- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

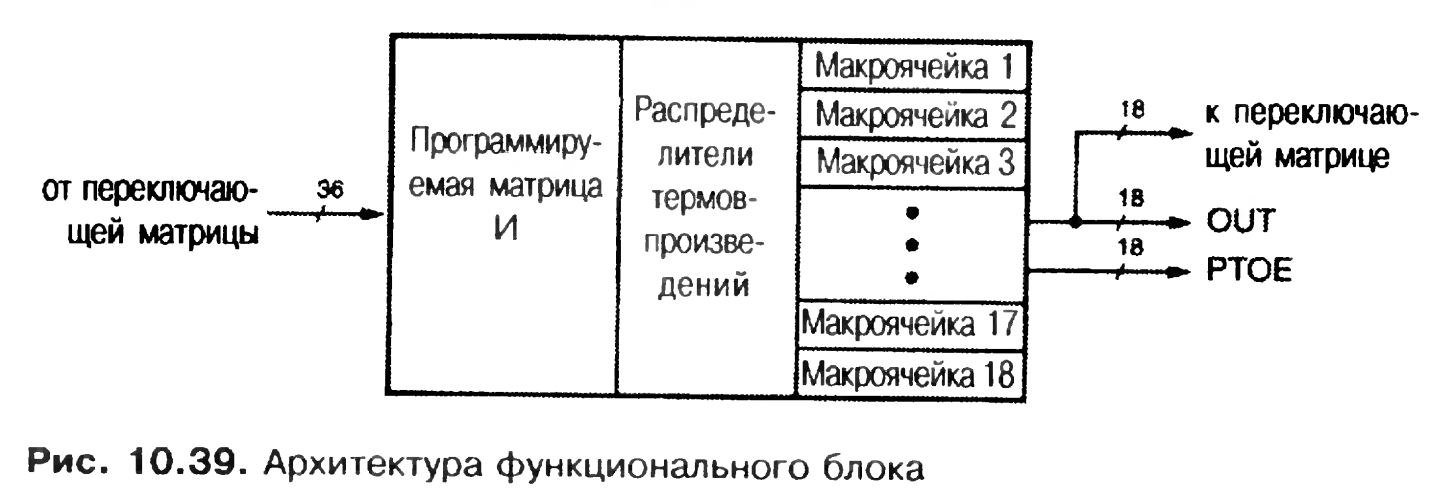

30. Архитектура функционального блока

Архитектура функционального блока семейства ХС9500 приведена на рис. 10.39. В программируемой матрице И имеется только 90 термов-произведений. По сравнению с такими ПЛУ как 16V8 и 22V10 у ИС типа ХС9500 и у большинства других ИС типа CPLD на одну макроячейку приходится меньшее число И-термов: у ИС ХС9500 их всего лишь 5, в то время как у микросхемы 16V8 - 8, а у микросхемы 22V10 - от 8 до 16. Однако все не так плохо благодаря возможности распределения термов-произведений {product-term allocation). У микросхем серии ХС9500, как и у других ИС типа CPLD, имеются распределители термов-произведений (product-term allocators), поэтому термы-произведения, не востребованные в одной макроячейке, можно использовать в других, соседних макроячейках того же функционального блока.

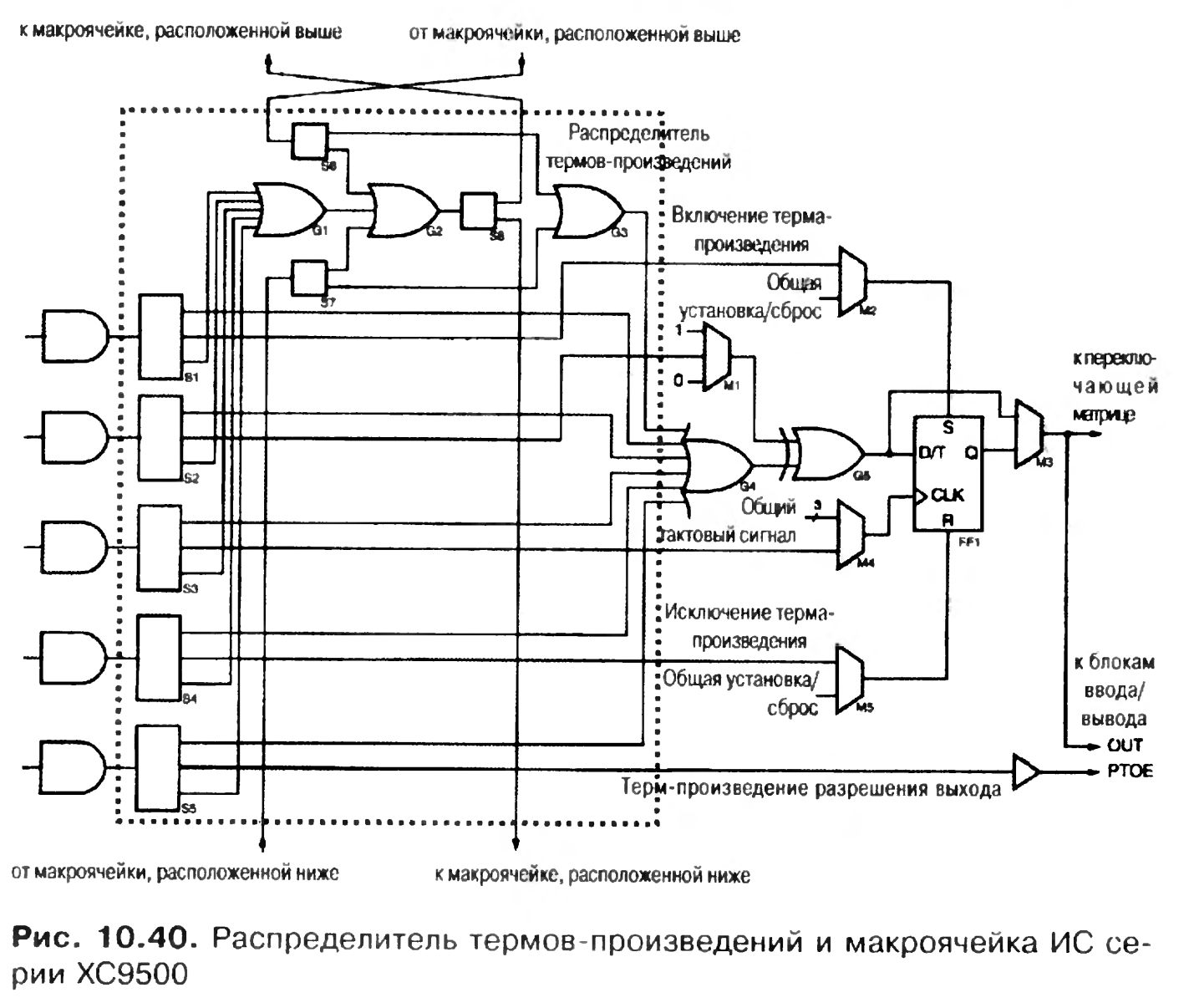

На рис. 10.40 представлена принципиальная схема распределителя термов-произведений и макроячейки ИС серии ХС9500. На этом рисунке прямоугольниками с именами S1-S8 обозначены программируемые элементы, посредством которых сигналы, действующие на их входах, направляются на один из имеющихся у них выходов. Трапециевидные символы, обозначенные М1-М5, представляют собой программируемые мультиплексоры, которые подключают один из двух или четырех имеющихся у них входов к своему выходу.

В левой части рисунка изображены 5 вентилей И, относящихся к данной макроячейке. Выходы каждого из них соединены с входами элементов, осуществляющих направление сигнала по тому или иному пути. С верхних выходов этих элементов термы-произведения поступают на вентиль G4 - главный вентиль ИЛИ данной макроячейки. Из сказанного можно заключить, что данной макроячейке доступны всего лишь пять термов-произведений. Однако верхний, шестой вход вентиля G4 соединен с выходом другого вентиля ИЛИ (G3), на который поступают термы-произведения от макроячеек, расположенных выше и ниже данной макроячейки.

Любые не используемые в данной макроячейке термы-произведения можно с помощью направляющих узлов S1-S5 подать на входы объединяющего вентиля ИЛИ (G1), сигнал с выхода которого через элемент S8, в конце концов, может быть отправлен в макроячейку, расположенную выше, или в макроячейку, расположенную ниже. Перед направлением в другую макроячейку эти термы-произведения можно с помощью элементов S6, S7 и G2 объединить с термами-произведениями макроячеек, расположенных выше или ниже данной макроячейки. Таким образом, возможно «гирляндное подключение» термов-произведений через следующие одна за другой макроячейки для образования суммы, состоящей из большего числа произведений. В принципе, можно объединить и направить в одну макроячейку все 90 термов-произведений, имеющихся в данном функциональном блоке, хотя при этом 17 из 18 макроячеек этого функционального блока останутся вообще без термов-произведений.

Третий вариант, когда сигнал появляется на среднем выходе какого либо из элементов S1-S5, служит для использования терма-произведения в качестве «специальной функции». Специальные функции - это подача сигнала на тактовый вход триггера, установка его в единичное состояние и сброс, а также управление вентилем ИСКЛЮЧАЮЩЕЕ ИЛИ и разрешение выхода. Обычно большинство этих специальных функций не используется.

Сердцевину макроячейки образует вентиль ИЛИ G4, на выходе которого возникает сумма всех выбранных термов-произведений, и вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ G5, на один из входов которого подается эта сумма произведений. Сигнал на другом входе вентиля G5 может быть равен 0 или 1, а также может быть термом-произведением в зависимости от того, что выбрано мультиплексором М1. При установке на этом входе вентиля G5 единицы, сумма произведений, поступающая с выхода вентиля G4, инвертируется, поэтому макроячейку можно сконфигурировать так, чтобы получить минимизированные логические выражения любой полярности. Подача на этот вход терма-произведения полезна при построении счетчиков. Если терм-произведение принимает значение I в том случае, когда биты младших разрядов счетчика равны 1 и счет разрешен, а сигнал на выходе вентиля G4 выражает собой текущее значение бита в данном разряде счетчика, то бит в данном разряде счетчика инвертируется, как и должно происходить в счетчике.

Триггер макроячейки FF1 можно запрограммировать для работы в качестве D- триггера или в качестве Т-триггера с входом разрешения счета; последний вариант полезен при реализации счетчиков того или иного типа. С помощью мультиплексора М4 выбирается сигнал, подаваемый на тактовый вход триггера; этим сигналом может быть один из четырех входных сигналов мультиплексора: один из трех общих тактовых сигналов на входах ИС или терм-произведение. На выбор последнего сигнала в синхронных проектах наложен запрет, за исключением тщательно проработанных синхронизирующих устройств типа схемы, приведенной на рис. 8.111.

У триггера есть также входы асинхронной установки в единичное состояние и сброса. Выбор сигналов, подаваемых на эти входы, осуществляется мультиплексорами М2 и М5. В большинстве случаев входы установки и сброса бывают соединены с общим входом установка/сброс данной ИС и используются только при начальном запуске системы. Однако по этим входам можно также получить доступ к SR-защелке, у которой вход CLK не используется.

В качестве выходного сигнала макроячейки OUT с помощью еще одного мультиплексора М3 выбирается сигнал с выхода триггера или сигнал, поступающий на его вход данных. Выходной сигнал OUT поступает на переключающую матрицу, где он может быть использован любой другой макроячейкой. Он может быть отправлен также к блокам ввода/вывода вместе с термом-произведением, выбранным элементом S5, который при необходимости, можно использовать как сигнал разрешения выхода РТОЕ.