- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

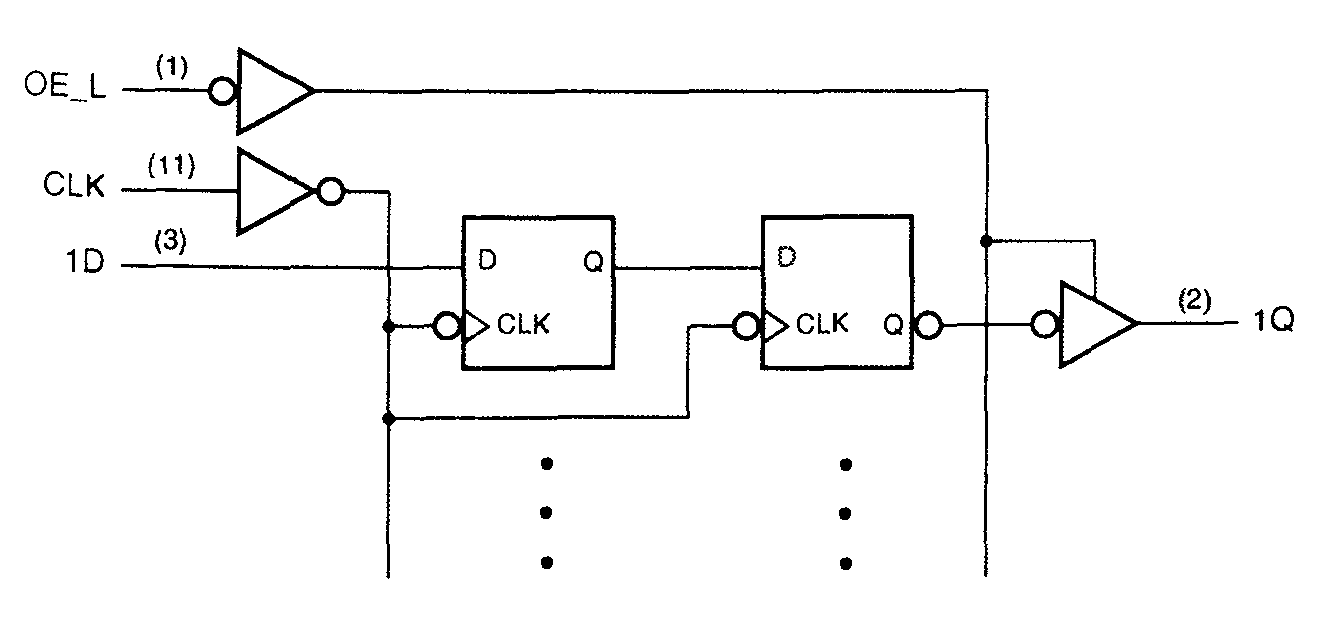

26. Триггеры с защитой от метастабильности

В конце 80-х годов фирма Texas Instruments и другие производители приступили к выпуску ИС малой и средней степени интеграции с триггерами, специально предназначенными для использования в синхронизирующих устройствах, встраиваемых в систему на уровне печатных плат. Микросхема 74AS4374 была, например, подобна ИС 74AS374, но с тем отличием, что отдельные триггеры заменены парами триггеров, включенных по схеме, представленной на рис. 1.

Внутренняя структура ИС 'AS4374 была усовершенствована таким образом, чтобы уменьшить значения т и Tо по сравнению с другими триггерами серии 74 AS, но самым замечательным достижением было значительное сокращение времени установления tsetup. Поскольку вся схема синхронизирующего устройства в данном случае размещается в одном кристалле, между триггерами FF1 и FF2 нет входных и выходных буферов, и значение tsetup для триггера FF2 составляет всего 0.5 нc. У обычного триггера серии 74AS эта величина равняется 5 нc, поэтому - при т = 0.40 нc - переход на ИС 74AS4374 приводит к увеличению среднего времени между сбоями MTBF в 77000 раз.

В последние годы по мере движения в сторону КМОП-технологий, обеспечивающих большее быстродействие и большую плотность упаковки, специализированные компоненты типа 'AS4374 почти полностью вышли из употребления. Быстродействующие ПЛУ и ИС типа CPLD вполне конкурентоспособны по величине т с самыми быстродействующими устройствами, собранными на отдельных ИС, и в то же время предоставляют возможность объединить синхронизацию со многими другими функциями.

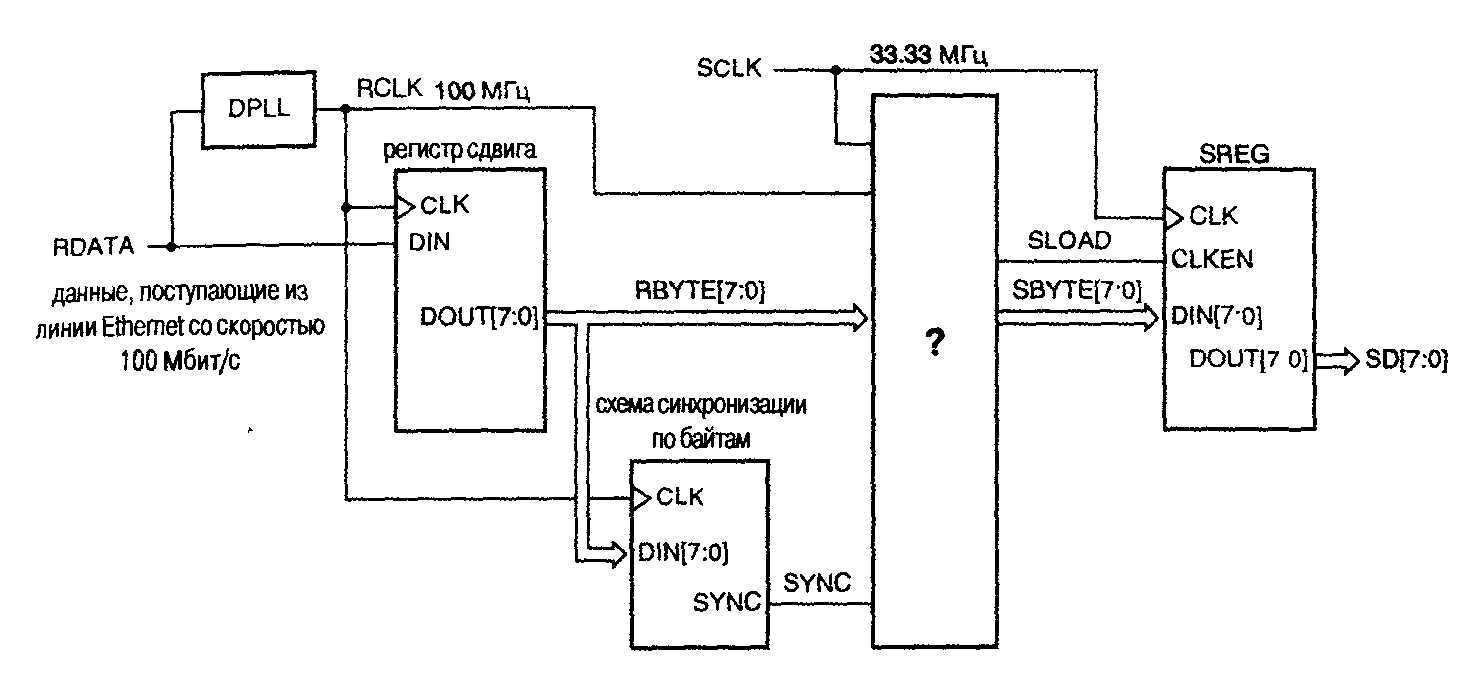

27. Синхронизация при высокоскоростной передаче данных

Широко распространенной проблемой, возникающей в компьютерных системах, является синхронизация переноса данных, поступающих по внешним линиям, с внутренним тактовым сигналом компьютера.

Эта проблема схематически представлена на рис. 1. Последовательные данные RDATA, представленные в коде NRZ, принимаются по линии Ethernet со скоростью 100Мбит/с. Цифровая схема ФАПЧ (Digital Phase-Locked Loop, DPLL) извлекает 100-мегагерцный тактовый сигнал RCLK из потока данных, поступающих со скоростью 100 Мбит/с, и позволяет заталкивать данные побитно в 8-разрядный регистр сдвига. В то же самое время схема синхронизации по байтам ищет в принимаемом потоке данных последовательность битов специального вида, которой отмечаются границы между байтами. Обнаруживая одну из них, схема синхронизации по байтам выдает сигнал SYNC и поступает так на каждом восьмом такте сигнала RCLK; таким образом, сигнал SYNC возникает всякий раз, когда регистр сдвига содержит выровненный по границам 8-битовый байт принимаемых данных. В остальной части системы тактирование осуществляется тактовым сигналом SCLK с частотой 33.33 МГц. Нам необходимо переносить каждый выровненный по границам байт RBYTE[7:0] в регистр SREG, находящийся в той части системы, которая работает с тактовым сигналом SCLK.

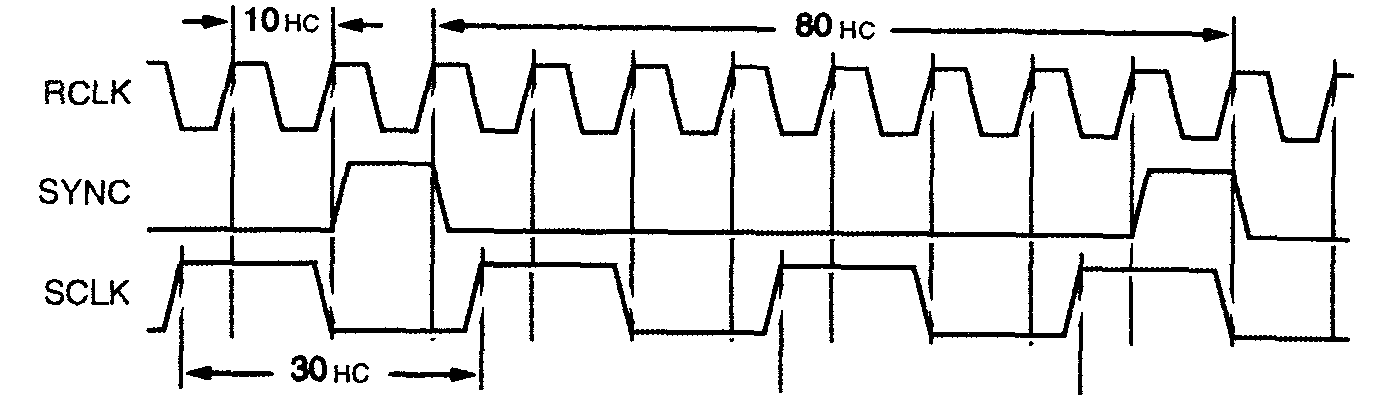

На рис. 2 приведены несколько временных диаграмм. Сразу видно, что сигнал выравнивания байтов по границам SYNC имеет активный уровень только в течение 10 нс в пределах байта. Нет никакой надежды, что удастся каждый раз привязывать этот сигнал к системному тактовому сигналу SCLK, период которого, равный 30 нс, много больше.

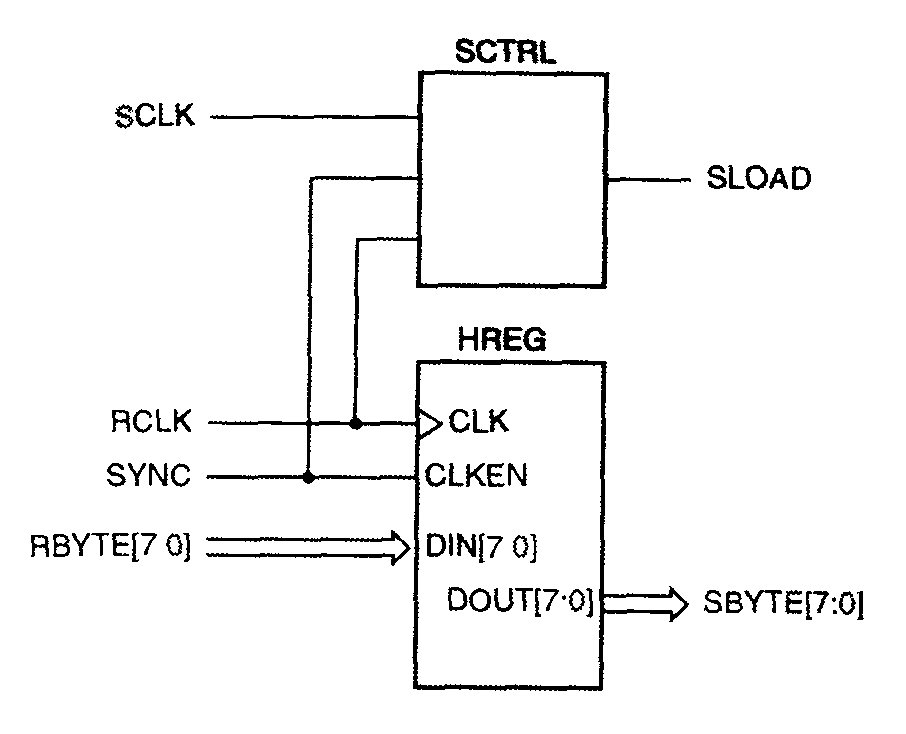

Стратегия,

которой следуют практически всегда в

ситуации подобного рода, состоит в том,

что сначала выровненные по границам

данные заносят в регистр хранения HREG

по

тактовому сигналу RCLK

из

принимаемого потока данных. Это

дает нам значительно больше времени, в

данном случае - 80 нс, чтобы разобраться

с принятым байтом. Таким образом, блок,

помеченный вопросительным знаком

"?" на рис. 1, можно заменить схемой,

показанной на рис. 3, состоящей из регистра

HREG

и

узла, названного "SCTRL".

Функция

этого узла заключается в вырабатывании

сигнала SLOAD

в

течение точно одного периода системного

тактового сигнала SCLK,

равного

30 нс, так, чтобы сигналы на выходах

регистра HREG

на

этом интервале оставались постоянными

и тем самым было удовлетворено требование

неизменности сигнала в течение времени

установления и времени удержания

регистра SREG,

переключающегося

по сигналу SCLK.

Стратегия,

которой следуют практически всегда в

ситуации подобного рода, состоит в том,

что сначала выровненные по границам

данные заносят в регистр хранения HREG

по

тактовому сигналу RCLK

из

принимаемого потока данных. Это

дает нам значительно больше времени, в

данном случае - 80 нс, чтобы разобраться

с принятым байтом. Таким образом, блок,

помеченный вопросительным знаком

"?" на рис. 1, можно заменить схемой,

показанной на рис. 3, состоящей из регистра

HREG

и

узла, названного "SCTRL".

Функция

этого узла заключается в вырабатывании

сигнала SLOAD

в

течение точно одного периода системного

тактового сигнала SCLK,

равного

30 нс, так, чтобы сигналы на выходах

регистра HREG

на

этом интервале оставались постоянными

и тем самым было удовлетворено требование

неизменности сигнала в течение времени

установления и времени удержания

регистра SREG,

переключающегося

по сигналу SCLK.

Рис

3.

Рис

3.

Правила, которые могут помочь при конструировании синхронизирующих устройств:

Минимизируйте число подсистем, работающих с различными тактовыми сигналами.

Четко определите границы между всеми тактовыми сигналам и и в явном виде поместите на этих границах синхронизирующие устройства.

Обеспечьте для каждого синхронизирующего устройства достаточное время выхода из метастабильности, чтобы сбои синхронизирующих устройств были редкими и происходили с много меньшей вероятностью, чем возникновение неисправности в других местах.

Проанализируйте работу синхронизирующего устройства при различных возможных сдвигах сигналов во времени, в том числе при более быстрых и более медленных тактовых сигналах, которые могут подаваться на схему при моделировании или при модернизации системы.

Осуществите моделирование работы системы в широком диапазоне возможных временных соотношений между сигналами.