- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

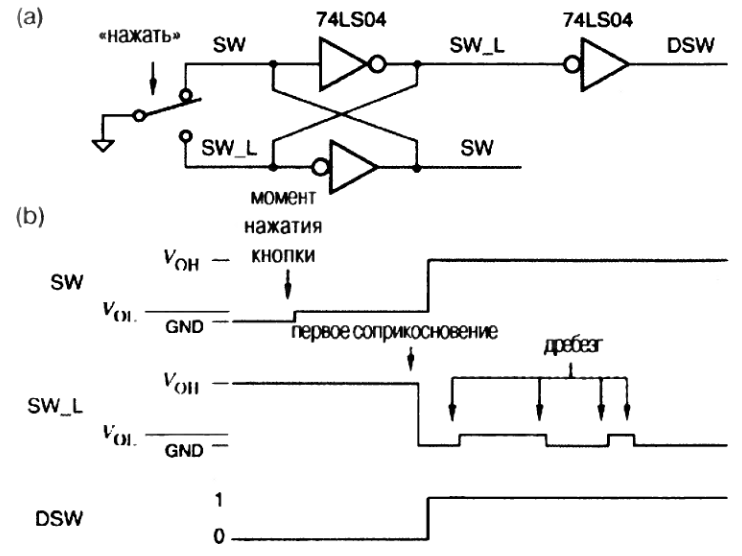

5. Простейшая схема защиты от дребезга

Защита от дребезга является хорошим примером применения простейшего пос- ледовательностного устройства — элемента с двумя устойчивыми состояниями . Им можно воспользоваться так, как показано на рис. 8.5. В этой схеме применяется однополюсный переключатель на два на- правления, устроенный таким образом, что при переключении подвижный кон- такт сначала размыкается с одним из неподвижных контактов и только потом за- мыкается на другой неподвижный контакт. Поэтому в процессе переключения подвижный контакт в течение некоторого времени пребывает в «плавающей» со- стоянии, где-то посередине между неподвижными контактами.

До нажатия кнопки на верхний неподвижный контакт подается 0 В, поэтому логическое значение сигнала SW равно 0, а на выходе верхнего инвертора удержи- вается сигнал с логическим значением 1, которым определяется потенциал SW_L нижнего неподвижного контакта. Когда кнопка нажимается и соединение между подвижным и верхним неподвижным контактом разрывается, петля обратной свя- зи в элементе с двумя устойчивыми состояниями удерживает значение SW на уров- не VOL(= 0.5 В для TTJI-схем серии LS), что, попрежнему соответствует логичес- кому 0.

Затем, когда подвижный контакт впервые касается нижнего неподвижного кон- такта, схема некоторое время ведет себя самым необычным образом. Верхний инвертор элемента с двумя устойчивыми состояниями пытается удерживать логи- ческую 1 на сигнальной линии SW_L, при этом верхний транзистор в его выходной цепи открыт и поэтому точка SW_L через малое сопротивление соединена с ши- ной питания +5 В. А тут вдруг нижний неподвижный контакт механически соеди- няется с землей, заставляя потенциал SW_L стать равным 0.0 В. Ничего удивитель- ного, что механическое воздействие побеждает.

Спустя короткое время (30 нс для ИС 74LS04) логический 0, механически удер- живаемый на линии SW_L, проходит через два инвертора, образующие элемент с двумя устойчивыми состояниями, так что верхний инвертор отказывается от тщет- ных усилий по поддержанию на линии SW_L логической 1, а вместо нее выдает логический 0. Но теперь нет больше необходимости в замыкании выхода верхнего инвертора на землю: петля обратной связи в элементе с двумя устойчивыми со- стояниями удерживает логический 0 на линии SW_L даже в том случае, когда под- вижный контакт отскакивает от нижнего неподвижного контакта. (Он отскакивает не очень далеко и не касается снова верхнего неподвижного контакта.)

Достоинство этой схемы по сравнению с другими вариантами защиты от дре- безга заключается в малом расходе ресурса по числу микросхем (одна треть ИС 74I S04), в отсутствии резисторов, подтягивающих входы вснтилей к шине питания, и в возможности получения входного сигнала любой полярности (с высоким или низким активным уровнем).

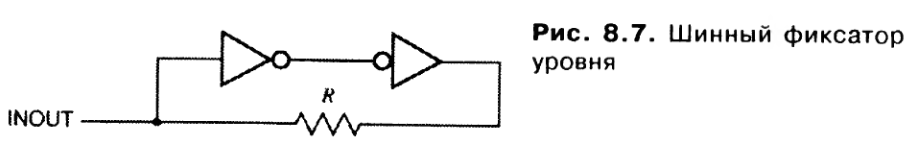

6. Шинный фиксатор уровня

В любой момент времени не более чем одна из схем выдает сигнал на шину; иногда ни одна из схем не является источником сигнала, и тогда шина оказывается в «плавающем» состоянии. Если к шине подключены входы быстродействующих КМОП-вентилей и шина оставлена в плавающем состоянии надолго, то могут происходить разные неприятности. В частности, из-за шумов перекрестных помех и других эффектов на высокоимпедансной шине, пребывающей в плавающем со- стоянии, может возникнуть напряжение, близкое к порогу переключения КМОП- -схем по входу, что, в свою очередь, приведет к протеканию чрезмерно больших токов по выходным цепям этих схем. По этой причине желательно соединять шины резисторами с источником питания, чтобы при их переходе в плавающее состоя- ние на них быстро устанавливался логический сигнал высокого уровня. Так обыч- но и поступают.

Но резисторы, подтягивающие потенциал шины к напряжению питания, - не такое уж хорошее решение: они стоят денег и занимают ценное «жизненное пространство» на печатной плате. В случае сверхбыстродействующих схем трудной задачей является выбор сопротивления этих резисторов. Если сопротивление слиш- ком велико и шина переходит в третье cocтояние с низкого уровня спгнала, то изменение потенциала шины от низкого уровня до высокого происходит медленно из-за большой постоянной времени RC, и напряжение на подключенных к шине входах слишком долго остается вблизи порога переключения. Если сопротивление резистора, подтягивающего шину к источнику питания, слишком мало, то схемы, которым предстоит выдавать на шину сигнал низкого уровня, должны будут до- пускать втекание в них со стороны выхода слишком большого тока.

Решение этой проблемы состоит в исключении резистора, подтягивающего шину к источнику питания, и замене его активным шинным фиксатором уровня (Bus holder circuit), показанным на рис. 8.7. В этой схеме нет ничего нового: это — элемент с двумя устойчивыми состояниями с резистором R в одной из ветвей петли обратной связи. Вывод INOUT данной схемы соединяется с сигнальной линией шины с тремя состояниями, уровень которой эта схема должна будет удержи- вать. Когда схема, выдававшая на шину сигнал низкого или высокого уровня, запи- рается и ее выход переходит в третье состояние, правый инвертор фиксатора уров- ня удерживает сигнальную линию в ее прежнем состоянии. При изменении сигнала, выдаваемого на линию, с низкого уровня на высокий или в обратном направлении схема, служащая источником этого сигнала, должна допускать вытекание или вте- кание со стороны ее выхода небольшого дополнительного тока, протекающего по резистору R, чтобы преодолеть действие фиксатора уровня. Этот дополнительный ток течет лишь короткое время, которое необходимо элементу с двумя устойчивы- ми состояниями, чтобы переключиться из одного состояния в другое.

Сопротивление резистора R выбирается из соображений компромисса между малым током, затрачиваемым на преодоление действия фиксатора уровня (боль- шое значение R), и хорошей помехоустойчивостью удержания шины в текущем состоянии (малое значение R). Приведем типичный пример: в случае 3.3-вольто- вых КМОП-схем семейства LVC максимальное значение тока, который может быть затрачен на преодоление действия фиксатора уровня, равно 500 мкА; поэтому R = 3.3/0.0005 = 6.6 кОм.

Шинные фиксаторы уровня часто бывают встроены в такие ИС средней сте- пени интеграции, как 8-разрядный шинный КМОП-буфер или приемопередатчик. Для шинных фиксаторов уровня не требуется дополнительных выводов, и они занимают очень мало места на поверхности кристалла, так что их можно иметь, по существу, бесплатно. Нет никакой проблемы в том, чтобы к одной и той же линии были подключены несколько (n) фиксаторов уровня при условии, что схемы, слу- жащие источниками сигналов, выдаваемых на шину, допускают протекание по их выходным цепям в течение нескольких наносекунд (при переключении) n-кратно- го тока, затрачиваемого на преодоление действия всех фиксаторов уровня. За- метьте, что в случае, когда к шине подключены ТТЛ-входы, применение шинных фиксаторов уровня, как правило, не рационально.