- •1. Частотно-временное представление сигналов

- •2. Спектр прямоугольного импульса

- •3. Спектры модулированных колебаний

- •4. Числовые последовательности, основные операции преобразования.

- •Определение

- •Примеры

- •Операции над последовательностями

- •Подпоследовательности

- •Примеры

- •Свойства

- •Предельная точка последовательности

- •Предел последовательности

- •Некоторые виды последовательностей

- •Ограниченные и неограниченные последовательности

- •5. Типы цифровых фильтров, ких-фильтры.

- •Динамические характеристики

- •Свойства

- •Прямая форма ких фильтра

- •6. Типы цифровых фильтров, бих-фильтры.

- •Описание Динамические характеристики

- •Устойчивость

- •Реализация бих фильтра

- •7. Параллельные ацп.

- •8. Ацп последовательного счёта.

- •9. Ацп последовательного приближения. Типы ацп

- •10. Ацп многотактного интегрирования.

- •11. Сигма-дельта ацп.

- •Применение

- •Форматы хранения аудио

- •12. Преобразователи напряжение-частота.

- •Несинхронизируемые пнч

- •Синхронизируемые пнч

- •13. Метрологические характеристики ацп.

- •14. Цап с широтно импульсной модуляцией.

- •18. Интерфейсы ацп

- •19. Вольтметры с времяимпульсным преобразованием

- •21. Цифровой метод измерения частоты.

- •22. Цифровой метод измерения интервалов времени.

- •23. Цифровой измерительный генератор.

- •24. Цифровой измеритель параметров r, c, l (иммитанса).

- •Измеряемые величины

- •Устройство и принцип действия

- •Некоторые примеры

- •Основные нормируемые характеристики

- •25. Цифровой измеритель фазового сдвига.

- •26. Микропроцессорный фазометр.

- •27. Анализаторы спектра, основанные на алгоритмах дискретного преобразования Фурье.

- •28. Анализаторы спектра, основанные на алгоритме быстрого преобразования Фурье.

- •Классификация анализаторов спектра

- •Основные свойства анализа

- •Низкочастотные и радиочастотные анализаторы спектра Низкочастотные анализаторы

- •Радиочастотные анализаторы

- •Анализаторы последовательного типа

- •Анализаторы параллельного типа

- •Цифровые анализаторы

- •Основные нормируемые характеристики

- •Оптические анализаторы спектра Принцип действия

- •Применение

- •Основные нормируемые характеристики

- •Основной алгоритм

- •Обратное преобразование Фурье

- •Общий случай

- •Вывод преобразования из дпф

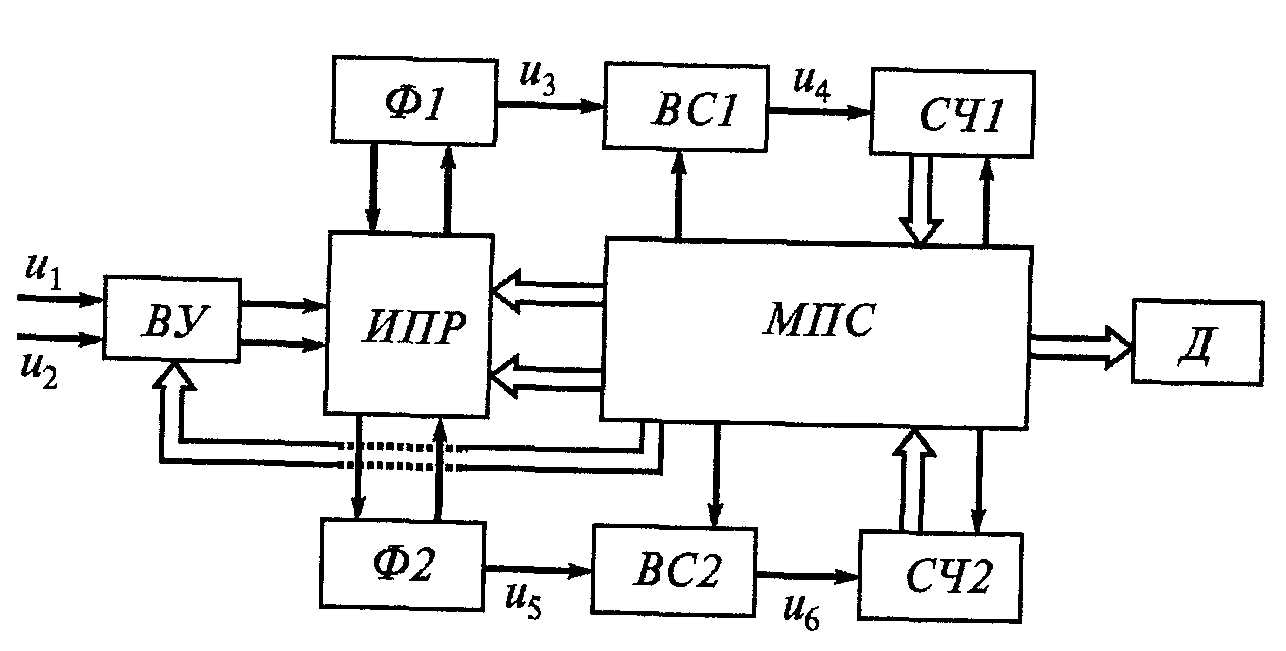

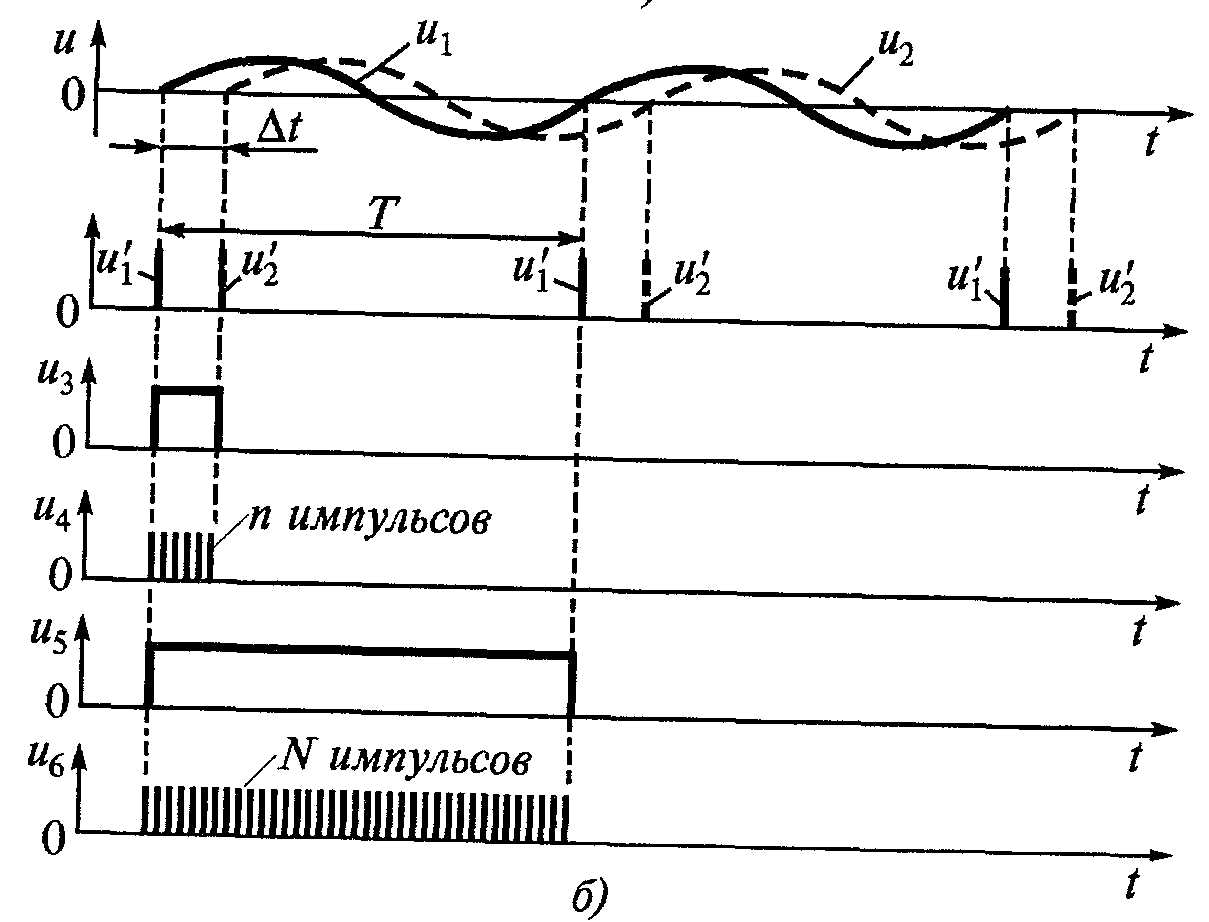

26. Микропроцессорный фазометр.

Значительное расширение функциональных возможностей, повышение надежности и некоторых других характеристик фазометров обеспечиваются при их построении на основе микропроцессора, работающего совместно с измерительными преобразователями. Такие фазометры позволяют измерять фазовый сдвиг между двумя периодическими сигналами за любой выбранный период, наблюдать флюктуации подобных сдвигов и оценивать их статистические характеристики: математическое ожидание, дисперсию, среднее квадратическое отклонение. Возможно также, как и в рассмотренных выше цифровых фазометрах, выполненных по схемам с жесткой логикой работы, измерение среднего значения фазового сдвига.

С труктурная

схема микропроцессорного фазометра

. Принцип измерения фазового сдвига

между двумя синусоидальными сигналами

u1 и u2

за один выбранный период Т их следования

поясняется временными диаграммами.

труктурная

схема микропроцессорного фазометра

. Принцип измерения фазового сдвига

между двумя синусоидальными сигналами

u1 и u2

за один выбранный период Т их следования

поясняется временными диаграммами.

В фазометре в схеме импульсного

преобразователя (ИПР) сигналы u1

и u2 преобразуются

в короткие импульсы

фазометре в схеме импульсного

преобразователя (ИПР) сигналы u1

и u2 преобразуются

в короткие импульсы

![]() и

и

![]() ,

соответственно. Формирователь Ф1 с

помощью первой пары данных импульсов

вырабатывает импульс u3

длительностью ∆t, равной сдвигу во

времени сигналов u1

и u2. Импульсом u3

открывается временной селектор (ВС1),

который в течение времени ∆t пропускает

на вход счетчика (СЧ1) счетные импульсы,

следующие с периодом То и вырабатываемые

микропроцессорной системой (МПС).

Поступающий на вход СЧ1 пакет импульсов

обозначен u4. Число

импульсов в пакете

,

соответственно. Формирователь Ф1 с

помощью первой пары данных импульсов

вырабатывает импульс u3

длительностью ∆t, равной сдвигу во

времени сигналов u1

и u2. Импульсом u3

открывается временной селектор (ВС1),

который в течение времени ∆t пропускает

на вход счетчика (СЧ1) счетные импульсы,

следующие с периодом То и вырабатываемые

микропроцессорной системой (МПС).

Поступающий на вход СЧ1 пакет импульсов

обозначен u4. Число

импульсов в пакете

![]() (5)

(5)

Одновременно формирователь Ф2 вырабатывает импульс u5, длительность которого равна периоду Т исследуемых сигналов u1 и u2. Импульс u5 открывает на время Т временной селектор ВС2, пропускающий от МПС на вход счетчика СЧ2 пакет импульсов u6. Период импульсов в пакете То, а их число

![]() (6)

(6)

Для оценки искомого значения фазового сдвига Дф за выбранный период Т требуется найти отношение величин (5) и (6), равное n/N = ∆t/T, a затем, домножить это отношение на 360°:

![]() (7)

(7)

Вычисление выражения (7) выполняется МПС, на которую передаются вырабатываемые счетчиками СЧ1 и СЧ2 коды чисел n и N. При соответствующей программе МПС на дисплее Д отображается значение фазового сдвига ∆φ для любого выбранного периода Т. За счет сравнения таких сдвигов в разных периодах появляется возможность наблюдать флюктуации ∆φ и оценивать их статистические параметры.

В режиме оценки фазометром среднего значения фазового сдвига ∆φ за заданное число r периодов T в счетчиках СЧ1 и СЧ2 происходит накопление кодов от числа импульсов, поступивших на их входы за r периодов, т.е. кодов чисел nr и Nr соответственно, которые затем передаются в МПС.

Данным фазометром, как и ранее рассмотренными, малую погрешность измерения ∆φ можно получить только на достаточно низкой частоте исследуемых сигналов. Поэтому для расширения частотного диапазона фазометров используется предварительное гетеродинное преобразование сигналов.

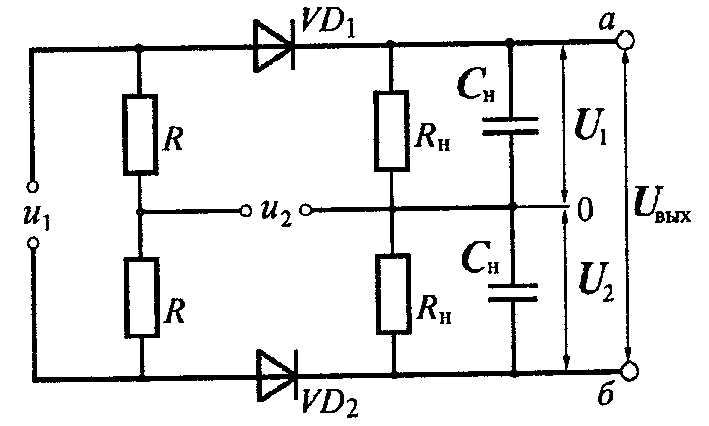

Измерение фазового сдвига фазовыми детекторами

Ф азовый

сдвиг между двумя гармоническими

сигналами одной частоты можно измерить

фазовым детектором. Одна из схем

фазового детектора приведена на рисунке.

Сигналы u1 и u2

между которыми измеряют фазовый

сдвиг φ, преобразуют фазовым детектором

в постоянное напряжение. На выходе его

включают вольтметр (ЦФ), измеряющий

постоянную составляющую напряжения

между точками а и б, которое равно

разности продетектированных напряжений

U1 и U2. Если амплитуды

исследуемых напряжений поддерживать

постоянными, шкалу вольтметра можно

проградуировать непосредственно в

значениях фазового угла. С помощью

фазового детектора получают погрешность

измерений около (2...3)о. Погрешность

зависит от выполнения условий,

накладываемых на параметры схемы и

амплитуды исследуемых напряжений, от

стабильности этих величин во времени,

чувствительности вольтметра и т. д.

азовый

сдвиг между двумя гармоническими

сигналами одной частоты можно измерить

фазовым детектором. Одна из схем

фазового детектора приведена на рисунке.

Сигналы u1 и u2

между которыми измеряют фазовый

сдвиг φ, преобразуют фазовым детектором

в постоянное напряжение. На выходе его

включают вольтметр (ЦФ), измеряющий

постоянную составляющую напряжения

между точками а и б, которое равно

разности продетектированных напряжений

U1 и U2. Если амплитуды

исследуемых напряжений поддерживать

постоянными, шкалу вольтметра можно

проградуировать непосредственно в

значениях фазового угла. С помощью

фазового детектора получают погрешность

измерений около (2...3)о. Погрешность

зависит от выполнения условий,

накладываемых на параметры схемы и

амплитуды исследуемых напряжений, от

стабильности этих величин во времени,

чувствительности вольтметра и т. д.

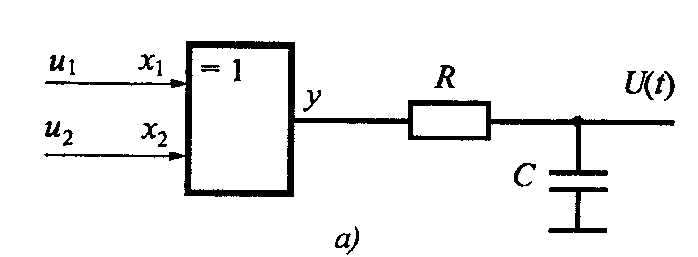

Ц ифровые

фазовые детекторы могут быть построены

на цифровых логических схемах: элементе

«Исключающее ИЛИ», JK-триггере

и пр. При этом достаточно просто удается

получить длительность выходных

импульсов, пропорциональную фазовому

сдвигу между сигналами u1

и u2, после чего

сгладить эти импульсы в ФНЧ. В качестве

примера приведем схему цифрового

фазового детектора на элементе

«Исключающее ИЛИ» (сумматор по модулю

два).

ифровые

фазовые детекторы могут быть построены

на цифровых логических схемах: элементе

«Исключающее ИЛИ», JK-триггере

и пр. При этом достаточно просто удается

получить длительность выходных

импульсов, пропорциональную фазовому

сдвигу между сигналами u1

и u2, после чего

сгладить эти импульсы в ФНЧ. В качестве

примера приведем схему цифрового

фазового детектора на элементе

«Исключающее ИЛИ» (сумматор по модулю

два).

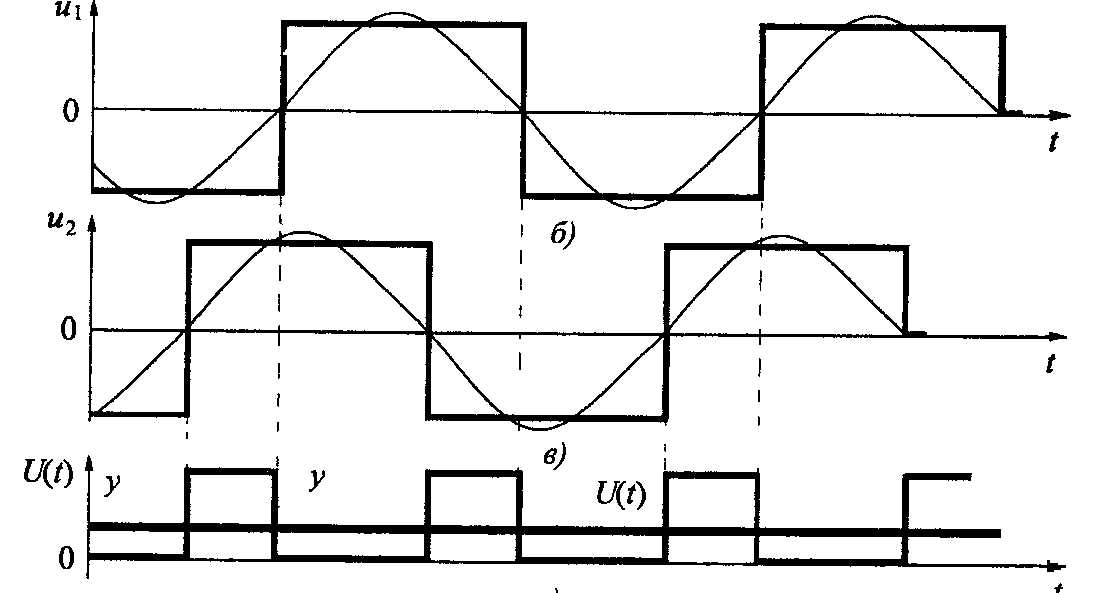

Временные диаграммы работы схемы показаны на рис. б - г. В этом детекторе из исследуемых синусоид u1 и u2 формируются соответствующие напряжения типа «меандр». На выходе логического элемента вырабатываются импульсы напряжения у, длительность которых пропорциональна фазовому сдвигу входных сигналов г). Далее этот сигнал подается на ФНЧ. Напряжение U(t) на выходе ФНЧ пропорционально сдвигу сигнала u1 относительно опорного u2.