- •1. Электропроводность п/п.

- •3. Прямое и обратное смещение p-n перехода.

- •4. Вольтамперная характеристика.

- •5. Основные параметры p-n перехода.

- •6. Пробой p-n перехода.

- •7. Методы изготовления p-n перехода.

- •8. Выпрямительный диод.

- •9. Стабилитрон.

- •10. Варикап.

- •11. Туннельный диод. Обращенный диод.

- •12. Контакт металл-п/п. Диод Шоттки.

- •13. Классификация транзисторов.

- •14. Устройство транзистора.

- •15. Принцип действия транзистора.

- •1 6. Токи в транзисторе.

- •17. Модуляция базы.

- •18. Схема включения транзистора с об, оэ и ок.

- •19. Основные параметры транзисторов: а) физические; б) h-параметры.

- •20. Основные характеристики транзисторов, таблица основных параметров.

- •21. Характеристики с оэ (входные, выходные, прямой передачи тока).

- •22. Униполярные транзисторы с управляющим p-n переходом.

- •23. Униполярные транзисторы с изолированным затвором.

- •24. Тиристор, Динистор.

- •25. Однопереходный транзистор.

- •26. Светодиод.

- •27. Фотодиод, вах.

- •28. Оптроны.

- •29. Особенности упт: причины дрейфа и способы его уменьшения.

- •30(31). Дифф. Усилитель. Режимы работы ду.

- •32. Дифф. Усилитель с гст.

- •3 3. Дифф. Усилитель с динам. Нагрузкой (с зеркалом токов).

- •34. Операц. Усилитель. Общие сведения.

- •35. Операц. Усилитель. Основные параметры.

- •36. Операц. Усилитель, структ. И принцип. Схемы.

- •37. Операц. Усилитель, внешние цепи.

- •38. Операц. Усилитель с отриц. Обратной связью.

- •39. Инвертирующий усилитель.

- •40. Неинвертирующий усилитель.

- •46. Триггер Шмидта.

- •47(48). Генераторы сигналов. Rc-генератор синусоид. Колебаний.

- •49. Мультивибратор.

- •5 0. Глин.

- •51. Основные логические операции и логические элементы.

- •54. Ттл с простым инвертором.

- •55. Ттл со сложным инвертором.

- •56(57). Эсл. Переключатель тока.

- •59(60). Схема не на мдп с (не)линейной нагрузкой.

- •61. Схема не на кмдп

- •62. Схема или-не на мдп и кмдп

- •63. Схема и-не на мдп и кмдп

- •64. Мультиплексор

- •65. Демультиплексор

- •66. Дешифратор

- •67. Шифратор

- •68. Триггеры классификация

- •69. Rs триггер

- •74. Регистр сдвига

- •75. Счетчики суммирующие.

- •76. Счетчики вычитающие.

- •77. Десятичный счетчик.

- •1. Электропроводность п/п

- •3. Прямое и обратное смещение p-n перехода

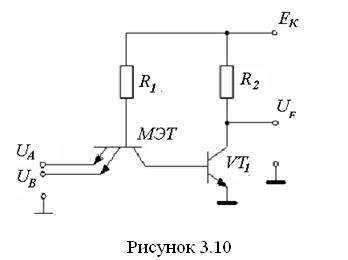

54. Ттл с простым инвертором.

Это

интегральный прибор, объединяющий

функции диодных логических схем и

транзисторного усилителя. МЭТ имеет

несколько эмиттеров, расположенных

так, что прямое взаимодействие между

ними исключается. Базовый элемент ТТЛ

так же, как и ДТЛ выполняет логическую

операцию И-НЕ. При низком уровне

сигнала (логический 0) хотя бы на одном

из входов МЭТ последний находится

в состоянии насыщения, а VT1

закрыт. На выходе схемы присутствует

высокий уровень напряжения (логическая

единица). При высоком уровне сигнала на

всех входах МЭТ работает в активном

инверсном режиме (эмиттерный переход

смещен в обратном направлении, а

коллекторный – в прямом), VT1

находится в состоянии насыщения. На

выходе схемы низкий уровень сигнала,

т.е. ноль.

Это

интегральный прибор, объединяющий

функции диодных логических схем и

транзисторного усилителя. МЭТ имеет

несколько эмиттеров, расположенных

так, что прямое взаимодействие между

ними исключается. Базовый элемент ТТЛ

так же, как и ДТЛ выполняет логическую

операцию И-НЕ. При низком уровне

сигнала (логический 0) хотя бы на одном

из входов МЭТ последний находится

в состоянии насыщения, а VT1

закрыт. На выходе схемы присутствует

высокий уровень напряжения (логическая

единица). При высоком уровне сигнала на

всех входах МЭТ работает в активном

инверсном режиме (эмиттерный переход

смещен в обратном направлении, а

коллекторный – в прямом), VT1

находится в состоянии насыщения. На

выходе схемы низкий уровень сигнала,

т.е. ноль.

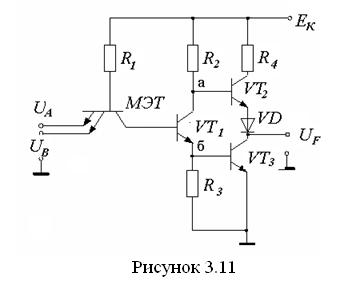

55. Ттл со сложным инвертором.

Е сли

хотя бы на одном из входов низкий уровень

напряжения U0ВХ

эмиттерный переход МЭТ отпирается

и течет ток: от +ЕК, через

R1, переход

база-эмиттер на землю. Коллекторный

переход МЭТ смещен в обратном

направлении (МЭТ в активном режиме).

Ток базы IБ1

= 0, следовательно, транзистор VT1

запирается. На коллекторе VT1

высокий уровень напряжения UК1

= ЕК. На эмиттере VT1

напряжение UЭ1

= 0. Транзистор VТ2

отпирается током через резистор R2.

Так как UБ3 =

UЭ1 = 0,

то транзистор VT3

заперт и UВЫХ=

U1ВЫХ.

Если же на всех входах ТТЛ высокий

уровень U1,

эмиттерные переходы МЭТ запираются,

потенциал базы увеличивается, коллекторный

переход МЭТ смещается в прямом

направлении. МЭТ работает в

активно-инверсном режиме. Транзисторы

VТ1 и

VТ3

открыты и насыщены. Транзистор VТ2

и диод VD заперты.

На выходе ТТЛ низкий уровень UВЫХ

= U0 = 0.

Следовательно, ТТЛ выполняет операцию

И-НЕ, т.е. является элементом Шеффера.

сли

хотя бы на одном из входов низкий уровень

напряжения U0ВХ

эмиттерный переход МЭТ отпирается

и течет ток: от +ЕК, через

R1, переход

база-эмиттер на землю. Коллекторный

переход МЭТ смещен в обратном

направлении (МЭТ в активном режиме).

Ток базы IБ1

= 0, следовательно, транзистор VT1

запирается. На коллекторе VT1

высокий уровень напряжения UК1

= ЕК. На эмиттере VT1

напряжение UЭ1

= 0. Транзистор VТ2

отпирается током через резистор R2.

Так как UБ3 =

UЭ1 = 0,

то транзистор VT3

заперт и UВЫХ=

U1ВЫХ.

Если же на всех входах ТТЛ высокий

уровень U1,

эмиттерные переходы МЭТ запираются,

потенциал базы увеличивается, коллекторный

переход МЭТ смещается в прямом

направлении. МЭТ работает в

активно-инверсном режиме. Транзисторы

VТ1 и

VТ3

открыты и насыщены. Транзистор VТ2

и диод VD заперты.

На выходе ТТЛ низкий уровень UВЫХ

= U0 = 0.

Следовательно, ТТЛ выполняет операцию

И-НЕ, т.е. является элементом Шеффера.

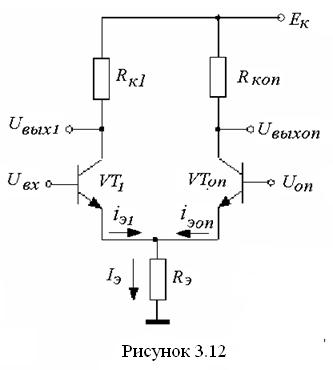

56(57). Эсл. Переключатель тока.

О собенность

ЭСЛ заключается в том, что схема

логического элемента строится на основе

интегрального ДУ в ключевом режиме

(токовый ключ), выполненный на двух

транзисторах, которые могут переключать

ток и при этом никогда не входят в режим

насыщения.

собенность

ЭСЛ заключается в том, что схема

логического элемента строится на основе

интегрального ДУ в ключевом режиме

(токовый ключ), выполненный на двух

транзисторах, которые могут переключать

ток и при этом никогда не входят в режим

насыщения.

На

базу одного из транзисторов, например,

VTоп, подано некоторое

постоянное опорное напряжение Uоп.

![]() .

Изменение напряжения, подаваемого на

вход UВХ

ниже или выше Uоп, приводит

к перераспределению постоянного тока

эмиттера Iэ, заданного токостабилизирующим

резистором Rэ, между транзисторами VT1

и VTоп. При

этом транзисторы не входят в режим

насыщения, и, следовательно, в ключе

принципиально отсутствует интервал

рассасывания их неосновных носителей.

.

Изменение напряжения, подаваемого на

вход UВХ

ниже или выше Uоп, приводит

к перераспределению постоянного тока

эмиттера Iэ, заданного токостабилизирующим

резистором Rэ, между транзисторами VT1

и VTоп. При

этом транзисторы не входят в режим

насыщения, и, следовательно, в ключе

принципиально отсутствует интервал

рассасывания их неосновных носителей.

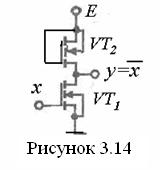

59(60). Схема не на мдп с (не)линейной нагрузкой.

С хема

инвертора на МДП. Транзистор VT1

работает в ключевом режиме, VT2

– всегда в активном. VT2

является нелинейной нагрузкой. При

запертом VT1

транзистор VT2

‑ в активном режиме, ближе к насыщению,

при насыщенном VT1

транзистор VT2

– в активном, ближе к отсечке. При

подаче на вход х низкого уровня

напряжения VT1

запирается, VT2

близок к насыщению, на выходе ключа

высокий уровень напряжения. При подаче

на вход х высокого уровня напряжения

VT1 отпирается,

VT2 близок к

отсечке, на выходе ключа низкий уровень

напряжения. Выполняется операция

хема

инвертора на МДП. Транзистор VT1

работает в ключевом режиме, VT2

– всегда в активном. VT2

является нелинейной нагрузкой. При

запертом VT1

транзистор VT2

‑ в активном режиме, ближе к насыщению,

при насыщенном VT1

транзистор VT2

– в активном, ближе к отсечке. При

подаче на вход х низкого уровня

напряжения VT1

запирается, VT2

близок к насыщению, на выходе ключа

высокий уровень напряжения. При подаче

на вход х высокого уровня напряжения

VT1 отпирается,

VT2 близок к

отсечке, на выходе ключа низкий уровень

напряжения. Выполняется операция

![]() ;

;