- •1.Классификация и характеристики мп.

- •Вопрос 2. Организация доступа к программно доступным элементам

- •Билет№2

- •1.Оценка производительности мп.

- •2.Программно-управляемый обмен.

- •1.Общая структура Фон-Неймановской архитектуры.

- •2.Обмен в режиме прерываний. Инициализация подсистемы прерывания.

- •Билет№4

- •1.Устройство управления мп.

- •2.Обмен в режиме прерываний. Алгоритм обмена.

- •Билет№5

- •1.Операционное устройство мп.

- •2.Обмен данными в режиме пдп. Инициализация.

- •1.Принцип конвейерной обработки. Производительность, проблемы.

- •2.Обмен данными в режиме пдп. Алгоритм обмена.

- •1.Структурные конфликты. Методы минимизации конфликтов.

- •2.Обмен в режиме прерываний. Алгоритм обмена.

- •1.Конфликты по данным. Методы минимизации конфликтов.

- •2.Организация доступа к программно-доступным элементам.

- •1.Конфликты по управлению. Статические методы минимизаций конфликтов.

- •2.Программно-управляемый обмен.

- •1.Конфликты по управлению. Динамические методы минимизаций конфликтов.

- •2.Суперскалярная обработка. Приминение. Проблемы.

- •1.Пути повышения производительности мп. Особенности высокоскростных мп.

- •2.Обмен в режиме прерываний. Инициализация подсистемы прерываний.

- •2.Операционное устройство мп.

- •1.Обмен данными в режиме пдп. Инициализация.

- •Аппаратный стек мп

- •1.Обмен данными в режиме пдп. Алгоритм обмена.

- •2.Оценка производительности мп.

- •1.Программно-управляемый обмен.

- •2.Организация доступа к программно-доступным элементам.

- •4, 8, 12, 16, 24, 32 И 64 разрядные мп

- •2.Обмен в режиме прерываний. Инициализация подсистемы прерывания.

- •Билет№18

- •1.Оценка производительности мп.

- •2.Обмен в режиме прерываний. Алгоритм обмена.

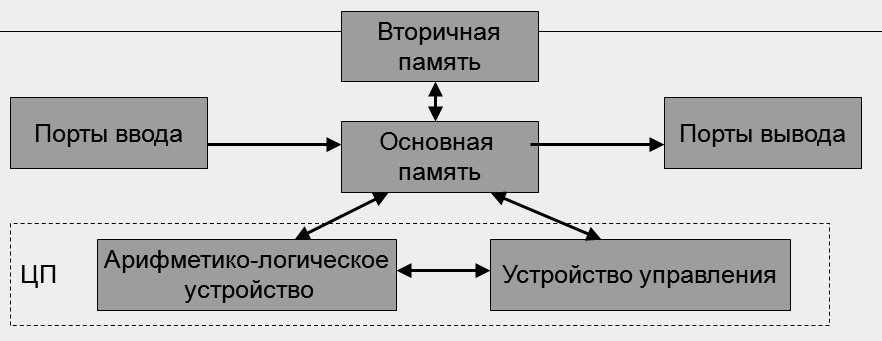

1.Общая структура Фон-Неймановской архитектуры.

Типичная фон-неймановская ВМ содержит: память, УУ, АЛУ и устройство вв/выв.

И поступает из подсоединенных к ЭВМ ПУ ввода. Результаты вычислений выводятся на ПУ вывода. Совокупность портов ввода и вывода, называют устройством ввода/вывода (УВВ) или модулем ввода/вывода ВМ (МВВ).

УУ—организует автом-е выполнение П, обеспечивает функц-е ВМ как единой С. УУ ВМ рассматривють как совокупность эл-в, м/у к-ми происходит пересылка И, к-я м подвергается обработке. Пересылка И инициируется своим сигналом управления (СУ). Оснфун-я УУ - формиров-е УпрСигн, отвечающих за извлечение команд из Пам в порядке, опр-м П, и исполн-е этих команд. УУ формирует СУ для синхронизации и координации внутр и внешних устройств ВМ.

АЛУ

- арифм и логич обработку двух входных

,

в результате формируется выходная ~.

Функции АЛУ обычно сводятся к простым

А и Л операциям, а также операциям

сдвига. Помимо результата операции АЛУ

формирует ряд признаков

результата (флагов),

хар-х результат и события, произошедшие

в процессе его получения (равенство

нулю, знак, четность, перенос, переполнение

и т. д.). Флаги могут анализироваться в

УУ с целью принятия решения о дальнейшей

последовательности выполнения команд

П.

,

в результате формируется выходная ~.

Функции АЛУ обычно сводятся к простым

А и Л операциям, а также операциям

сдвига. Помимо результата операции АЛУ

формирует ряд признаков

результата (флагов),

хар-х результат и события, произошедшие

в процессе его получения (равенство

нулю, знак, четность, перенос, переполнение

и т. д.). Флаги могут анализироваться в

УУ с целью принятия решения о дальнейшей

последовательности выполнения команд

П.

УУ и АЛУ тесно взаимосвязаны и их обычно рассматривают как единое устройство, известное как центральный процессор (ЦП).Помимо УУ и АЛУ в процессор входит также набор регистров общего назначения (РОН).

2.Обмен в режиме прерываний. Инициализация подсистемы прерывания.

в компьютерах предусматривают обмен данными с различными устройствами в режиме прерывания. Инициатором обмена является устройство, посылающее для этого процессору сигнал INTR запроса на прерывание его работы.

Циклы обработки прерываний возникают, когда какое-либо устройство стремится приостановить работу ведущего для немедленного обмена с ним или при выполнении какого-либо программного прерывания.

Идентификация периферийного устр-ва, выставившего запрос прерывания, осуществляется с помощью векторов прерывания, посылаемых от ВУ в процессор. Для устранения конфликтов при одновременном поступлении нескольких запросов исп-ся контроллер прерываний, к-й фиксирует все поступ-ие запросы и выделяет наиболее приор-ый из них в тек-ий момент.

Для быстродействующих устройств наиболее эффективным вариантом обмена с оперативной памятью является режим DMA, т.е. обмен с памятью без участия процессора.

Чтобы блокировать обращение процессора к Пам на это время устройство, стремящееся произвести обмен с памятью, формирует к процессору сигнал HOLD запроса на DMA. По нему процессор завершает начатый цикл, отключается от шин AB и DB, а затем формирует сигнал HLDA (HoldAcknowledge), разрешая произвести обмен. По сигналу HLDA устройство, выставившее запрос, получает доступ к системным шинам и может самостоятельно организовывать циклы обмена с памятью, включая формирование адресов и управляющих сигналов. Закончив обмен, устройство снимает сигнал HOLD, тем самым разрешая процессору продолжить выполнение прерванной П.

Получив этот сигнал, процессор сохраняет состояние текущей П, затем прерывает ее выполнение и формирует сигнал INTE разрешения прерывания. В процессорах Pentium для этого используется линия M/IO (низкий уровень). Обмен производится с помощью обработчика прерывания – П обмена сданным устройством.