- •1.Основные понятия и определения, относящиеся к мп технике

- •2. Структура эвм по фон Нейману. Пять принципов фон Неймана. Цикл управления по фон Нейману

- •3. Классификация архитектур эвм по взаимодействию процессора, памяти и устройств ввода-вывода.

- •4. Классификация архитектур эвм по взаимодействию потока команд и потока данных

- •5. Классификация mimd-систем по Таненбауму (smp , numa ,mpp и cow).

- •6. Архитектуры мп . Назовите и поясните составные части понятия архитектуры.

- •7. Основные характеристики мп (m/n/k). Архитектурные особенности современных мп. Микроархитектура мп.

- •1) Тактовой частотой,

- •2) Разрядностью,

- •3) Архитектурой.

- •8. Risc и cisc-микропроцессоры.

- •Характерные особенности risc-процессоров

- •9. Структура рынка универсальных микропроцессоров

- •10. Микропроцессоры компании Intel. История создания мп, закон Myрa , динамика развития мп от Intel

- •11. Маркетинговая стратегия фирмы Intel. Платформенная стратегия фирмы на современном этапе

- •Компоненты платформ Intel

- •12. Маркировка мп от Intel .Процессорные номера для процессоров класса p4 и класса Core

- •13. Архитектура ia-32.Расширения архитектуры x86-Intel 64/em64t

- •14. Архитектура ia-64. Особенности мп Itanium, Itanium-2

- •15. Архитектура Power

- •16. Архитектура PowerPc. Архитектура Сell

- •17. Архитектура Alpha,pa-risc

- •18. Архитектура sparc, mips

- •19. Кодовое название ядер мп. Примеры (Intel, amd, via)

- •20. Новые технологии в процессорах Intel Pentium 4 (vt, ht, eist, em64t)

- •21. Описание использованных в мп на ядре Core новых технологий

- •22. Структура микропроцессорной системы.

- •23. Логическая структура микропроцессора.

- •23. Программный (синхронный асинхронный) ввод-вывод информации в мпс.

- •25. Построение магистрали адреса в мпс с использованием непрограммируемых интерфейсных компонентов к580ва86

- •26. Построение магистрали данных.

- •27. Построение магистрали управления.

- •28. Ввод-вывод информации в мпс по прерываниям; в режиме прямого доступа к памяти.

- •29. Параллельный ввод-вывод информации в мпс.

- •30. Последовательный ввод-вывод информации в мпс

- •31. Организация памяти в мпс. Подключение озу

- •32. Организация памяти в мпс. Подключение пзу

- •33. Условные обозначения компонентов Intel

- •34. Основной механизм сопряжения по времени работы мп и внешних устройств

- •35. Подключение дисплея и клавиатуры к мпс

- •36. Физическое адресное пространство памяти и портов.

- •1.3.2.2. Режимы адресации переходов.

- •1.2. Реальный режим

- •1.2.1. Параметры базового микропроцессора семейства Intel 8086.

- •Основные отличия от 486-ого процессора

- •История

- •[Править] Слияния и поглощения

- •[Править] Происхождение названия

- •Архитектура mc68000

- •Архитектура mc68020

- •Архитектура mc68030

- •Архитектура mc68040

- •Спецификация шины pci

- •Стандартные модификации pci

- •Версии HyperTransport

- •Применение HyperTransport: Замена шины процессора

- •Технические характеристики жк-монитора

- •Специализация

- •Надежность

- •[Править] Аппаратные решения

- •Размещение и Обслуживание

3. Классификация архитектур эвм по взаимодействию процессора, памяти и устройств ввода-вывода.

Многообразие ПЭВМ в зависимости от характера связей процессора, памяти и устройств ввода-вывода можно свести к двум структурам:

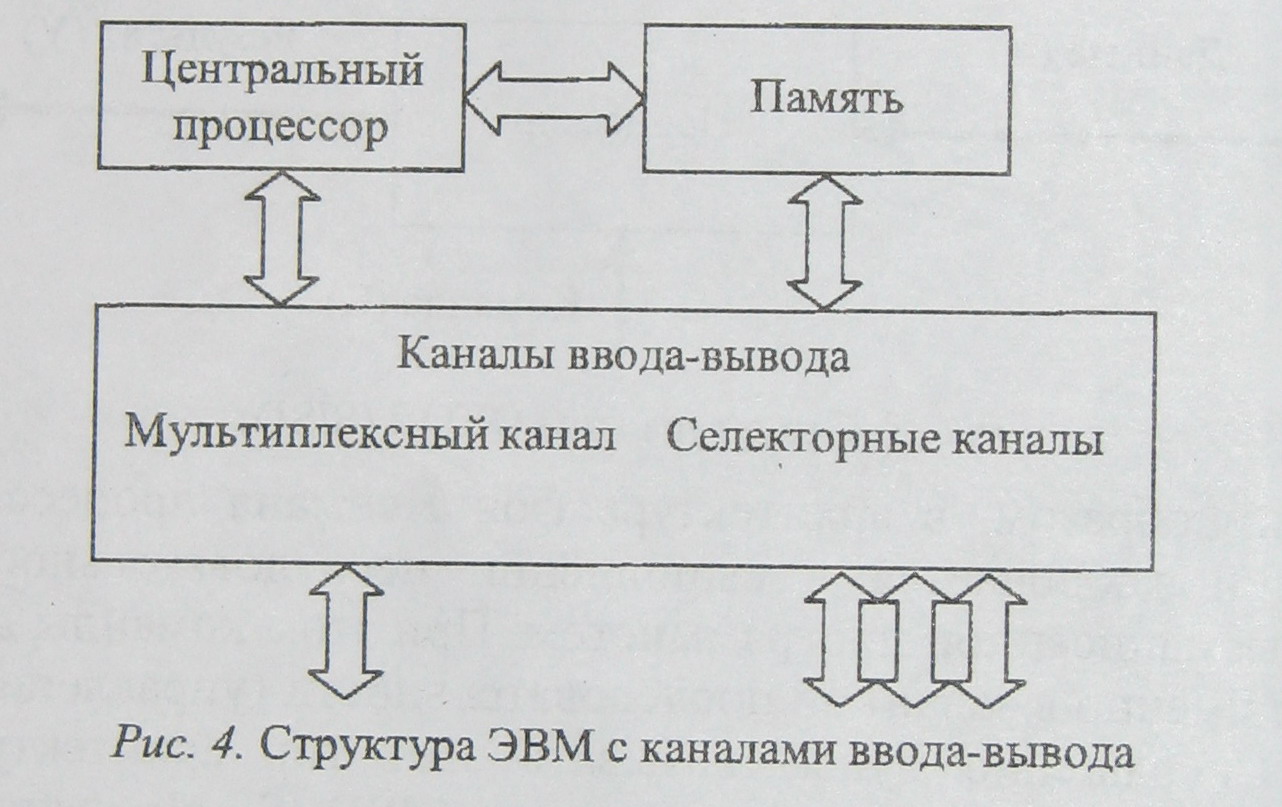

1. С использованием каналов ввода-вывода.

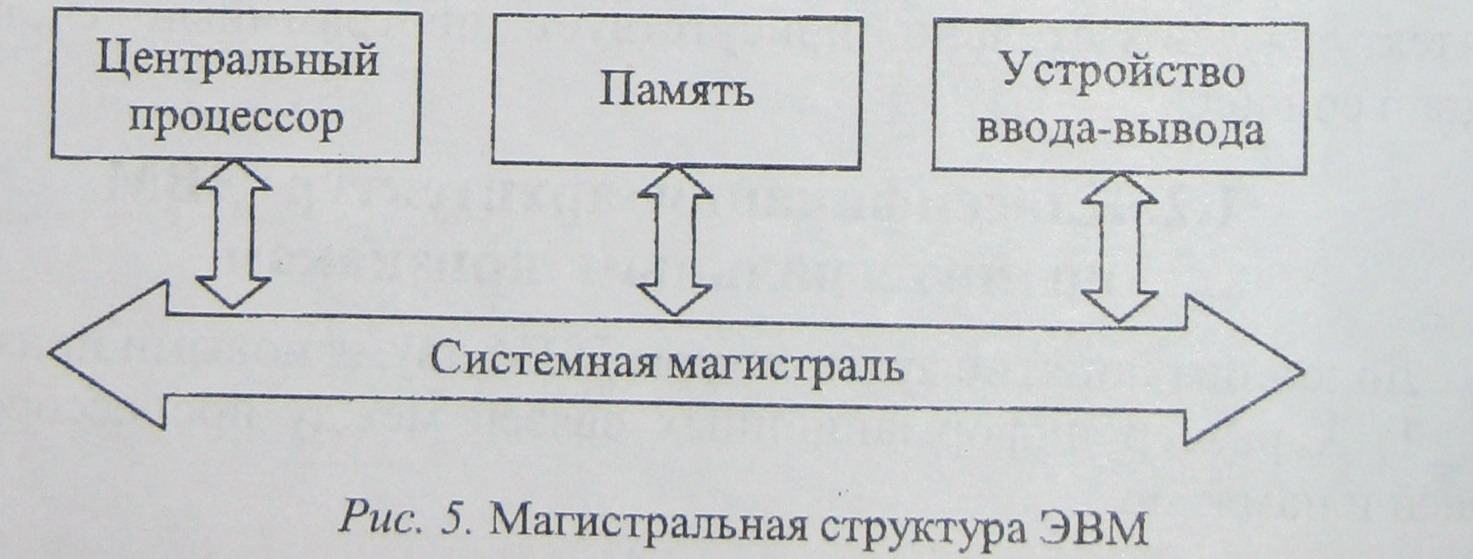

2. Магистральная структура.

Особенность первого варианта - непосредственная связь ЦП и ОЗУ. Связь же с внешними устройствами осуществляется посредством специальных процессоров ввода-вывода, называемых часто каналами ввода-вывода (рис. 4). Использование нескольких каналов обеспечивает параллельное выполнение операций ввода-вывода с несколькими устройствами ввода-вывода.

Концепция магистральной структуры

4. Классификация архитектур эвм по взаимодействию потока команд и потока данных

Классификация Флинна для архитектур вычислительных систем строится по признаку множественности потоков команд и данных.

Однопроцессорная ЭВМ. Структура обыкновенной однопроцессорной ЭВМ (рис. 4.5) содержит одиночный поток команд и одиночный поток данных ОКОД (Single Instruction Single Data – SISD).

Матричная МПС – это структура типа одиночный поток команд и множественные потоки данных ОКМД (Single Instruction Multiple Data – SIMD). Система содержит некоторое число одинаковых сравнительно простых быстродействующих процессоров, соединенных между собой и с памятью данных регулярным образом так, что образуется сетка (матрица), в узлах которой размещаются процессоры (рис. 4.6). В системе образуется несколько потоков данных и один общий поток команд. Здесь возникает сложная задача распараллеливания алгоритмов решаемых задач для обеспечения загрузки процессоров.

В зависимости от возможностей контроллера и процессорных элементов, числа процессоров, организации режима поиска и характеристик маршрутных и выравнивающих сетей архитектуры класса SIMD подразделяются на четыре типа:

матричные процессоры; ассоциативные процессоры; процессорные ансамбли;

конвейерные процессоры.

Матричные процессоры используются для решения векторных и матричных (сеточных) задач и в общем случае для реализации алгоритмов, соответствующих характеристикам архитектуры SIMD. К этим задачам относятся в основном задачи числовой обработки. Для решения нечисловых задач используются ассоциативные процессоры. Процессорные ансамбли применимы как для числовой, так и нечисловой обработки. Конвейерные и векторные процессоры могут быть отнесены к архитектуре SIMD, но их можно причислить также и к другим типам архитектур.

Конвейерная МПС – это структура типа МКОД (или MISD) (рис. 4.7). Система имеет регулярную структуру в виде цепочки последовательно соединенных процессоров или специальных вычислительных блоков (СВБ), так что информация на выходе одного процессора является входной информацией для следующего в конвейерной цепочке. Процессоры СВБ образуют конвейер, на вход которого одинарный поток данных доставляет операнды из памяти. Каждый процессор обрабатывает свою часть задачи, передавая результаты соответствующему процессору, который использует их в качестве исходных данных. Таким образом, решение задач для некоторых исходных данных развертывается последовательно в конвейерной цепочке. Это обеспечивает подведение к каждому процессору СВБ своего потока команд, т.е. имеет место множественный поток команд.

Общий случай МПС – это структура типа МКМД (или MIMD). К классу MIMD могут быть отнесены, хотя и не всегда однозначно, следующие конфигурации:

а) мультипроцессорные системы;

б) системы с мультиобработкой;

в) многомашинные системы;

г) компьютерные сети.