- •Лекции Программируемые логические матрицы

- •1. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •§ 1.1. Вводные замечания

- •§ 1.2. Программируемые логические матрицы и программируемая матричная логика (плм и пмл)

- •Схемы с памятью

- •§ 1.3. Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

- •§ 2.2. Программируемые пользователем вентильные матрицы (fpga)

- •§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

- •§ 2.4. Сбис программируемой логики типа "система на кристалле"

- •2.5. Параметры и популярные семейства бис программируемой логики

- •§ 2.6. Интерфейс jtag. Периферийное сканирование. Программирование в системе (isp). Конфигурирование сбис пл

- •3. Методика и средства проектирования цифровых устройств

- •§ 3.1. Общие сведения

- •§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

2.5. Параметры и популярные семейства бис программируемой логики

БИС ПЛ характеризуются многими параметрами и их подробная классификация по разнообразным признакам сложна и громоздка. К важнейшим параметрам относятся:

1 кратность программирования (однократное, многократное с ограничением числа циклов, неограниченно многократное), определяемая типом программируемых элементов;

1 уровень интеграции (максимальный уровень интеграции определяется возможностями технологических процессов);

3 быстродействие (ограничивается возможностями технологических процессов);

3 структурная организация (FPGA, CPLD, гибкая логика со смешанной архитектурой, схемы типа "система на одном кристалле"), в частности, наличие или отсутствие специализированных областей встроенной памяти.

Кроме перечисленных параметров, важную роль играет и ряд других: тип базового логического элемента, постоянство или непостоянство задержек сигналов в путях их передачи, наличие или отсутствие интерфейса JTAG и программирования в системе ISP, совместимости со стандартными интерфейсами (в частности, шиной PCI), уровни питающих напряжений и режимы пониженной мощности, наличие средств засекречивания реализованного проекта и др.

Способы оценки таких параметров, как уровень интеграции (Density) и быстродействие (Performance) требуют пояснений.

Уровень интеграции (сложность)

Уровень интеграции СБИС ПЛ оценивается числом эквивалентных вентилей (обычно это вентили 2И-НЕ), размещенных на кристалле. Объективная оценка сложности не так проста, как может показаться на первый взгляд. Нельзя просто подсчитать число эквивалентных вентилей в СБИС ПЛ, поскольку их в ней может даже и не быть, а имеющиеся блоки могут не разбиваться на такие вентили.

Рекламируемые изготовителями оценки сложности кристаллов до некоторых пор получались по разным методикам, что вносило путаницу в вопросы сравнительной оценки разных СБИС ПЛ. Затем консорциум компаний под названием PREP (Programmable Electronics Performance Corporation) предложил набор эталонных схем для проверки возможностей СБИС ПЛ. Для измерения сложности кристалла каждая схема реализуется в нем в максимально возможном числе раз, что дает оценку сложности СБИС ПЛ числом "помещающихся" в ней эталонных схем. В качестве эталонных схем было выбрано более 10 типовых функциональных узлов (регистры, дешифраторы и т. п.). Для эталонных схем можно определить число эквивалентных вентилей, необходимых для их построения. Таким путем можно выйти и на оценку уровня интеграции СБИС ПЛ числом эквивалентных вентилей. При этом методика PREP четко оговаривает условия измерений, использует усреднение данных по разным эталонным узлам и приводит к более или менее объективной оценке сложности СБИС.

СБИС ПЛ первых поколений имели достаточно однородную структуру и для них указывались два числа эквивалентных вентилей — полное (total) и пользовательское (usable), т. к. не вся схема кристалла может быть использована системотехником для реализации его проекта. В дальнейшем положение осложнилось, например, в СБИС появились специализированные области памяти и другие структурные неоднородности. Для таких СБИС приводятся несколько чисел для оценки сложности. Под числом логических вентилей понимают оценку сложности без учета памяти. Под числом системных вентилей понимают оценку, учитывающую и область памяти, сложность которой также пересчитана в число эквивалентных вентилей. Число системных вентилей обычно задается диапазоном, т. к. конкретные числа существенно зависят от типа реализуемого проекта. Поэтому при сравнении СБИС ПЛ по сложности следует обращать внимание на тот смысл, который вкладывается в данном конкретном случае в приводимый показатель "число эквивалентных вентилей". К сожалению, во многих книгах такие цифры приводятся без комментариев.

Быстродействие СБИС

Быстродействие СБИС характеризуется либо задержкой распространения сигнала по указанным путям (pin-to-pin, comer-to-corner, clock-to-output), либо максимально возможной частотой работы схемы в целом (системная частота) или счетного триггера (частота счетчика Fcnt)- Обычно системная частота приблизительно вдвое ниже, чем частота переключений счетного триггера. При наличии встроенного ОЗУ указывается и цикл доступа к памяти.

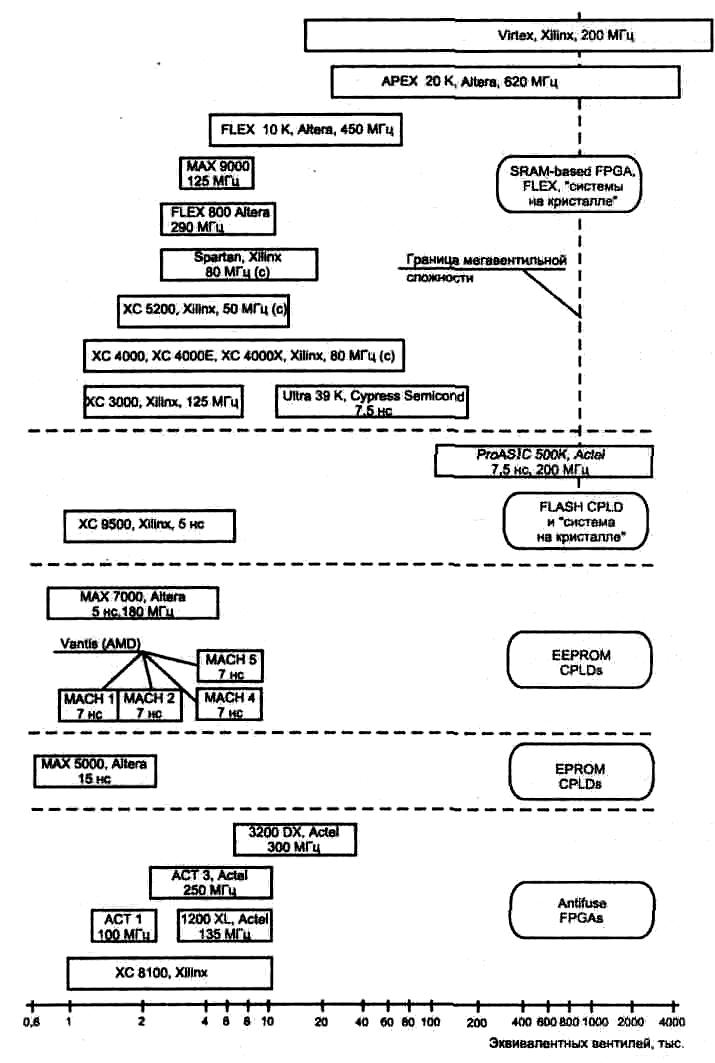

На рис. 2.23 представлены параметры сложности и быстродействия семейств СБИС ПЛ.

Рис. 2.23. Параметры сложности и быстродействие СБИС ПЛ

( Замечание )

Ввиду расхождений в методике определения отдельных параметров разными производителями и неполноты сведений в технических описаниях некоторых микросхем приводимые данные следует считать ориентировочными.

В качестве параметров быстродействия даны максимальные частоты работы, причем системные частоты отмечены буквой "с" в скобках. Сложность оценивается полным числом вентилей, для микросхем со встроенной памятью приводятся числа, соответствующие системным вентилям. Границы сложностей для семейства даются в логарифмической шкале.

Нельзя не отметить, что параметры СБИС ПЛ довольно быстро изменяются, т. к. новые их поколения изготовляются по все более совершенной технологии. Поэтому сведения, подобные приведенным на рис. 2.23, нуждаются в постоянных дополнениях. Тем не менее, такие сведения полезны, т. к. дают общее представление о развитии и возможностях микросхем программируемой логики.

Среди представленных популярных СБИС ПЛ широко известна продукция фирмы Xilinx, которая в 1985 г. выпустила первую в мире FPGA с триггерной памятью конфигурации и с тех пор постоянно развивает архитектуру и схемотехнику СБИС ПЛ.

После первого поколения FPGA XC2000 (на рис. 2.23 не показано) появились схемы второго поколения ХСЗООО и третьего— ХС4000. Продукция фирмы обогатилась также семействами FPGA, ориентированными на определенные области применения. Так, например, семейство ХС6200 ориентировано на реализацию сопроцессоров. Это можно возлагать и на FPGA общего назначения, однако их архитектуры создают при этом определенные ограничения, т. к. на интерфейс с центральным процессором тратится значительная часть ресурсов программируемой логики, да и сама архитектура FPGA не особенно приспособлена к потоковым алгоритмам, типичным для сопроцессоров. Этих недостатков лишена архитектура семейства ХС6200, предусматривающая встроенный интерфейс с процессором, мелкозернистые ЛБ и др.

FPGA семейства ХС8100 не являются репрограммируемыми, их однократное программирование ведется с помощью перемычек технологии MicroVia, позволяющей располагать пробиваемые перемычки между двумя металлизированными слоями, т. е. не в плоскости размещения логических элементов, что значительно сокращает площадь кристалла, имеющего архитектуру "море вентилей". Тем самым совмещаются хорошие трассировочные ресурсы и небольшая площадь кристалла. Семейство является недорогой альтернативой схемам БМК.

Семейство репрограммируемых FPGA.XC5200 в сравнении со схемами семейства ХС4000 отличается, в частности, меньшей стоимостью.

Новые технологические достижения позволили выпустить в последние годы семейства FPGA с улучшенной архитектурой, являющиеся продолжением развития линии ХС4000, а именно ХС4000Е и ХС4000Х. Появилась также и серия Spartan.Семейства ХС4000Е и ХС4000Х позволяют реализовать на их основе сложные проекты систем высокого быстродействия, в их составе 20 представителей. Семейство Spartan ориентировано на удовлетворение полного комплекса требований, характерного для построения систем эквивалентной сложностью до 40 тыс.вентилей.

В новых семействах имеются низковольтные версии (с буквой L в маркировке). Микросхемы семейства ХС9500 относятся к классу CPLD.

Интересно отметить, что при запуске в производство большой серии устройств (свыше 5—10 тысяч) можно заказать у самой фирмы Xilinx реализацию на основе стандартных БМК, что при этих условиях может значительно снижать стоимость продукции.

Другим примером фирмы-производителя классических FPGA является фирма Actel, работавшая с программируемыми элементами antifuse, а недавно выпустившая микросхему с элементами памяти конфигурации типа Flash (семейство Pro ASIC500K).

Высокое качество, компактность и надежность перемычек типа ONO позволили размещать на кристалле большое их число (уже в первых FPGA было до 700 000 перемычек). Это означало возможность увеличения числа сегментов в системе межсоединений, и, тем самым, обеспечения хороших трассировочных ресурсов кристалла. Автоматические размещение и трассировка проектов осуществимы даже при 90... 100% использовании логических элементов и фиксации позиций задействованных выводов.

Фирмой Actel производятся FPGA ACT1, 1200XL (замена семейства АСТ2), АСТЗ, 3200DX с однократным программированием и микросхемы с Флэш-памятью конфигурации, к которым относится семейство Pro ASIC500K, начальная серия которого насчитывает 7 представителей. Семейство рассчитано, в частности, на применения с интенсивным интерфейсом (имеет большое число конфигурируемых блоков ввода/вывода) и отличается потреблением малой мощности. Гибкость возможных применений микросхем семейства обусловлена мелкозернистостью логических ячеек, которые можно рассматривать как трехвходовые программируемые вентили с программируемостью каждого входа на прямую или инверсную передачу входного сигнала. В состав ячейки входят элементы 2И-НЕ, мультиплексоры и флэш-ключи, которые конфигурируются как популярные логические элементы или триггеры типа D.

Микросхемы семейства Pro ASIC500K выполнены по технологии с минимальными размерами 0,25 мкм с четырьмя слоями металлизации. Задержка сигнала в логической ячейке и локальной связи не превышает 0,5 нс. Блоки памяти работают на частотах до 133 МГц, цикл FIFO составляет 7,5 нс.

СБИС ПЛ фирмы Altera принадлежат в основном к CPLD и схемам гибкой логики FLEX со смешанной архитектурой. Первыми CPLD были несложные микросхемы семейства Classic, заменявшие собою схемы из 10...20 корпусов СИС при задержках по цепи "вход-выход" не более 10 нс, наличии Турбо-бита и режима засекречивания проекта.

Микросхемы семейства МАХ 5000 значительно сложнее, заменяют устройства из нескольких десятков корпусов СИС, архитектура их заложила основы архитектур следующих поколений и близка к архитектуре семейства МАХ 7000, подробно рассмотренной в § 2.3.

Семейство МАХ9000 продолжило линию развития своих предшественников, но обладает и рядом новых свойств (ISP, интерфейс JTAG, регистровая буферизация входных сигналов, работа в системах со смешанным питанием 5 и 3,3 В, наличие двух линий обратной связи в макроячейке, что позволяет реализовать в ней одновременно комбинационную и регистровую схему и др.).

Семейства типа FLEX имеют смешанную архитектуру. Первое их поколение — схемы FLEX 8000, второе — FLEX 10K, которое рассмотрено в § 2.3.

СБИС ПЛ типа "система на кристалле" представлены уже в продукции нескольких фирм, в том числе фирм Altera (APEX 20K), Xilinx (Virtex). Сюда же можно отнести микросхемы ProASIC5QOK фирмы Actel и Ultra 39K фирмы Cypress Semiconductor.

Параметры наиболее популярных СБИС ПЛ приведены в табл. 2.1—2.4.

Таблица 2.1. Основные параметры FPGA фирмы Xilinx

Схема

|

Максимальное число вентилей (без ЗУ), тысяч

|

Максимальная емкость памяти (без логики), бит

|

Типичный диапазон числа вентилей (логика + ЗУ), тысяч*

|

Число КЛБ в матрице

|

Число триггеров

|

Число пользовательских входов-выходов

|

XC4000E/EX/XL

|

|

|

|

|

|

|

ХС4003Е

|

3

|

3200

|

2-5

|

100= 10х10

|

360

|

80

|

XC4005E/XL

|

5

|

6272

|

3-9

|

196=14х14

|

616

|

112

|

ХС4006Е

|

6

|

8192

|

4-12

|

256 = 16 х 16

|

768

|

128

|

ХС4008Е

|

8

|

10368

|

6-15

|

324=18х18

|

936

|

144

|

XC4010E/XL

|

10

|

12800

|

7-20

|

400 = 20 х 20

|

1120

|

160

|

XC4013E/XL

|

13

|

18432

|

10-30

|

576 = 24 х 24

|

1536

|

192

|

XC4020E/XL

|

20

|

25088

|

13-40

|

784 = 28 х 28

|

2016

|

224

|

ХС4025Е

|

25

|

32768

|

15-45

|

1024=32х32

|

2560

|

256

|

XC4028EX/XL

|

28

|

32768

|

18-50

|

1024=32х32

|

2560

|

256

|

XC4036EX/XL

|

36

|

41472

|

22-65

|

1296=36х36

|

3168

|

288

|

XC4044XL

|

44

|

51200

|

27-80

|

1600=40х40

|

3840

|

320

|

XC4052XL

|

52

|

61952

|

33-100

|

1936=44х44

|

4576

|

352

|

XC4062XL

|

62

|

73728

|

40-130

|

2304 = 48х48

|

5376

|

384

|

XC4085XL

|

85

|

100352

|

55—180

|

3136=56х56

|

7168

|

448

|

Таблица 8.1. Основные параметры FPGA фирмы Xilinx (окончание)

Схема

|

Максимальное число вентилей (без ЗУ), тысяч

|

Максимальная емкость памяти (без логики), бит

|

Типичный диапазон числа вентилей (логика + ЗУ), тысяч*

|

Число КЛБ в матрице

|

Число триггеров

|

Число пользовательских входов-выходов

|

Spartan

|

|

|

|

|

|

|

XCS05(XL)

|

5

|

—

|

2-5

|

100=10х10

|

360

|

80

|

XCS10(XL)

|

10

|

—

|

3-10

|

196=14х14

|

616

|

112

|

XCS20(XL)

|

20

|

—

|

7-20

|

400 = 20 х 20

|

1120

|

160

|

XCS30(XL)

|

30

|

—

|

10-40

|

576 = 24 х 24

|

1536

|

192

|

XCS40(XL)

|

40

|

—

|

13-40

|

784 = 28 х 28

|

2016

|

224

|

* При использовании ресурсов схемы для реализации как логики, так и памяти, предполагается, что в качестве ЗУ работают 20...30% КЛБ.

Таблица 2.2. Основные параметры СБИС семейства МАХ фирмы Аltеrа

Схема

|

Макроячеек

|

Вентилей, тысяч

|

Триггеров

|

Число пользовательских входов-выходов

|

Частота Fcnt, МГц

|

МАХ 7000

|

|

|

|

|

|

ЕРМ7032

|

32

|

0,6

|

—

|

36

|

178

|

ЕРМ7064

|

64

|

1,25

|

—

|

68

|

178

|

ЕРМ7096

|

96

|

1,8

|

—

|

76

|

151

|

ЕРМ7128

|

128

|

2,5

|

—

|

100

|

151

|

ЕРМ7160

|

160

|

3,2

|

—

|

104

|

151

|

ЕРМ7192

|

192

|

3,75

|

—

|

124

|

125

|

ЕРМ7256

|

256

|

5

|

—

|

164

|

125

|

MAX 9000

|

|

|

|

|

|

ЕРМ9320

|

320

|

6

|

484

|

168

|

125

|

ЕРМ9400

|

400

|

8

|

580

|

159

|

125

|

ЕРМ9480

|

480

|

10

|

676

|

175

|

118

|

ЕРМ9560

|

560

|

12

|

772

|

216

|

118

|

Обе серии FPGA способны работать на системной частоте свыше 80 МГц. Низковольтные версии работают при напряжениях питания 3,0... 3,6 В (ХС4000Е и ХС4000Х с буквами L) или 3,3 В (Spartan). Данные семейства Spartan справедливы как для схем с обычным питанием (без добавления букв XL, т. е. просто XCS05 и т. д.), так и для схем с добавлением XL в маркировке.

Таблица 8.3. Основные параметры СБИС семейства FLEX 10K фирмы Altera

Схема

|

Частота Fcnt, МГц

|

Вентилей, тысяч

|

Триггеров

|

Емкость ОЗУ, бит

|

Число пользовательских входов-выходов

|

EPF10K10

|

450

|

10

|

720

|

6144

|

134

|

EPF10K20

|

450

|

20

|

1344

|

12288

|

189

|

EPF10K30

|

450

|

30

|

1968

|

12288

|

246

|

EPF10K40

|

450

|

40

|

2576

|

16384

|

183

|

EPF10K50

|

450

|

50

|

3184

|

20480

|

310

|

EPF10K70

|

450

|

70

|

4096

|

18432

|

358

|

EPF10K100

|

450

|

100

|

5392

|

24576

|

406

|

EPF10K130

|

450

|

130

|

7126

|

32762

|

470

|

Таблица 2.4. Основные параметры СБИС типа "система на кристалле" фирмы Altera (APEX) и Xilinx (Virtex)

Схема

|

Максимальное число системных вентилей, тысяч

|

Емкость встроенного ОЗУ, Кбит

|

Емкость распределенного ОЗУ, Кбит

|

Число пользовательских входов-выходов

|

APEX 20K

|

|

|

|

|

ЕР20К100(Е)

|

236

|

53

|

—

|

252

|

ЕР20К160(Е)

|

404

|

82

|

—

|

320

|

ЕР20К200(Е)

|

526

|

106

|

—

|

382

|

ЕР20КЗОО(Е)

|

728

|

147

|

—

|

420

|

ЕР20К400(Е)

|

1052

|

213

|

—

|

502

|

ЕР20К600(Е)

|

1573

|

311

|

—

|

620

|

ЕР20К1000(Е)

|

2670

|

540

|

—

|

780

|

Таблица 2.4. Основные параметры СБИС типа "система на кристалле" фирмы Altera (APEX) и Xilinx (Virtex) (окончание)

Схема

|

Максимальное число системных вентилей, тысяч

|

Емкость встроенного ОЗУ, Кбит

|

Емкость распределенного ОЗУ, Кбит

|

Число пользовательских входов-выходов

|

Virtex*

|

|

|

|

|

XCV50

|

58

|

38

|

24

|

180

|

XCV100

|

109

|

41

|

38

|

180

|

XCV150

|

165

|

49

|

55

|

260

|

XCV200

|

237

|

57

|

75

|

284

|

XCV300

|

323

|

64

|

98

|

316

|

XCV400

|

468

|

82

|

153

|

404

|

XCV600

|

661

|

98

|

211

|

512

|

XCV800

|

888

|

114

|

300

|

512

|

XCV1000

|

1124

|

130

|

392

|

512

|

XCV1000E

|

1569

|

329

|

392

|

660

|

XCV1600E

|

2189

|

589

|

497

|

724

|

XCV2000E

|

2542

|

655

|

614

|

804

|

XCV2600E

|

3264

|

749

|

812

|

804

|

XCV3200E

|

4074

|

851

|

1038

|

804

|

Для семейства XCVXXXE показаны лишь микросхемы наивысшей сложности, имеющие напряжение питания 1,8 В. Кроме них имеются шесть микросхем с напряжением питания 2,5 В, сложность которых ниже.