- •Лекции Программируемые логические матрицы

- •1. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •§ 1.1. Вводные замечания

- •§ 1.2. Программируемые логические матрицы и программируемая матричная логика (плм и пмл)

- •Схемы с памятью

- •§ 1.3. Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

- •§ 2.2. Программируемые пользователем вентильные матрицы (fpga)

- •§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

- •§ 2.4. Сбис программируемой логики типа "система на кристалле"

- •2.5. Параметры и популярные семейства бис программируемой логики

- •§ 2.6. Интерфейс jtag. Периферийное сканирование. Программирование в системе (isp). Конфигурирование сбис пл

- •3. Методика и средства проектирования цифровых устройств

- •§ 3.1. Общие сведения

- •§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

§ 2.4. Сбис программируемой логики типа "система на кристалле"

Уменьшение топологических норм проектирования и ряд технологических усовершенствований довели уровень интеграции современных микросхем СБИС ПЛ до величин в несколько миллионов эквивалентных вентилей, а быстродействие до тактовых частот в 500...600 и более МГц. На таких кристаллах можно разместить целую систему (процессорную часть, память, интерфейсные схемы и др.).

Определение СБИС как "система на кристалле" возникло вследствие двух факторов. Во-первых, из-за высокого уровня интеграции, позволяющего разместить на кристалле схему высокой сложности (систему). При этом разные по функционированию блоки реализуются одними и теми же аппаратными средствами благодаря их программируемости. Такие СБИС обозначаются в англоязычной литературе термином generic. Во-вторых, из-за того, что СБИС приобретает специализированные области, выделенные на кристалле для определенных функций — аппаратные ядра (Hardcores). Системы разного назначения разделяются, тем не менее, на типовые части, что и ставит вопрос о целесообразности введения в СБИС ПЛ наряду с программируемой логикой специализированных областей с заранее определенными функциями.

Введение специализированных аппаратных ядер, имея ряд позитивных следствий, сужает в то же время круг потребителей СБИС, поскольку в сравнении с полностью программируемыми схемами (типа generic) уменьшается их универсальность.

Реализация сложных функций специализированными аппаратными ядрами значительно уменьшает площадь кристалла в сравнении с их реализациями на конфигурируемых логических блоках. Для некоторых аппаратных ядер площадь снижается на порядок, для других меньше. Например, умножитель 8х8, построенный по модифицированному алгоритму Бута и реализованный методами заказного проектирования, разместился на площади в 5 раз меньшей, чем такой же, реализованный на реконфигурируемых логических блоках, обычных для взятой FPGA.

Таким образом, введение специализированных аппаратных ядер в FPGA и CPLD — процесс противоречивый по результатам. Он сокращает площадь кристалла при реализации сложных функций и ведет к достижению максимального быстродействия, но и таит в себе нежелательные последствия для изготовителя СБИС, т. к. может ощутимо сузить рынок их сбыта, а это ведет к росту цен и потере в какой-то мере конкурентоспособности продукции.

Что же будет преобладать? Здесь ключевой вопрос — какие именно специализированные аппаратные ядра будут выбраны для реализации.

Самый очевидный выбор — блоки ОЗУ. Эти блоки в той или иной мере нужны почти для всех систем, причем некоторые из них требуют очень больших объемов памяти. Выяснились уже и условия эффективного использования ядер памяти — не слишком крупные блоки, возможность изменять организацию памяти, возможность иметь асинхронный и синхронный режимы работы, организовывать буферы FIFO и двухпортовую память. Многие FPGA уже давно основываются на SRAM-ячейках (обычно на каждый конфигурируемый ЛБ тратится 16...32 бит ОЗУ), и эти ячейки могут быть применены не только для конфигурирования ЛБ, но и организуются в простые ОЗУ, которые могут далее объединяться в более емкие регистровые файлы. Однако такой вариант не дает максимального быстродействия и существенно снижает количество доступной пользователю логики кристалла, т. к. каждый 16...32 бита памяти "выводят из строя" целый ЛБ, т. е. по эквивалентной сложности 10... 20 логических вентилей.

В среднем блок ОЗУ с заказным проектированием емкостью 256...512 бит может быть реализован на площади приблизительно 1/10 от той, которая затрачивается на подобный блок, составленный из распределенных на кристалле ячеек памяти конфигурации. Времена доступа также уменьшаются в 1,5...4 раза.

Области ОЗУ — первыеbи, безусловно, главные специализированные аппаратные ядра. Других не так уж много. Это умножители, используемые в некоторых СБИС ПЛ, а также схемы интерфейса JTAG. Ядра интерфейса JTAG успешно внедрились во многие СБИС ПЛ, поскольку они выполняют важные функции, нужные очень многим, занимают очень небольшую площадь на кристалле и позволяют достичь высокого быстродействия.

Самыми сложными из практически известных ядер являются контроллеры шины PCI, также необходимые в очень многих приложениях и требующие максимального быстродействия.

Семейство СБИС типа APEX 20K/KE

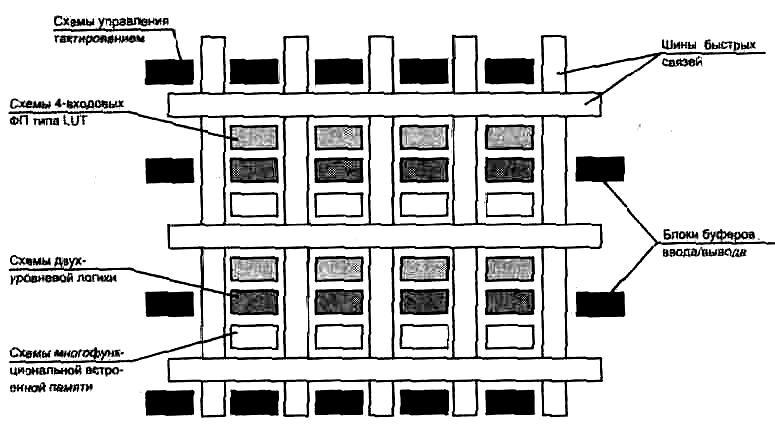

Перспективы существенного расширения перечня реализованных специализированных аппаратных ядер явно ограничены. Для реализации систем на кристалле фирма Altera выпустила семейство СБИС типа APEX 20K/KE, построенных по архитектуре, названной Multicore. В них комбинируются табличные методы реализации функций и реализации их двухуровневыми структурами, т. е. сочетаются характерные признаки FPGA и CPLD. Имеется встроенная память и гибкая система интерфейсов (рис. 2.21).

Рис. 2.21 Структура СБИС семейства APEX 20K

Эти СБИС отличались наибольшим среди промышленных СБИС ПЛ объемом встроенной памяти (от 58 до 540 Кбит для разных микросхем). Сложность — от 263 К до 2,67 М системных вентилей. Понятие "системных вентилей" поясняется в § 2.5.

Сочетание средств логической обработки из арсеналов FPGA и CPLD облегчает обработку разнотипных функций (трактов передачи данных, автоматов с памятью). При реализации автоматов задержки выработки функций возбуждения триггеров составляют 4,8 нс, что соответствует работе автомата на частотах около 200 МГц. Ядро ОЗУ состоит из блоков ESB (Embedded System Block) no 2 Кбит, число блоков от 26 (у младших представителей семейства) до 264 (у старших). Блоки могут работать независимо (с вариантами организации 128 х 16, 256 х 8, 512 х 4, 1024 х 2, 2048 х 1) или соединяться с другими для образования более емкой памяти. Вместе со схемами близлежащих логических блоков блоки памяти могут образовывать стандартные SRAM, буферы FIFO, двухпортовую память, а в некоторых микросхемах возможна организация ассоциативной памяти САМ (Content-Addressable Memory). Имеются обширные возможности выбора сигналов интерфейса — в семействе "К" это 2,5 В I/O; 3,3 В PCI; LVCMOS (низковольтные схемы КМОП) и LVTTL (низковольтные ТТЛ). В семействе "КЕ" выбор сигналов интерфейса значительно шире.

Семейство СБИС типа Virtex

В качестве "истинной программируемой системы на кристалле" фирма Xilinx представляет СБИС ПЛ Virtex. Как и APEX 20K, это кристаллы с мегавентильным уровнем интеграции и большими емкостями встроенной памяти. Представители семейства имеют от 38 до 851 Кбит встроенной памяти, к которой могут добавляться от 24 до 1038 Кбит памяти от схем конфигурации логических блоков типа LUT. Схемы работают на системной частоте 180...200 МГц. Понятие "системная частота" поясняется в §2.5. Достижимый процент использования вентилей оценивается как 90%. Число пользовательских выводов лежит в диапазоне 180...804. Линии ввода/вывода программируются на ряд стандартов интерфейсных сигналов (GTL+, LVTTL, SSTL3-1 и др.).

Файл конфигурации (для кристаллов с 100 тыс. эквивалентных вентилей) имеет объем 2 Мбита и загружается за менее чем 3 мс, что является малым временем, способствующим применению микросхем в системах с реконфигурацией аппаратных средств.

Система межсоединений сохраняет многое из свойственного предыдущим семействам СБИС ПЛ фирмы Xilinx, но имеет и своеобразие. В дополнение к прежним ресурсам межсоединений созданы новые диагональные связи с хорошей предсказуемостью задержек.

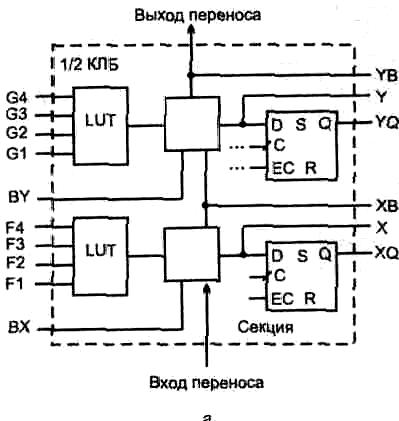

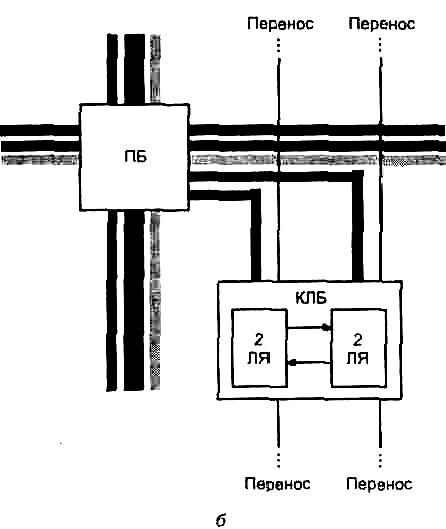

Логические ячейки ЛЯ содержат 4-входовые преобразователи типа LUT, схемы переноса и управления СПУ и D-триггеры с общим (глобальным) тактированием и входами сброса/установки (рис. 2.22, а). Для упрощения программного обеспечения средств проектирования ЛЯ соединяются парами в секции (Slice). Две секции составляют конфигурируемый логический блок КЛБ (CLB). Имеются схемы PLL (см. § кн-3.6), обеспечивающие коррекцию временных соотношений для тактовых импульсов.

Логические ячейки имеют высокоскоростные схемы переноса для построения каскадных структур. Благодаря им такие схемы, как 32-разрядный счет2чик или АЛУ работают на частотах до 100 МГц.

Основа LUT — статическое ЗУ емкостью 16 бит с задержкой выработки функций 1,2 нс. Память может использоваться и по прямому назначению с возможностью объединения в более крупные блоки. Можно объединять два элемента LUT для воспроизведения функций пяти переменных.

Рис. 2.22. Схема секции (а) и схема связей КЛБ с системой межсоединений (б)

Рис. 2.22. {окончание} Общий план (в) СБИС семейства Virtex

Блоки ввода/вывода в регистровом режиме имеют задержки по пути "такт-выход" 6 не без PLL и 3,5 нс с PLL. Максимальный темп передач ввода/вывода 110 МГц без PLL и 160 МГц с PLL.

В области памяти содержится набор 2-портовых SRAM по 4 Кбит каждый с несколькими вариантами организации (4Кх1, 2К х 2, 1К х 4, 512х8. 256 х 16). Память синхронная, время цикла 10 нс. Предусмотрены конфигурации памяти типа видеобуфера, буферов FIFO.

Внутренняя область состоит из матрицы блоков (Versa Block), содержащих переключательные блоки ПБ и КЛБ (рис. 2.22, б). Внутри КЛБ созданы быстрые пути трассировки. Между КЛБ образованы связи общего назначения и некоторое количество прямых связей (см. §2.2). Линии обратных связей обладают малыми задержками, поэтому воспроизведение сложных функций с помощью нескольких LUTs не ведет к большим потерям быстродействия. Прямые связи обеспечивают межсоединения двух смежных КЛБ в горизонтальном направлении, разгружая в известной степени систему межсоединений общего назначения.

С каждым Versa-блоком связан ПБ (GRM, General Routing Matrix), коммутирующий горизонтальные и вертикальные связи. В системе связей есть не только линии одинарной длины, передающие сигналы от одной GRM к другой смежной, но и буферированные линии передач на расстояние в 6 GRM. По всей длине и ширине кристалла проходят длинные линии.

На периферии кристалла расположены блоки ввода/вывода с буферированием входных и выходных сигналов и управлением третьим состоянием

Программируются такие возможности, как регулировка крутизны фронта, "подтягивание" линии к высокому потенциалу, регулировка задержки и другие аспекты операции буферирования. Возможен выбор того или иного стандарта сигналов интерфейса, включая GTL+, SSTL, LVTTL.

Многообразные ресурсы трассировки дополнены средствами, названными VersaRing. Это интерфейс между логикой внутренней области и блоками ввода/вывода, позволяющий перекоммутировать связи с внешними вывода-. так что при модификации схемы во внутренней области связи с монтажом печатной платы могут не изменяться.

Параметры микросхем семейства Virtex приведены в табл. 2.4 (см. § 2.5). Микросхемы типа "система на кристалле" выпускаются и рядом других фирм:

Ultra 39K (Cypress Semicond.), QL (Quick Logic), ispLSISOOV (Lattice Semi-nd.), ProASIC500K (Actel), PSD (WSI) и др.