- •Лекции Программируемые логические матрицы

- •1. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •§ 1.1. Вводные замечания

- •§ 1.2. Программируемые логические матрицы и программируемая матричная логика (плм и пмл)

- •Схемы с памятью

- •§ 1.3. Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

- •§ 2.2. Программируемые пользователем вентильные матрицы (fpga)

- •§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

- •§ 2.4. Сбис программируемой логики типа "система на кристалле"

- •2.5. Параметры и популярные семейства бис программируемой логики

- •§ 2.6. Интерфейс jtag. Периферийное сканирование. Программирование в системе (isp). Конфигурирование сбис пл

- •3. Методика и средства проектирования цифровых устройств

- •§ 3.1. Общие сведения

- •§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

Сложные программируемые логические ИС (СПЛИС) архитектурно произошли от структур PLD (PAL, GAL) и называются CPLD (Complex Programmable Logic Devices).

Для русского эквивалента этого названия примем СПЛИС, хотя в ряде работ встречается наименование ПЛИС. Следовать этому нежелательно, т. к. многие авторы трактуют термин ПЛИС как наименование всех ИС программируемой логики вообще. Приемлемым вариантом названия для CPLD является и СПЛУ— сложные программируемые логические устройства, что соответствует переводу термина CPLD на русский язык.

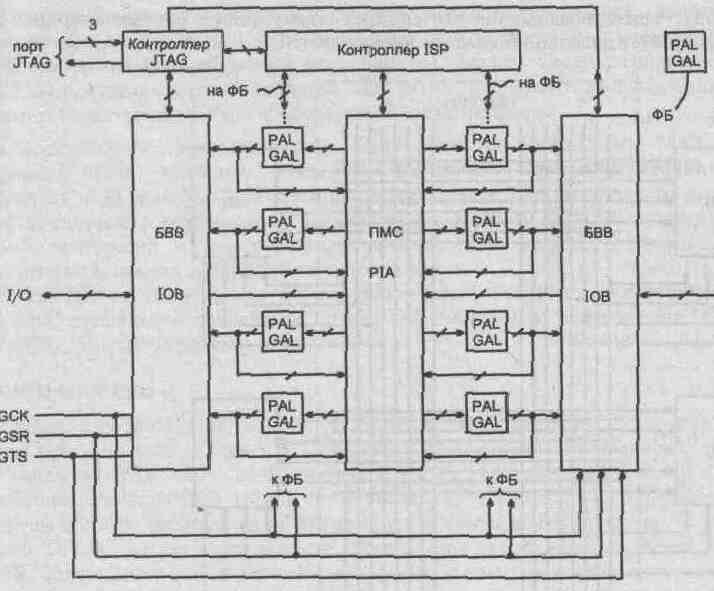

Архитектурно CPLD состоят из центральной коммутационной матрицы множества функциональных блоков ФБ (именуемых также макроячейками макроэлементами и др.) и блоков ввода/вывода на периферии кристалла. Архитектура CPLD показана на рис. 2.12, где через ПМС обозначена программируемая матрица соединений (PIA, Programmable Interconnect Array).

Рис. 2.12. Архитектура CPLD

Функциональные блоки CPLD.

Эти блоки подобны PLD и содержат многовходовую (wide) программируемую матрицу элементов И, вырабатывающую конъюнктивные термы из поступающих на ее входы переменных, группу элементов ИЛИ, между которыми распределяются выработанные термы, и некоторые другие элементы, обогащающие функциональные возможности ФБ и подобные рассмотренным в § 1.2. Функциональные блоки реализуют двухуровневую логику с вариантами формируемого результата (прямой или инверсный, комбинационный выход или регистровый выход и т. д.).

Системы коммутации CPLD.

В отличие от типичных для FPGA систем сегментированных связей, в CPLD используется непрерывная или одномерно непрерывная система связей, причем все связи идентичны, что дает хорошую предсказуемость задержек сигналов в связях — важное достоинство, облегчающее проектирование и изготовление работоспособных схем высокого быстродействия. В самих линиях связи число программируемых ключей мало, но многие из ключей не будут задействованы, так что система коммутации с единой матрицей в целом требует довольно большого числа ключей.

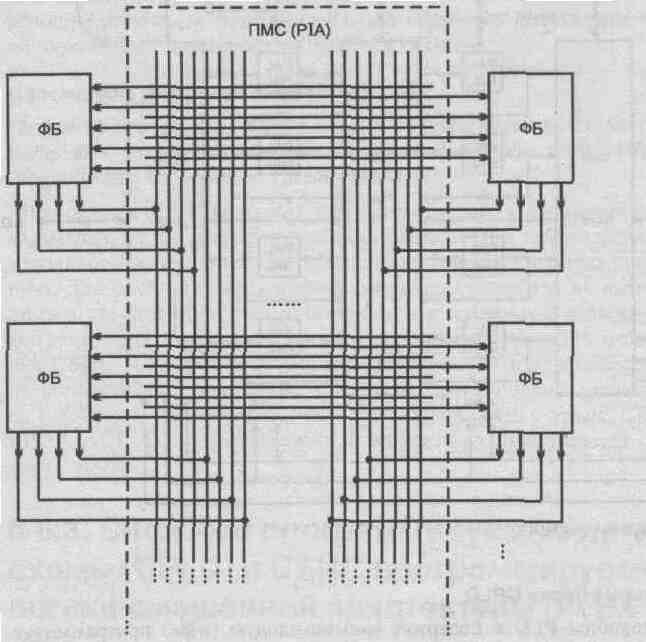

Рис. 2.13. Схема коммутации функциональных блоков CPLD с помощью программируемой матрицы соединений

Типичная ПМС (рис. 2.13) позволяет соединять выход любого ФБ со входами других. Входы ФБ связаны с горизонтальными линиями, пересекающими все вертикальные линии. Любой вход может быть подключен к любому выходу программированием точек связи между вертикальными и горизонтальными линиями. Иначе говоря, ПМС обеспечивает полную коммутируемость блоков.

Внутри самих ФБ может существовать локальная система коммутации, подобная глобальной.

CPLD и СБИС ПЛ смешанной архитектуры производятся многими фирмами. К ведущим фирмам относятся Altera (семейства MAX, FLEX, APEX и др.), Atmel (семейство ATF 1500 и др.), Vantis (ранее была известна как фирма AMD, семейство MACH), Xilinx (семейство ХС9500), Philips, Cypress Semicond. и т.д.

В рамках каждого семейства потребителю предлагается ряд представителей, различных по сложности, стоимости и другим параметрам, с целью гибкого обслуживания разнообразных потребностей. Общее число разновидностей CPLD оказывается очень большим. Для более подробного рассмотрения, выделим характерные CPLD из продукции ведущих фирм.

Классическими представителями CPLD являются микросхемы МАХ 7000, фирмы Altera, имеющие память конфигурации типа и EEPROM. Для "старых" CPLD небольшой сложности триггерная память конфигурации вообще не была характерной. В дальнейшем с освоением глубоко субмикронной технологии и многослойных металлизации положение изменилось, триггерная память конфигурации появилась и в CPLD, но, строго говоря, одновременно изменилась и их архитектура, так что соответствующие СБИС правильнее относить к СБИС ПЛ смешанной архитектуры (FLEX, APEX), рассматриваемым ниже.

CPLD МАХ 7000

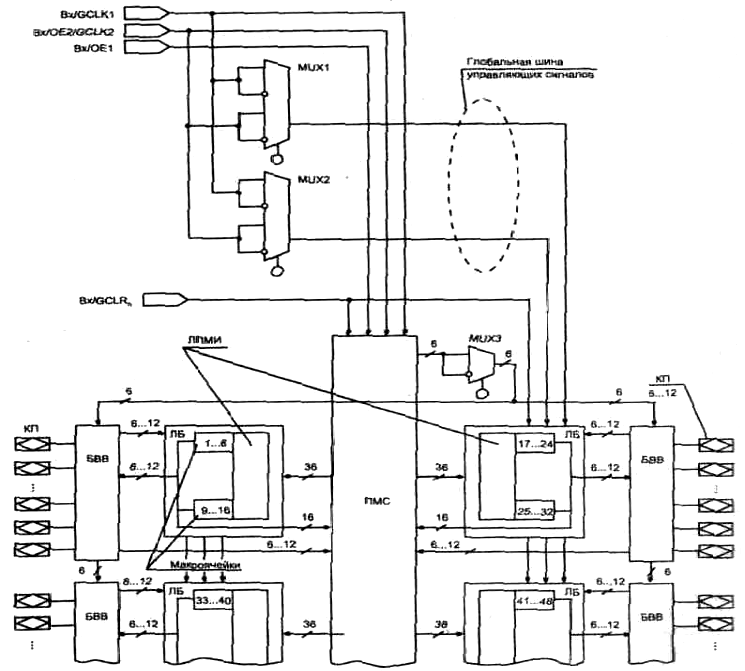

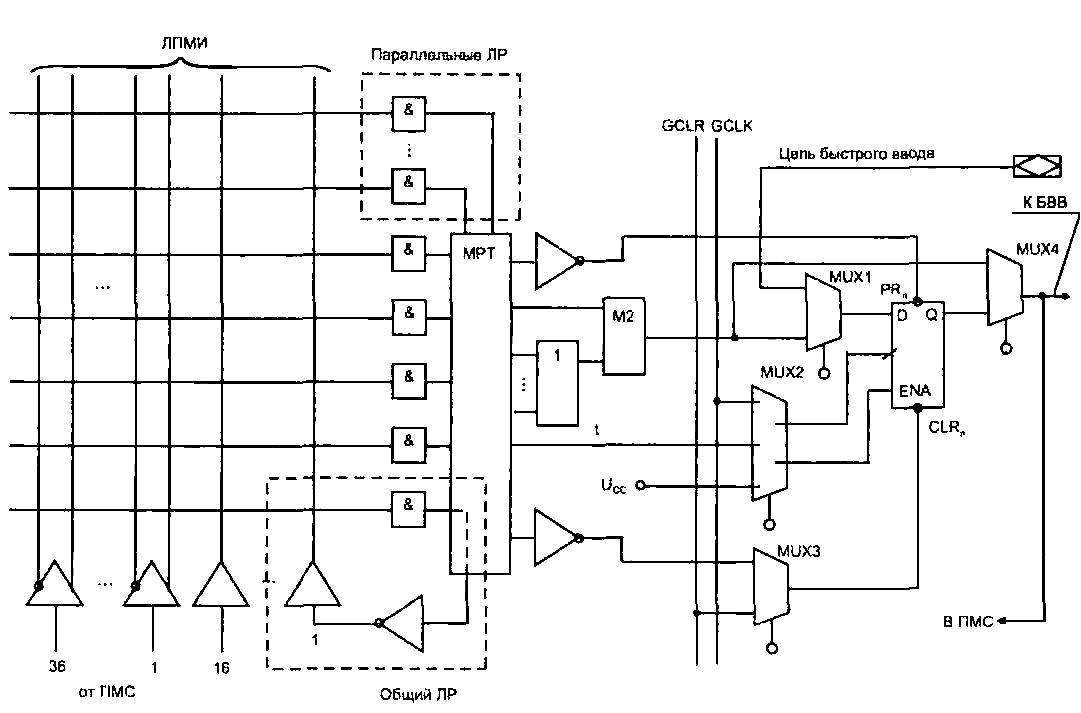

На рис. 2.14 показан фрагмент CPLD MAX 7000S, дающий достаточно полное представление о ней, т.к. структура CPLD в целом составляется повторением изображенного на фрагменте яруса из логических блоков ЛБ и блоков ввода/вывода БВВ то или иное число раз (на рис. 2.14 повторяющиеся ярусы должны располагаться сверху вниз) в зависимости от числа ЛБ у данной CPLD, т.е. от ее сложности. На рисунке выделены логические блоки ЛБ, содержащие по 16 макроячеек МЯ, получающих термы от локальных программируемых матриц И (ЛПМИ), программируемая матрица соединений ПМС и блоки ввода/вывода БВВ.

Микросхемы семейства МАХ 7000 имеют маркировку EPM7ХХХ, (усовершенствованные варианты отмечаются дополнительной буквой в конце), где в трех последних позициях размещается число МЯ у данной микросхемы (от 032 у младшего представителя до 256 у старшего).

Как и во всех СБИС ПЛ, логические операции производятся в ЛБ, которые соединяются в единую схему с помощью ПМС. Каждый ЛБ содержит 16 макроячеек, так что у младшего представителя семейства 2 логических блока, у старшего — 16.

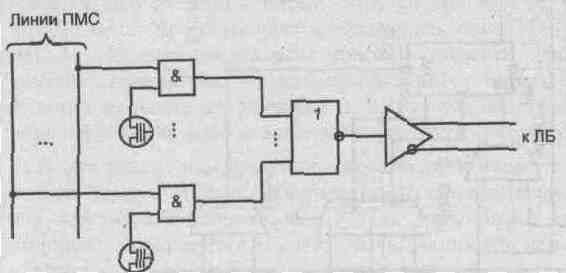

ПМС обеспечивает возможность подачи на любой вход ЛБ сигнала от любого источника (выходов ЛБ или контактов ввода/вывода), причем она организована так, что на пути сигнала нет программируемых ключей, и задержки сигналов малы. Подача сигнала из ПМС в ЛБ (рис. 2.15) происходит через конъюнктор, открытый по второму входу единичным логическим сигналом с помощью программируемого транзистора, который не находится в цепи передачи сигнала. На вход ЛБ можно передать сигнал с любой вертикальной линии ПМС. Вертикальные линии непрерывны и идут по всей длине между двумя столбцами из ЛБ.

Рис. 2.14. Фрагмент структуры CPLD MAX 7000S

Каждый ЛБ непосредственно связан со своим блоком ввода/вывода, имеющим от 6 до 12 контактов (КП — контактная площадка). Как видно, не все макроячейки могут иметь внешний вывод. Часть из них может быть использована только для подачи сигнала обратной связи в ПМС, что является естественным при построении ряда узлов (счетчиков и др.).

ПМС получает следующие сигналы: 16 сигналов обратной связи от каждого ЛБ, от 6, до 12 сигналов от БВВ, четыре сигнала (вверху на рис. 2.15) от специализированных входов. Разное число контактов у БВВ позволяет выбирать более экономичный вариант там, где требования интерфейса это допускают.

Рис. 2.15. Схема передачи сигналов из программируемой матрицы соединений в логические блоки

К специализированным сигналам относятся так называемые глобальные сигналы тактирования GCLK1 и GCLK2 и сброса GCLR, а также сигнал разрешения выходов ОЕ. Здесь и в других случаях термин "глобальный" означает "единый для всех одноименных блоков СБИС". При необходимости перечисленные линии могут быть использованы как простые входы ПМС.

Из ПМС поступает по 36 сигналов для каждого ЛБ и еще 6 сигналов, которые передаются в прямом или инверсном виде через мультиплексор MUX2 для глобальной шины разрешения выходов блока ввода/вывода.

Логический блок обеспечивает построение, как комбинационных цепей, так и схем с элементами памяти. Одна из макроячеек ЛБ показана на рис. 2.16. Из матрицы элементов И в матрицу распределения термов МРТ поступает основных термов (на рисунке слева). МРТ дает возможность использовать эти термы для сборки по ИЛИ с последующей подачей результата на элемент сложения по модулю 2 для образования комбинационной функции, а также для управления триггером по входам сброса (CLRn), установки (PRn). Терм t может быть использован для тактирования триггера или разрешения тактирования в зависимости от программирования мультиплексора MUX2.

Триггер может тактироваться от глобального сигнала GCLK с минимальной задержкой поступления сигнала синхронизации от общего входа микросхемы, что типично при реализации синхронных автоматов. Тактирование от глобального сигнала может сопровождаться индивидуальным управлением от сигнала разрешения тактирования ENA, что характерно для построения апериодических автоматов, и, наконец, возможно тактирование локальным сигналом от терма t, что соответствует асинхронным схемам.

Рис. 8.16. Схема макроячеек CPLD MAX 7000S

Имеются асинхронные сигналы установки и сброса PRn и CLRn, кроме того, сброс возможен и от глобального сигнала GCLR при соответствующем программировании мультиплексора MUX3.

Имеется возможность быстрой загрузки триггера от внешнего вывода по прямой цепи (программируется мультиплексором MUX1). В другом состоянии MUX1 передает на вход триггера значение функции, выработанное комбинационной частью макроячейки. Мультиплексор MUX4 позволяет подавать на выход макроячейки (к БВВ) либо непосредственно комбинационную функцию, либо хранящуюся в триггере (регистровый выход).

Если для реализации функции макроячейкой недостаточно числа ее собственных термов, можно воспользоваться дополнительно ресурсами двух типов логических расширителей ЛР. Так называемый общий (разделяемый) расширитель образуется за счет использования для него пятой линии термов макроячеек. Терм этой линии вводится в матрицу И и становится доступным (общим) для всех макроячеек. Так как в ЛБ 16 макроячеек, общий расширитель может иметь до 16 линий (рис. 2.16).

Рис.

2.17.

Схема

параллельного расширителя макроячеек

CPLD

MAX

7000S

Рис.

2.17.

Схема

параллельного расширителя макроячеек

CPLD

MAX

7000S

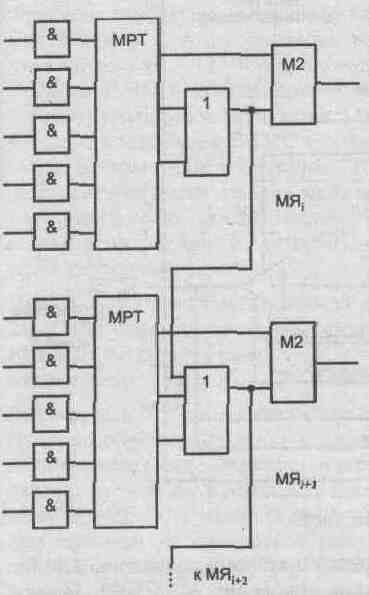

Логический расширитель, называемый параллельным, образуется за счет коммутации термов предшествующих макроячеек, которые передаются в последующие (рис. 2.17), так что макроячейки связываются в цепочку. Можно образовать цепочку, длина которой не превышает восьми звеньев. Понятно, что вследствие последовательного включения вентилей ИЛИ в выработку результата вносится дополнительная задержка.

Блок ввода/вывода (рис. 2.18) дает возможность гибкого управления разрешением выходного буфера. ПМС формирует шесть глобальных сигналов разрешения выхода ОЕ. Для некоторых представителей семейства МАХ 7000 имеется возможность программирования выхода как выхода с открытым коллектором (ОК.), кроме того, может программироваться и скорость изменения выходных сигналов с целью, указанной ранее (эта скорость связана с уровнем создаваемых помех). вые свойства: интерфейс JTAG, программирование в системе ISP без применения повышенных напряжений и др. Сведения о параметрах микросхем МАХ 7000 и МАХ 9000 приведены в табл. 2.2 § 2.5.

Развитие архитектур СБИС ПЛ идет по пути создания комбинированных структур, сочетающих достоинства FPGA и CPLD. Так, например, фирма Altera выпустила семейство FLEX 8000 (Flexible Logic Element MatriX) и позднее FLEX 10K с триггерной памятью конфигурации.

По архитектуре микросхемы типа FLEX занимают промежуточное положение между классическими вариантами CPLD и FPGA. Сохранив ряд качеств, предшествующих разработок CPLD, микросхемы FLEX в то же время имеют логические элементы табличного типа (LUT), их логические блоки расположены в виде матрицы, причем трассировочные каналы проходят горизонтально и вертикально между ЛБ, что характерно для FPGA. Одновременно с этим трассы в каналах не сегментированы, а непрерывны, что типично для CPLD и дает хорошую предсказуемость и малые величины задержек.

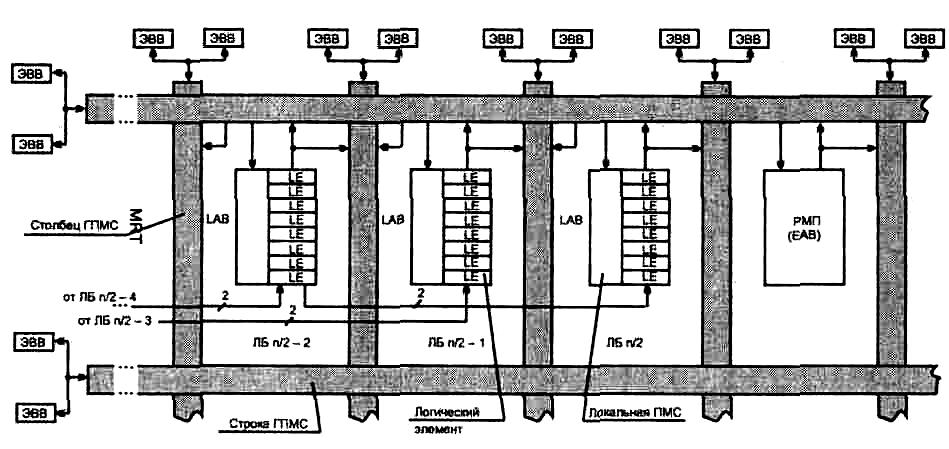

Микросхемы семейства FLEX 10K

Фрагмент структуры микросхем FLEX 10K, по которому можно судить о микросхеме в целом (остальные части являются повторением фрагмента), показан на рис. 2.19. Фрагмент содержит логические блоки, имеющие локальные ПМС и составленные из логических элементов ЛЭ (LE, Logic Element) табличного типа, строки и столбцы глобальной программируемой матрицы соединений ГПМС и элементы ввода/вывода ЭВВ, подсоединенные к концам строк и столбцов ГПМС. Кроме того, микросхема содержит реконфигурируемые модули памяти РМП (ЕАВ). Впервые такая встроенная память появилась в семействе FLEX 10K, до этого ресурсы памяти состояли в тех элементах, которые используются в логических преобразователях табличного типа.

Память может быть организована в вариантах 2048 х 1, 1024 х 2, 512 х 4 и 256 х 8 и ориентирована на реализацию буферов FIFO или (только для FLEX10KE) двухпортовых ОЗУ. Отдельные РМП могут объединяться для создания более емких блоков памяти.

В микросхемах FLEX реализовано двухуровневое разбиение средств логического преобразования данных. Наименьшей структурной единицей, выполняющей логические операции, является логический элемент (ЛЭ, LE). Компактная группа из восьми ЛЭ образует логический блок ЛБ (LAB, Logic Array Block). Логические блоки выступают как самостоятельные структурные единицы на следующем уровне иерархии. Все они расположены по строкам и столбцам, которым соответствуют строки и столбцы глобальной программируемой матрицы соединений ГПМС играют роль аргументов для ЛЭ, формирующего окончательный результат.

Рис. 2.19. Фрагмент структуры СБИС FLEX 10K

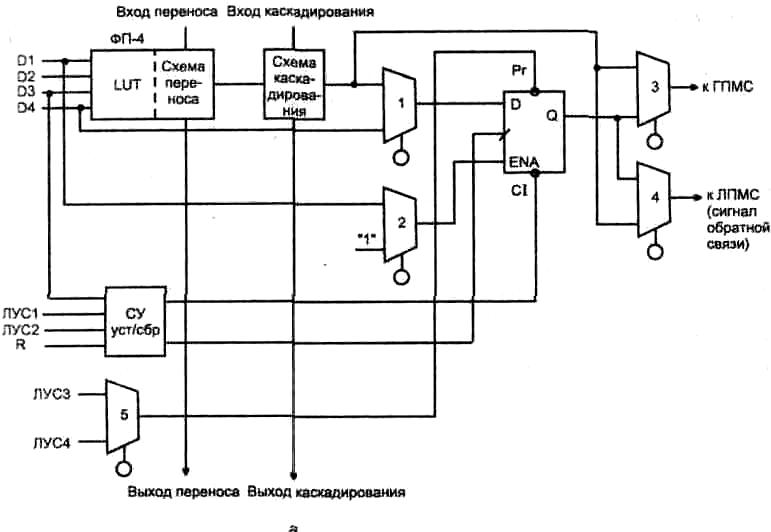

Логический элемент

Логический элемент (рис. 2.20, а) имеет четырехвходовой табличный функциональный преобразователь типа LUT (память емкостью 16 бит), схему переноса, схему каскадирования, программируемый триггер, схему управления сбросом/установкой триггера и несколько программируемых мультиплексоров. Функциональный преобразователь ФП-4 может также работать в режиме воспроизведения двух функций трех переменных (16 бит памяти в этом случае разбиваются на два блока по 8 бит), одна из которых — функция переноса, необходимая для таких схем, как счетчики или сумматоры с последовательными переносами или другие схемы с функциями переноса. В микросхемах FLEX удалось реализовать цепи переноса высокого быстродействия (с задержкой 1 нс на каскад), поэтому в библиотеке функциональных блоков немало рекомендованных структур с последовательным переносом, отличающихся схемной простотой.

Функциональный преобразователь реализует функции с малыми задержками. Синхронный триггер может функционировать как триггер D, Т, RS, JK. Входные сигналы асинхронных сброса и установки вырабатываются схемой управления, в которую поступают два локальных управляющих сигнала ЛУС1, ЛУС2, сигнал общего сброса СБИС и входная переменная D3. В схеме управления установкой/сбросом (СУ уст/сбр) имеются программируемые мультиплексоры, благодаря которым можно задать один из шести режимов воздействия на триггер. Все режимы асинхронные — это операции сброса, установки или загрузки в разных вариантах.

Триггер может быть использован совместно с комбинационной частью логического элемента или независимо, как отдельный элемент, если на его вход через мультиплексор 1 поступает сигнал со входа D4.

Выходные сигналы ЛЭ через мультиплексоры 3, 4 могут подаваться в глобальную и локальную программируемые матрицы соединений в программируемом комбинационном или регистровом варианте.

Тактирование триггера возможно от любого из двух локальных управляющих сигналов ЛУСЗ и ЛУС4.

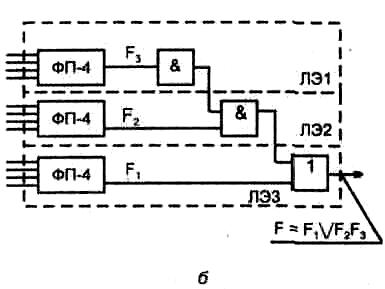

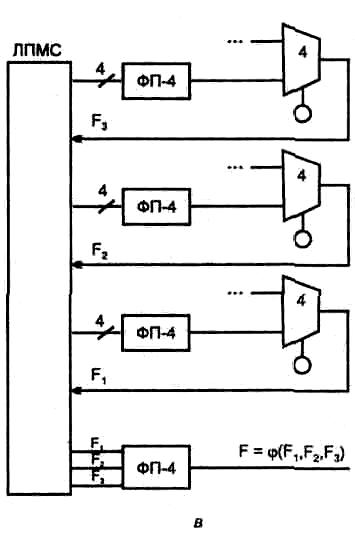

Функции более чем четырех аргументов могут быть получены двумя способами в виде композиций из функций 4-х переменных. Первый способ (рис. 2.20, б) предполагает использование схем каскадирования, имеющихся в каждом ЛЭ. Схему каскадирования можно настраивать на любую логическую операцию, кроме сложения по модулю 2 и равнозначности. С помощью схем каскадирования отдельные функции 4-х переменных объединяются в функцию большего числа аргументов. Второй способ, более обычный для СБИС ПЛ, использует схему с обратными связями (рис. 2.20, в), результатом при этом является получение "функции от функций". Вначале логическими элементами вырабатываются функции, зависящие от не более чем 4-х аргументов, а затем эти функции играют роль аргументов для ЛЭ, формирующего окончательный результат

Рис. 2.20. Схема логического элемента СБИС FLEX 10K (а) и схемы воспроизведения функций многих переменных (б, в)

Возможности обоих способов соответствуют возможностям декомпозиции воспроизводимых функций.

В СБИС семейства FLEX 10K впервые были включены встроенные реконфигурируемые матрицы памяти РМП (EABs, Embedded Array Blocks) с общей емкостью от приблизительно 6 Кбит до более чем 20 Кбит статической памяти. Такие блоки расположены в центре каждой строки матрицы логических блоков. В каждом блоке имеется 2048 программируемых битов памяти. Возможности блока не ограничиваются его использованием как блока памяти. Блок может быть и функциональным преобразователем табличного типа для получения сложных функций (в области цифровой обработки сигналов, арифметико-логических операций, интерфейсных функций и т. п.). Например, в одном блоке можно реализовать множительное устройство 4х4, способное работать на частотах до 50 МГц. Если же строить подобное устройство без применения EABs, то потребовалось бы занять 8 логических блоков LAB, и максимальная рабочая частота составила бы приблизительно 20 МГц.

Подробности устройства глобальной системы коммутации и работу элементов ввода/вывода рассматривать не будем. В них много сходства с работой схем аналогичного назначения, рассмотренных ранее. Основные параметры СБИС семейства FLEX 10K даны в табл. 2.3 §2.5.