- •Лекции Программируемые логические матрицы

- •1. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •§ 1.1. Вводные замечания

- •§ 1.2. Программируемые логические матрицы и программируемая матричная логика (плм и пмл)

- •Схемы с памятью

- •§ 1.3. Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

- •§ 2.2. Программируемые пользователем вентильные матрицы (fpga)

- •§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

- •§ 2.4. Сбис программируемой логики типа "система на кристалле"

- •2.5. Параметры и популярные семейства бис программируемой логики

- •§ 2.6. Интерфейс jtag. Периферийное сканирование. Программирование в системе (isp). Конфигурирование сбис пл

- •3. Методика и средства проектирования цифровых устройств

- •§ 3.1. Общие сведения

- •§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

$ 2.1. Общие сведения

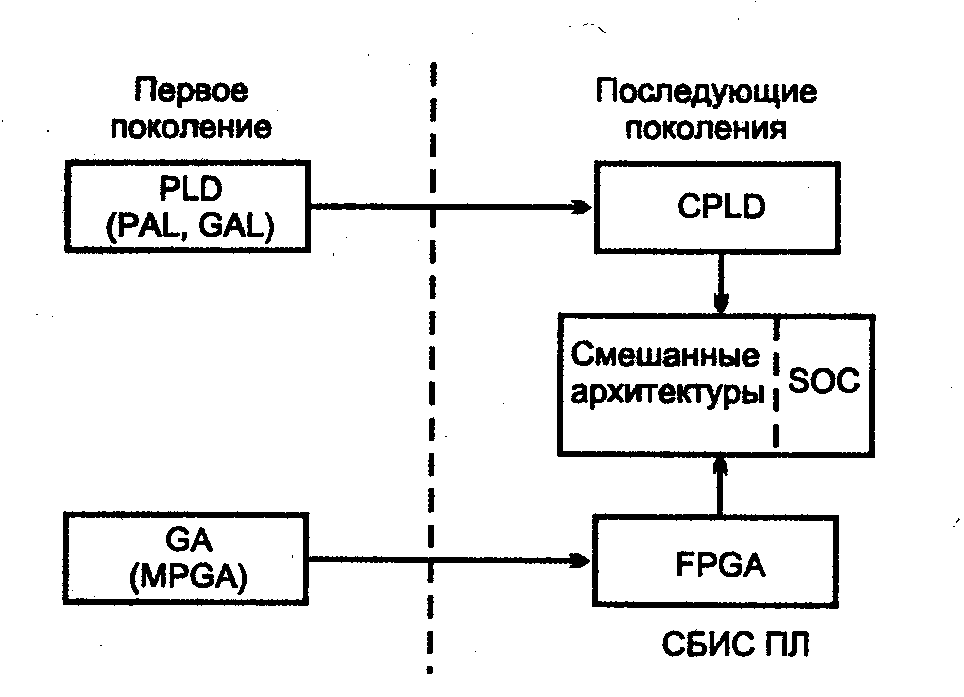

Микросхемы ПЛМ, ПМЛ и БМК, рассмотренные в гл.1, положили начало двум основным ветвям дальнейшего развития логических схем с программируемой и репрограммируемой структурами. Продолжением линии ПМЛ ста-то БИС/СБИС CPLD (Complex Programmable Logic Devices), а линии БМК— FPGA (Field Programmable Gate Arrays). Стремление объединить достоинства обеих линий привело к созданию БИС/СБИС смешанной (комбинированной) архитектуры, для которых еще не выработано общепринятое название (фирма Altera пользуется названием FLEX (Flexible Logic Element MatriX) — гибкие). Рост уровня интеграции дал возможность размещать на кристалле схемы, сложность которых соответствует целым системам. Эти схемы именуются SOC (Systems On Chip).

Сказанное иллюстрируется рис. 2.1, где под MPGA понимаются Mask Programmable GAs (вентильные матрицы с масочным программированием или БМК), а остальные термины уже объяснены.

Новизна темы, которой посвящена эта глава, сопровождается отсутствием установившейся терминологии, особенно в русскоязычной литературе, где иногда одни и те же термины обозначают разные вещи. Для некоторых терминов русские аналоги еще не определились. Ввиду сказанного ниже используются преимущественно английские термины и аббревиатуры, что, кстати говоря, характерно также для справочной литературы и документации САПР.

Общее название, объединяющее совокупность ИС, рассматриваемых в этой главе, т. е. "БИС/СБИС с программируемой (либо репрограммируемой) структурой" слишком громоздко, поэтому для краткости будем пользоваться обозначением "СБИС ПЛ" (СБИС программируемой логики), в котором не разделяются понятия БИС и СБИС (для нас это разделение несущественно) и не отражается однократность или многократность программируемости микросхемы.

Рис. 2.1. Взаимосвязь поколений СБИС программируемой логики

В разработке СБИС ПЛ участвуют уже десятки фирм, ведущими среди них являются Xilinx, Altera, Actel, Atmel, AMD (Vantis), Lattice (все США) и некоторые другие. Перечисленные фирмы достаточно полно представляют спектр продукции в области СБИС ПЛ, хотя и не исчерпывают ее. Последующее изложение темы ориентировано в основном на разработки фирм Xilinx, Altera и Actel.

Сфера применения СБИС ПЛ чрезвычайно широка, на них могут строиться не только крупные блоки систем, но и системы в целом, включая память и процессоры. Области

крупные блоки систем, но и системы в целом, включая память и процессоры. Области применения СБИС ПЛ уточняются в дальнейшем, предварительно отметим важность таких применений, как отработка прототипов систем при их проектировании, даже если конечная реализация систем рассчитана на другие средства, и создание малотиражных изделий быстрыми и эффективными способами.

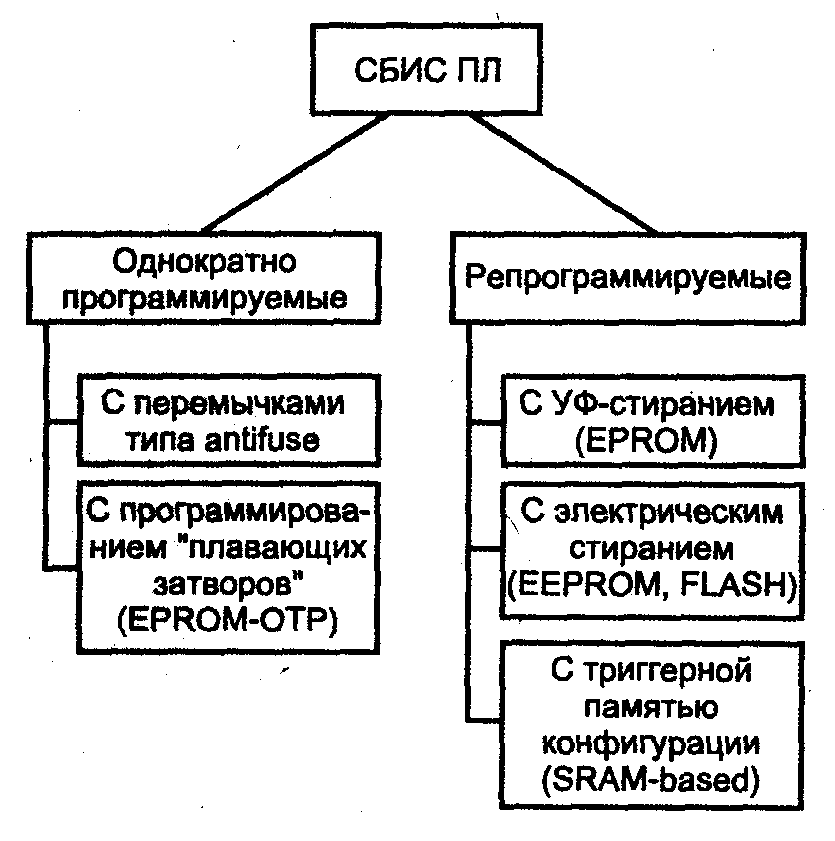

СБИС ПЛ классифицируются по нескольким признакам.

Классификация по конструктивно-технологическому типу программируемых элементов

Классификация СБИС ПЛ по конструктивно-технологическому типу показана на рис. 2.2. Программируемость, т. е. реализуемость конкретного проекта на стандартной СБИС, обеспечивается наличием в ней множества двухполюсников, проводимость которых может быть задана пользователемлибо очень малой (это соответствует разомкнутому ключу), либо достаточно большой (это соответствует замкнутому ключу). Состояния ключей задают ту или иную конфигурацию схеме, формируемой на кристалле. Число программируемых двухполюсников (программируемых точек связи ПТС) в СБИС ПЛ зависит от ее сложности и может доходить до нескольких миллионов. Для современных СБИС ПЛ характерны следующие виды программируемых ключей:

D перемычки типа antifuse (русский термин отсутствует);

О ЛИЗМОП транзисторы с двойным затвором (см. рис. 4.16, б и текст к нему);

О ключевые транзисторы, управляемые триггерами памяти конфигурации ЗУ ("теневым").

Рис.2.2. Классификация СБИС ПЛ по типу программируемых элементов

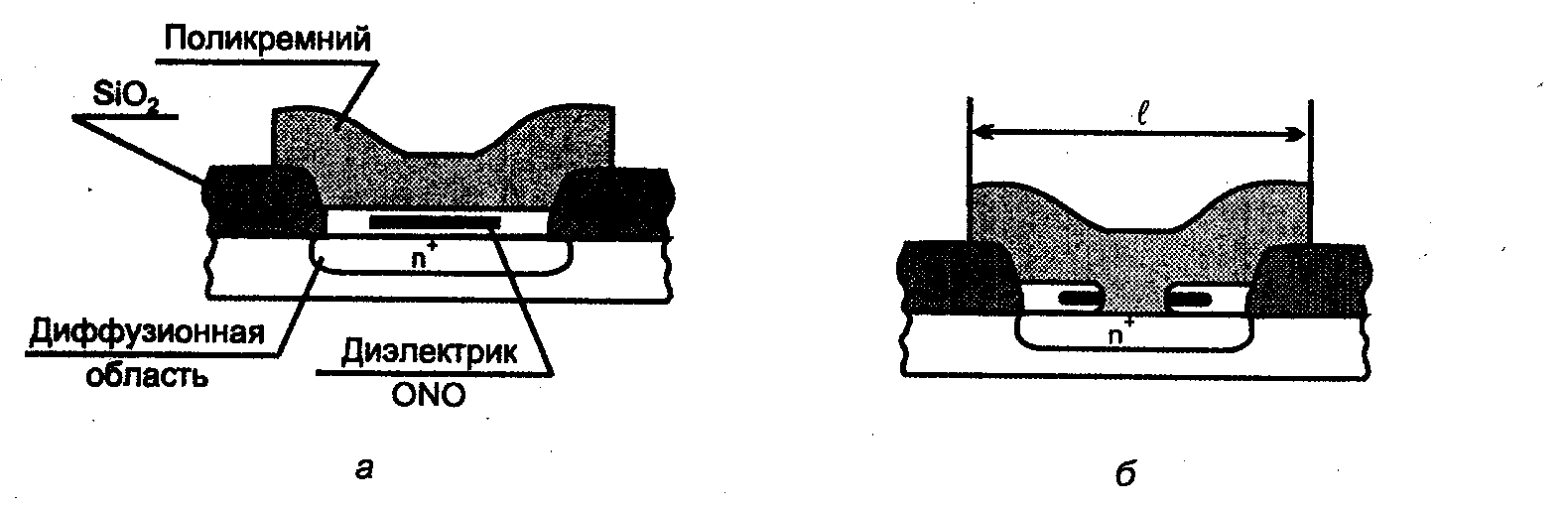

Программирование с помощью перемычек типа antifuse является однократным. Высококачественные перемычки фирмы Actel (рис. 2.3) компактны, имеют очень малые токи в первоначальном (непроводящем) состоянии (около одного фемтоампера, 1 фА=10e-15А). Перемычка образована трехслойным диэлектриком с чередованием слоев "оксид-нитрид-оксид". Соответственно чередованию слоев Oxid-Nitrid-Oxid перемычки также называют перемычками типа ONO.

Программирующий импульс напряжения пробивает перемычку и создает проводящий канал из поликремния между электродами (один электрод поликремниевый, другой — диффузионная область n+). Величина тока, создаваемого импульсом программирования, влияет на диаметр проводящего канала, что позволяет управлять параметрами проводящей перемычки (ток 5 mA создает перемычки со средним значением сопротивления 600 Ом, ток 15 mA — 100 Ом). Размер l зависит от топологической нормы применяемой технологии (близок к ней). Паразитная емкость перемычки для топологической нормы 1 мкм менее 10 фФ. Параметры обоих состояний перемычки должны сохраняться около 40 лет.

Рис. 2.3. Программируемые перемычки типа ONO до (а) и после (б) программирования

Элементы EPROM и EEPROM (Flash) на ЛИЗМОП транзисторах с плавающим затвором используются в схемах программируемой памяти и рассмотрены в гл. 4. Точно так же используются они и в СБИС ПЛ. Из элементов с УФ-стиранием выделился вариант вообще без возможности стирания данных — вариант EPROM-OTP (ОТР, One Time Programmable). Если в обычных EPROM стирание данных производится облучением кристалла через прозрачное

окошко в корпусе, то в схемах ОТР дорогостоящий корпус с окошком заменен на дешевый без окошка, т. е. возможность стирания исключается.

Не повторяя подробностей, напомним основные свойства элементов EPROM и EEPROM.

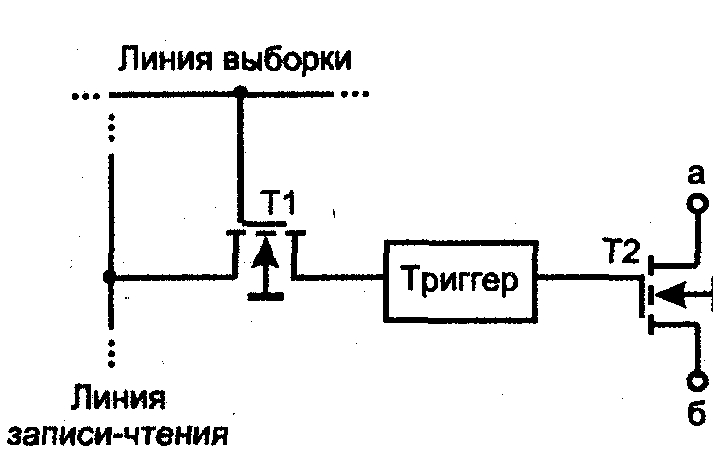

Репрограммируемые СБИС ПЛ на основе схемотехники EPROM требуют длительного (около часа) стирания старой конфигурации под воздействием ультрафиолетового излучения с извлечением СБИС из устройства и ограничением числа программирований из-за деградации свойств материалов под действием УФ-излучения. Память конфигурации с EEPROM, стираемая электрическими сигналами, для обновления не требует извлечения микросхемы из устройства, допускает достаточно большое число циклов стирания (10e4...10e6) стирание старой и запись новой информации занимают время порядка миллисекунд. В то же время площадь запоминающего элемента с электрическим стиранием вначале была приблизительно вдвое больше, чем площадь элемента с УФ-стиранием. В последнее время схемотехника EEPROM совершенствуется и все больше вытесняет схемотехнику EPROM. Транзисторный ключ, управляемый триггером памяти конфигурации, показан на рис. 2.4. Ключевой транзистор Т2 замыкает или размыкает участок ab в зависимости от состояния триггера, выход которого подключен к затвору транзистора Т2. При программировании на линию выборки подается высокий потенциал, и транзистор Т1 включается. С линии записи-чтения подается сигнал, устанавливающий триггер в состояние логической "1" или "О". В рабочем режиме транзистор Т1 заперт, триггер сохраняет неизменное состояние. Так как от триггера памяти конфигурации не требуется высокое быстродействие, он проектируется с оптимизацией по параметрам компактности и максимальной устойчивости стабильных состояний. Помехи в несколько вольт для такого триггера не влияют на его состояние. Схемы с триггерной памятью конфигурации (SRAM-based) впервые разработаны фирмой Xilinx.

Рис.

2.4.

Схема ключевого транзистора, управляемого

триггером памяти конфигурации

Рис.

2.4.

Схема ключевого транзистора, управляемого

триггером памяти конфигурации

Загрузка соответствующих данных в память конфигурации программирует СБИС ПЛ. Быстрый процесс оперативного программирования может производиться неограниченное число раз. В СБИС ПЛ с триггерной памятью конфигурация разрушается при каждом выключении питания. При включении питания необходим процесс программирования (инициализации, конфигурирования) схемы — загрузка данных конфигурации из какой-либо энергонезависимой памяти, что требует времени порядка десятков и даже сотен миллисекунд, если речь не идет о специальных СБИС ПЛ с так называемым динамическим оперативным репрограммированием.

Триггеры памяти конфигурации распределены по всему кристаллу СБИС вперемешку с элементами схемы, которые .они конфигурируют.

Ключевой транзистор Т2 (в английской терминологии pass-transistor) можно назвать программируемой точкой связи ПТС. В английской терминологии используется название Programmable Interconnection Point, сокращенно PIP.

Репрограммирование СБИС ПЛ с триггерной памятью конфигурации производится в том же режиме, что и рабочий режим, путем записи кодовой последовательности в цепочку триггеров. Стирание информации как специфический процесс воздействия на запоминающие элементы, требующий относительно длительных операций, вообще устранено. Несмотря на повышенную сложность запоминающего элемента и его энергозависимость в силу указанных и других (рассматриваемых ниже) достоинств, СБИС ПЛ с триггерной памятью конфигурации занимают важнейшее место в новых вариантах FPGA и CPLD.

Говоря об общих свойствах СБИС ПЛ, следует отметить, что благодаря регулярной структуре они реализуются с уровнем интеграции, близким к максимальному. Так как для средств программирования межсоединений требуются затраты дополнительной площади кристалла, СБИС ПЛ по уровню интеграции уступают БМК, но в последнее время все более успешно их догоняют.

В отличие от БМК, СБИС ПЛ выпускаются как полностью готовые, в них реализованы уже не только логические элементы, триггеры и т. п., но в межсоединения. Потребитель СБИС ПЛ не обращается к их изготовителю для выполнения каких-либо завершающих операций, т. к. программирование выполняет самостоятельно. Это дает основания отнести СБИС ПЛ к стандартной продукции, что сопровождается известными преимуществами — массовостью производства и снижением стоимости.

Как и при разработке других микросхем высшего уровня интеграции, в случае СБИС ПЛ большое внимание уделяется вопросам понижения потребляемой мощности. С ростом сложности СБИС потребляемая мощность становится наиболее критическим фактором. Так как мощность пропорциональна квадрату напряжения питания Ucc, его снижение дает значительный эффект. Если длительное время типовым напряжением питания микросхем и в том числе БИС/СБИС ПЛ было 5 В, то сейчас это могут быть напряжения 3,3 В; 2,7 В; 1,8 В и даже 1,5 В.

Поскольку передача сигналов низкого уровня по внешним связям неприемлема из-за малой помехоустойчивости таких сигналов, часто в СБИС используются два напряжения питания: повышенное для схем ввода/вывода данных и меньшее для питания основных логических схем и накопителей памяти. Соответственно этому для разных областей кристалла могут изготовляться транзисторы с разными пороговыми напряжениями.

Для быстродействующих низковольтных схем разрабатывается глубоко субмикронная технология КМОП и возрождается старая идея построения схем типа "кремний на диэлектрике" (SOI, Silicon On Insulator), в которых устранены многие паразитные схемные элементы. В схемах особо низковольтной логики достигается очень малая мощность элементов, например, 4,3 нВт/вентиль/МГц. При этом плотность упаковки такова, что достижима схемная сложность до 40 млн вентилей (около 100 млн транзисторов).

В схемах СБИС ПЛ нередко используется иерархия режимов понижения мощности.

В активных режимах часто при программировании используется так называемый Турбо-бит, с помощью которого выбирается один из двух режимов. Значение ON этого бита увеличивает скорость работы схемы при ограничении мощности допустимым значением. При состоянии OFF этот бит дает режим уменьшения мощности (со снижением скорости).

Для реализации режима с Турбо-битом используются специальные схемы выявления фактов изменения входных сигналов. Каждый вход снабжается несложной схемой, содержащей элементы ИЛИ, М2 и элемент задержки. Любое изменение входного сигнала выявляется и вызывает подачу на схему нормального питания, необходимого для быстрого протекания в ней процессов переключения. Затем автоматически питание схемы снижается, токи переходят на микроамперные уровни, и потребляемая мощность падает до начала новых переходных процессов из-за новых изменений входных сигналов.

Схема выявления перепадов входных сигналов увеличивает задержку на пути "вход-выход" СБИС на 30...40%. Программируемый Турбо-бит дает возможность пользователю предпочесть любой из вариантов работы схемы — более скоростной или более экономичный по потребляемой мощности. Турбо-бит включен в файл программирования СБИС.

Режим Standby Power (мощности в режиме ожидания) используется, когда все входные переменные сохраняют неизменные значения. При этом схема сохраняет готовность к переходу в рабочий режим. Могут применяться и режимы глубокого понижения мощности с очень малым уровнем ее потребления. В этих режимах схема сохраняет свое информационное состояние, но для перехода в рабочий режим с обычными параметрами быстродействия требуется определенное время.

Эффективность СБИС ПЛ стимулирует быстрый рост соответствующей отрасли промышленности и объемов их производства, а также научных исследований по развитию их архитектур, схемотехники, алгоритмов решения практических задач.