- •Лекции Программируемые логические матрицы

- •1. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •§ 1.1. Вводные замечания

- •§ 1.2. Программируемые логические матрицы и программируемая матричная логика (плм и пмл)

- •Схемы с памятью

- •§ 1.3. Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

- •§ 2.2. Программируемые пользователем вентильные матрицы (fpga)

- •§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

- •§ 2.4. Сбис программируемой логики типа "система на кристалле"

- •2.5. Параметры и популярные семейства бис программируемой логики

- •§ 2.6. Интерфейс jtag. Периферийное сканирование. Программирование в системе (isp). Конфигурирование сбис пл

- •3. Методика и средства проектирования цифровых устройств

- •§ 3.1. Общие сведения

- •§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

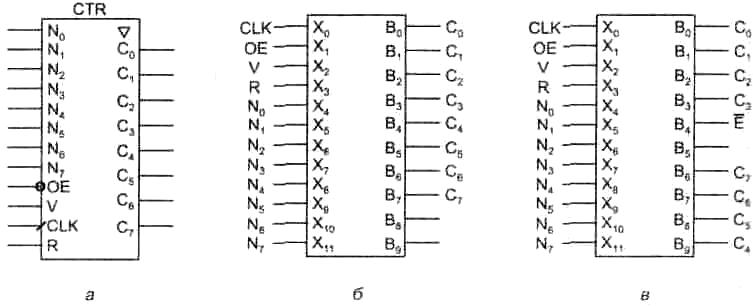

Пусть требуется спроектировать восьмиразрядный двоично-кодированный счетчик с управляемым модулем счета, величина которого задается восьмиразрядным входным кодом N. Такой счетчик считает входные сигналы от нулевого до N — 1, а при появлении N-го сигнала автоматически сбрасывается в ноль, после чего цикл повторяется снова. Счетчик должен иметь сигналы асинхронного сброса R, разрешения счета V (работать при V == 1), выдачи параллельного кода ОЕ и тактирования CLK. Внешняя организация счетчика приведена на рис. 3.4, а

Рис. 3.4. Внешняя организация проектируемого счетчика (а) и варианты распределения сигналов по контактам реализующей его микросхемы (б, в)

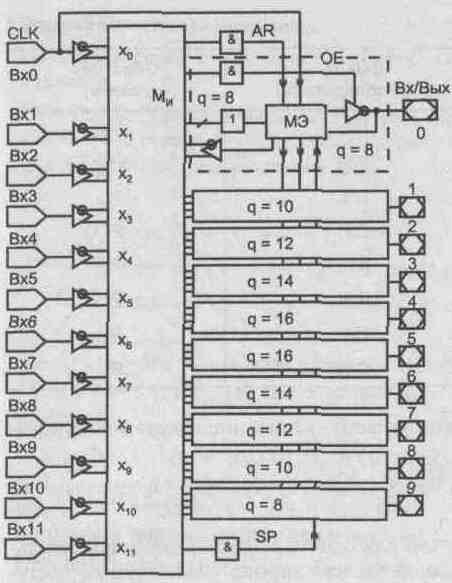

Средством реализации счетчика выбрана PLD 85C22V10 (рис. 3.5, а). Это быстродействующая PLD с десятью макроэлементами, имеющая тактовую частоту до 71,4 МГц при использовании обратных связей и 100 МГц при их отсутствии. В макроэлементы поступают от 5 до 16 термов. Кроме того, матрица И вырабатывает отдельные термы для сигналов разрешения буферов ОЕ. Общими для всей PLD являются термы выработки сигналов асинхронного сброса AR и синхронной установки SP. Наличие уровня логической единицы на выводе SP приведет к тому, что очередной тактовый импульс переведет все триггеры в состояние 1. При появлении единичного сигнала AR все триггеры немедленно сбросятся.

Микросхема имеет 12 специализированных входов и 10 двунаправленных выводов.

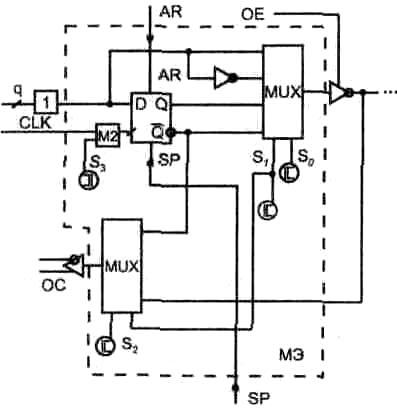

В схеме макроэлемента (рис. 3.5, б) вывод может быть запрограммирован как вход или как комбинационный либо регистровый выход с возможностью инвертирования выходных сигналов в зависимости от программирования мультиплексора "4—1" с помощью транзисторов ЛИЗМОП, обеспечивающих сигналы s0 и S1). Программируется также тип обратной связи с помощью мультиплексора "2—1", имеющего сложную схему управления, вырабатывающую окончательное значение адресующего сигнала как сумму по модулю два величин S1 и S2.

При программировании на режим комбинационного выхода сигнал обратной связи посылается в матрицу И с контакта Вх/Вых. При программировании регистрового выхода можно использовать сигнал обратной связи с выхода триггера или с контакта Вх/Вых.

Возможные конфигурации макроэлемента МЭ даны в табл. 3.1, где приняты обозначения: R — регистровый, С — комбинационный, Р — снимаемый -контакта Вх/Вых (от английского Pin), Н — Н-активный, L — L-активный.

а)

а)

б)

б)

Рис. 3.5. Структура PLD 85C22V10 (а) и схема макроэлемента этой PLD (б)

Таблица 3.1

S2 |

S1 |

S0 |

Выход (тип/полярность) |

Обратная связь |

0 |

0 |

1 |

R/H |

R |

0 |

1 |

0 |

C/L |

P |

0 |

1 |

1 |

C/H |

P |

1 |

0 |

0 |

R/L |

P |

1 |

0 |

1 |

R/H |

P |

1 |

1 |

0 |

C/L |

R |

1 |

1 |

1 |

C/H |

R |

Возможен выбор полярности тактирующего сигнала индивидуально для каждого МЭ.

Управление третьим состоянием буфера задается термами, получаемыми от матрицы И.

На рис. 3.5, а раскрыта схема только для одного выхода. Схемы для остальных выходов аналогичны показанной во всем, кроме числа термов, поступающих в МЭ из матрицы “И”. Число термов q для каждого выхода указано в прямоугольнике условного обозначения.

Первый этап проектирования

На первом этапе проектирования выясняется достаточность числа входов и выходов выбранной PLD для реализации проекта. Для этого производят предварительное распределение сигналов между контактами микросхемы. В данном случае, очевидно, что выходы счетчика должны быть определены на любых 8 из 10 контактов типа Вх/Вых. Наличие двух свободных контактов типа Вх/Вых создает возможность варьирования распределением оставшихся сигналов, т. к. их 12, а свободных контактов 14. Предпочтителен вариант, в котором контакты типа Вх/Вых остаются свободными, поскольку в случае необходимости реализации функций с числом термов больше 16 потребуется дополнительная логика и можно будет воспользоваться ресурсами свободных МЭ.

Входной сигнал CLK однозначно закрепляется за контактом xq, т. к. только с него подаются синхросигналы на триггеры МЭ. Таким образом, предварительный вариант распределения сигналов по контактам PLD приобретет вид (см. рис. 9.4, б).

Второй этап проектирования.

На втором этапе определяются функции возбуждения для всех 8 триггеров счетчика.

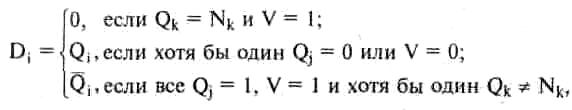

Счетчик должен сбрасываться при совпадении его содержимого с входным кодом N. Согласно логике работы счетчика, функции возбуждения триггеров могут быть представлены в виде:

где i, j, k == 0...7 — номера разрядов счетчика, причем j < i, a k — любое, Di — вход i-го триггера;

Отсюда:

![]()

где

![]() —

признак равенства содержимого счетчика

и входного управляющего слова.

—

признак равенства содержимого счетчика

и входного управляющего слова.

Преобразовав выражение для D, в ДНФ, получим

![]()

где

![]()

Как видно, число термов в функциях возбуждения зависит от номера разряда. Максимальное число 9 требуется для старшего разряда. Для следующих нужны 8, 7, 6 и т. д. термов.

Следовательно, функцию возбуждения старшего разряда нельзя получить с выходов 0 и 9, макроэлементы которых имеют по 8 термов.

Третий этап проектирования

На третьем этапе функции с большим числом термов, превышающим возможности выходных каналов PLD, которые не могут быть воспроизведены в ДНФ, разбиваются на подфункции. Реализовав подфункции на отдельных выходах, эти подфункции через цепи обратных связей вводят в матрицу И в качестве аргументов для формирования функции в целом (см. § 1.2). В нашем примере функций с неприемлемым для реализации в ДНФ числом гермов не оказалось. Заметим, что это благоприятное обстоятельство возникло из-за того, что в преобразованном выражении для D; не оказалось