- •Лекции Программируемые логические матрицы

- •1. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •§ 1.1. Вводные замечания

- •§ 1.2. Программируемые логические матрицы и программируемая матричная логика (плм и пмл)

- •Схемы с памятью

- •§ 1.3. Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •2. Современные и перспективные бис/сбис со сложными программируемыми и репрограммируемыми структурами (fpga, cpld, flex, soc и др.)

- •§ 2.2. Программируемые пользователем вентильные матрицы (fpga)

- •§ 8.3. Сложные программируемые логические схемы (cpld) и сбис программируемой логики смешанной архитектуры (flex и др.)

- •§ 2.4. Сбис программируемой логики типа "система на кристалле"

- •2.5. Параметры и популярные семейства бис программируемой логики

- •§ 2.6. Интерфейс jtag. Периферийное сканирование. Программирование в системе (isp). Конфигурирование сбис пл

- •3. Методика и средства проектирования цифровых устройств

- •§ 3.1. Общие сведения

- •§ 3.2. Пример "ручного" проектирования цифрового устройства с использованием программируемой матричной логики (пмл)

3. Методика и средства проектирования цифровых устройств

§ 3.1. Общие сведения

Проектирование — разработка технической документации, позволяющей изготовить заданное устройство в заданных условиях.

Сущность процесса проектирования удачно отражена в работе [10] следующим образом.

Стратегия проектирования — функциональная декомпозиция. Для системы в целом и ее блоков используется концепция "черного ящика". Для "черного ящика" разрабатывается функциональная спецификация, включающая внешнее описание блока (входы и выходы) и внутреннее описание — функцию или алгоритм работы: F = Ф (X, t), где Х — вектор входных величин;

F — вектор выходных величин; t — время. При декомпозиции функция Ф разбивается на более простые функции Ф1...Фк, между которыми должны быть установлены определенные связи, соответствующие принятому алгоритму реализации функции Ф. В результате разбиения в конечном счете получается структура. Переход от функции к структуре — синтез.

Синтез неоднозначен. Выбор наилучшего варианта осуществляется по результатам анализа, когда проверяется правильность работы и некоторые показатели, характеризующие устройство.

Декомпозиция функций блоков выполняется до тех пор, пока не получатся типовые функции, каждая из которых может быть реализована той или иной микросхемой.

Процесс проектирования — многошаговый и итерационный, с возвратами назад и пересмотром ранее принятых решений.

К этому наглядному описанию процесса проектирования следует добавить лишь, отражая возможности современной элементной базы, что декомпозиция заканчивается при получении типовых функций, соответствующих тем или иным микросхемам или элементам функциональных библиотек программируемых БИС/СБИС.

Характер проектирования существенно зависит от вида применяемой элементной базы.

Классификация цифровых ИС с точки зрения методов проектирования

Классификация цифровых ИС по признакам, связанным с методами их проектирования, приведена на рис. 3.1.

Рис. 3.1. Классификация цифровых ИС по признаку методов проектирования

К стандартным микросхемам отнесены схемы малой и средней степени интеграции МИС и СИС. Эти микросхемы производятся массовыми тиражами и реализуют стандартные элементы и узлы, функционирование которых никак не определяется конкретными потребителями. К стандартным схемам высокого уровня интеграции (БИС и СБИС) относятся микропроцессоры МП, микроконтроллеры МК и запоминающие устройства ЗУ, остающиеся неизменными после изготовления независимо от устройств и систем, в которых они используются. Стандартные ИС имеют обширный рынок, что благоприятно для снижения их стоимости.

К специализированным ИС (СпИС) относятся все, структура которых в отличие от структур стандартных ИС массового производства каким-либо способом приспосабливается к конкретным требованиям того или иного проекта. В английской терминологии СпИС именуются ASICs (Application Specific Integrated Circuits). Среди СпИС различают классы полузаказных и заказных. Разновидностями заказных микросхем являются полностью заказные и спроектированные методом "на стандартных ячейках".

Полностью заказные схемы целиком проектируются по требованиям конкретного заказчика. Проектировщик имеет полную свободу действий, определяя схему по своему усмотрению вплоть до уровня схемных компонентов (отдельных транзисторов и т. п.). Для изготовления схемы требуется разработка всего комплекта фотошаблонов, верификация и отладка всех схемных фрагментов. Такие схемы очень дороги и имеют длительные циклы проектирования.

Схемы на стандартных ячейках отличаются от полностью заказных тем, что их фрагменты берутся из заранее разработанной библиотеки схемных решений. Такие фрагменты уже хорошо отработаны, стоимость и длительность проектирования при этом снижаются. Для производства схем тоже требуется изготовление полного комплекта фотошаблонов, но разработка их облегчена. Потери сравнительно с полностью заказными ИС состоят в том, что проектировщик имеет меньше свободы в построении схемы, т. е. результаты оптимизации ее ло критериям площади кристалла, быстродействию и т. д. менее эффективны. Наивысших технических параметров добиваются от полностью заказных схем, однако метод стандартных ячеек популярен, т. к. при небольших потерях в технических характеристиках, с его помощью можно заметно упростить проектирование схемы. Полностью заказные схемы разрабатываются за время, превышающее время разработки методом стандартных ячеек приблизительно в два раза.

К полузаказным схемам относятся базовые матричные кристаллы БМК (в английской терминологии MPGA, Mask Programmable Gate Arrays). В этом случае имеется стандартный полуфабрикат, который доводится до готового изделия с помощью индивидуальных межсоединений. Реализация требует изготовления лишь малого числа фотошаблонов. Стоимость и длительность проектирования в сравнении с полностью заказными схемами сокращаются в 3...4 раза, но результат еще дальше от оптимального, поскольку в матричных БИС (МАБИС) менее рационально используется площадь кристалла (на кристалле остаются неиспользованные элементы и т. п.), длины связей не минимальны и быстродействие не максимально.

Сходство методов проектирования на БМК и стандартных ячейках состоит в использовании библиотек функциональных элементов. Различие в том, что для схем, проектируемых по методу стандартных ячеек, библиотечный набор элементов имеет более выраженную топологическую свободу. Например, стандартизируется только высота ячеек, а их длины могут быть различными. При проектировании вначале из набора библиотечных элементов подбираются необходимые функциональные блоки, а затем решаются задачи их размещения и трассировки.

САПР для проектирования по методу стандартных ячеек более сложны, чем для проектирования на основе БМК, которому свойственны более жесткие топологические ограничения. Ограничения вводятся и для метода стандартных ячеек (постоянство высоты ячеек, предопределенность геометрических размеров и положения шин питания, тактирования и др.), но по мере применения более мощных САПР ограничения ослабляются.

Длительность изготовления БИС/СБИС методом стандартных ячеек превышает этот же показатель для МАБИС на основе БМК в 1,3...1,8 раз.

Особое место в классификации занимают БИС/СБИС ПЛ. С одной стороны они относятся к СпИС, т. к. в конечном счете приспосабливаются к требованиям конкретного проекта. В то же время этот процесс (конфигурация схемы) не затрагивает изготовителя, для которого схемы являются стандартным продуктом со всеми вытекающими из этого выгодами.

По мнению специалистов, высказанному в журнале Electronic Design, "программируемая аппаратура произведет в ближайшие годы такой же переворот, как микрокомпьютеры в начале 70-х гг.".

Области применения СпИС различных типов

Все типы СпИС имеют свои области применения. Каждому типу свойственно определенное соотношение таких параметров как сложность (достижимый уровень интеграции), быстродействие, стоимость. На выбор типа СпИС для реализации проекта влияет совокупность свойств. Основные соображения можно пояснить с позиций экономики, обратившись к формуле стоимости ИС, изготовляемой уже освоенным технологическим процессом:

Сис=Сизг+Спр/N,

где Сизг — стоимость изготовления ИС (стоимость кристалла и других материалов, стоимость технологических операций по изготовлению ИС, контрольных испытаний). Затраты на изготовление относятся к каждой ИС, т. е. повторяются столько раз, сколько ИС будет произведено; Спр — стоимость проектирования ИС, т. е. однократные затраты для данного типа ИС. N — объем производства (тиражность), т. е. число ИС, которое будет произведено.

Стоимость проектирования БИС/СБИС велика и может достигать сотен миллионов долларов. Для дорогостоящих вариантов проектирования БИС/СБИС производство становится рентабельным только при большом объеме их продаж.

Затраты Спр и Сизг — находятся во взаимосвязи. Рост затрат на проектирование, как правило, ведет к снижению Сизг поскольку чем совершеннее проект, тем рациональнее используется площадь кристалла и другие его ресурсы. Отсюда видно, что выигрыш по экономичности могут получать те или иные типы СпИС в зависимости от тиражности их производства N и сложности.

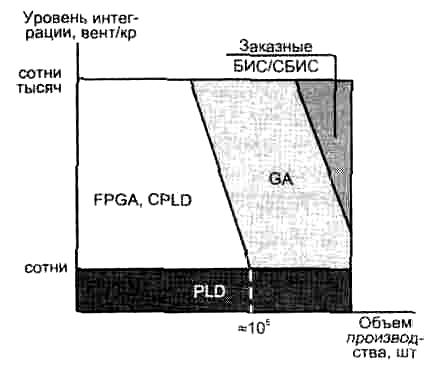

Применительно к микросхемам программируемой логики справедливы следующие положения. Простые устройства, со сложностью в сотни эквивалентных вентилей, целесообразно реализовывать на PLD (PAL, GAL, PLA).

При росте сложности проекта естественен переход к FPGA и CPLD, если тиражность ИС сравнительно невелика. Рост тиражности (приблизительно свыше десятков тысяч) ведет к преимуществам реализации на БМК, т. к. стоимость изготовления небольшого числа шаблонов для создания межсоединений разложится на большое число микросхем, а стоимость изготовления каждой ИС уменьшится благодаря исключению из схемы схем программируемых связей и средств их программирования.

При еще большей тиражности выгодным оказывается метод стандартных ячеек, позволяющий дополнительно улучшить параметры схемы, плотнее разместить ее элементы на кристалле, т. е. уменьшить Сизг и улучшить быстродействие. При этом слагаемое Спр/N в формуле стоимости ИС не окажется слишком большим благодаря большой величине N, хотя необходимость проектировать весь комплект шаблонов для технологических процессов приводит к большим затратам Спр.

Полностью заказное проектирование для СпИС не характерно. Оно стоит настолько дорого, что применяется практически только для создания стандартных БИС/СБИС массового производства. Например, проектирование первого 32-разрядного микропроцессора обошлось в свое время в 140 млн. долларов, а ЗУ емкостью в 1 Мбит — в 395 млн. долларов.

Диаграмма областей целесообразного применения разных типов СпИС в зависимости от их сложности и тиражности, приведена на рис. 3.2.

Рис.

3.2.

Диаграмма областей целесообразного

применения различных типов специализированных

БИС/СБИС

Рис.

3.2.

Диаграмма областей целесообразного

применения различных типов специализированных

БИС/СБИС

Интересно отметить, что ведущая компьютерная фирма IBM использует методологию проектирования смешанного типа БМК/СЯ (Gate-Array/Standard Cell Intermix), размещая в одной СБИС области, выполненные по методу стандартных ячеек СЯ и по методу БМК. Более плотные и быстродействующие схемы типа СЯ используются в критических трактах обработки сигналов, остальная площадь занимается транзисторами БМК.

Проектирование стандартных ИС массового производства, как и проектирование заказными методами вообще, — удел крупных специализированных фирм. На долю системотехников приходятся главным образом другие разработки: цифровых устройств малой сложности на МИС и СИС, микропроцессорных систем для целей управления техническими объектами и технологическими процессами, малотиражной аппаратуры либо прототипов систем на основе ИС программируемой логики.

Проектирование на основе МИС, СИС — наиболее традиционный процесс, в котором используются как эвристические подходы, так и формализованные методики. Проектировщик задает структуру устройства на базе своих знаний, идей и освоения опыта предшественников, а при определении функций отдельных блоков пользуется и формальными методами. Требуется знание типовых функциональных узлов, их свойств и параметров. Соответствующий материал изложен в кн. в гл. 1, 2 и 3.

Микропроцессорная система создается в результате разработки 'комплекса программно-аппаратных средств. Разработка аппаратной части сводится к компоновке системы из типовых модулей: центрального процессорного элемента, различных видов памяти, адаптеров, контроллеров и внешних устройств. Способы подключения модулей к шинам микропроцессорной системы, описания основных модулей, сведения о методике их программирования и применения приведены в кн. в гл. 4, 5 и 6.

Львиной долей инженерных разработок аппаратуры в условиях современной России, по-видимому, явится использование программируемой логики для создания требуемых устройств и/или их отладки. Этому вопросу следует уделить дополнительное внимание.

Проектирование на основе схем программируемой логики высокой сложности выполняется только с помощью систем автоматизированного проектирования САПР. Укрупненная структура алгоритмов проектирования показана на рис. 3.3.

Проектирование на концептуальном уровне возлагается на проектировщика и слабо связано с автоматизацией. На этом уровне по существу определяется требуемое функционирование устройства, множества входных и выходных сигналов, их характер и взаимосвязь, разбиение проекта на части и т. д. Результаты концептуального синтеза вводятся в САПР, которая производит компиляцию проекта, т. е. синтезирует устройство в базисе библиотеки своих моделей. Полученный проект требует тщательной проверки, поэтому за этапом синтеза следует этап анализа, проводимого моделированием и теоретической верификацией. Моделирование имеет несколько уровней с разной степенью отображения свойств реального объекта. Оно может быть функциональным, проверяющим правильность логической структуры устройства, временным, учитывающим задержки сигналов в схемах устройства без учета окончательной топологии трассировки, и т. д. В результате моделирования могут выявиться ошибки, требующие исправления, что придает процессу проектирования итеративный характер с возвратами к прежним этапам и введением в проект нужных коррекций.

Рис.

3.3.

Укрупненная

структура алгоритмов автоматизированного

проектирования цифровых устройств на

основе микросхем программируемой логики

Рис.

3.3.

Укрупненная

структура алгоритмов автоматизированного

проектирования цифровых устройств на

основе микросхем программируемой логики

Далее производится конфигурирование микросхемы программируемой логики, после чего возможна реальная проверка работы устройства — физическое моделирование проекта. При успешном завершении физического моделирования устройство готово к установке в систему.