- •Основные классы вычислительных машин и их сравнительная характеристика.

- •Принципы работы вычислительных машин. Принципы фон-неймановской концепции вычислительной машины.

- •Структура фон-неймановской вычислительной машины.

- •Структуры вычислительных машин: с непосредственными связями, на основе шины.

- •Принципы построения микропроцессорных систем.

- •Определение микро-эвм. Классификация микро-эвм. Основные технические характеристики пэвм.

- •Обобщенная структурная схема микро-эвм, модульность конструкции микро-эвм.

- •Структуры микро-эвм с изолированными и мультиплексированными шинами. Системная магистраль микро-эвм.

- •Системная магистраль микро-эвм. Интерфейсы микро-эвм. Назначение контроллеров и адаптеров периферийных устройств.

- •Назначение и функции мп. Основные технические характеристики мп.

- •Классификация мп.

- •Архитектура микропроцессора: архитектура со сложной системой команд (cisc-процессоры), архитектура с упрощенной системой команд (risc-процессоры). Неймановская и гарвардская архитектуры

- •Обобщенная структурная схема однокристального мп.

- •Алу мп. Назначение, функции, основные технические характеристики.

- •Устройство управления мп. Понятия микропрограмм, микрокоманд и микроопераций.

- •Понятие о системе команд микропроцессоров. Основные группы команд.

- •Способы адресации операндов в микропроцессорах

- •Модуль процессора микропроцессорной системы. Состав модуля – операционный блок, блок управления, интерфейсный блок. Выполняемые функции

- •Программно-доступные регистры микропроцессора

- •Сегментные регистры (cs, ds, ss, es),

- •Регистр адреса командIp,

- •Регистр флагов f.

- •Регистр флагов (признаков) мп

- •Сегментная организация памяти мп. Сегментные регистры и сегменты.

- •Общие сведения о системе прерываний мп.

- •Классификация типов прерываний мп. Механизм обработки прерываний.

- •Аппаратные прерывания

- •Программные прерывания

- •Исключительные ситуации

- •Регистровая структура 32-разрядного мп.

- •Типы данных 32-разрядных мп.

- •Отличительные особенности архитектуры 32-разрядного мп.

- •Структура микропроцессорной системы и основные режимы ее работы – выполнение основной программы, обслуживание прерываний, прямой доступ к памяти

- •Иерархическая организация памяти микро-эвм.

- •Система ввода-вывода микроЭвм. Общие принципы построения систем ввода-вывода. Организация обмена информацией с периферийными устройствами

битовая строка - упорядоченная последовательность разрядов, которая может начинаться с любого разряда любого байта и содержать до 4Гбит.

Отрицательные числа хранятся в памяти в дополнительном коде.

Форматы данных математического сопроцессора (FPU):

одинарная точность

31

30

23

22

0

знак

порядок

мантисса

двойная точность

63

62

52

51

0

знак

порядок

мантисса

повышенная точность

-

79

78

64

63

0

знак

порядок

мантисса

При обращении к оперативной памяти 32-разрядные микропроцессоры используют указатели:

«близкий» указатель – это 32-разрядный логический адрес, являющийся смещением внутри сегмента,

«дальний» указатель – это 48-разрядный логический адрес, состоящий из 16-разрядного селектора сегмента и 32-разрядного смещения.

Отличительные особенности архитектуры 32-разрядного мп.

Все 32-разрядные процессоры могут работать в двух режимах: реальном и защищенном. Основные архитектурные особенности микропроцессора:

в архитектуре применено RISC-ядро, позволяющее наиболее часто встречающиеся инструкции выполнять за 1 такт;

наличие встроенного арифметического сопроцессора;

наличие внутренней кэш-памяти и предусмотрены все необходимые средства для построения памяти с двухуровневым кэшированием;

увеличена очередь команд до 16 байт;

ускорено выполнение операций как в целочисленном АЛУ, так и в блоке арифметического сопроцессора;

используется умножение тактовой частоты системной платы (с увеличенной частотой работают только внутренние схемы микропроцессора, все внешние по отношению к микропроцессору схемы, в том числе расположенные и на системной плате, работают с обычной частотой).

Концепция RISC-микропроцессора сводится к следующим положениям:

выполнение всех (или, по крайней мере, 75% команд) за один цикл;

стандартная длина всех команд;

малое число команд;

малое количество форматов команд;

малое число способов адресации (преимущественно регистровая и непосредственная);

все команды, за исключением «Чтения» и «Записи», используют внутрипроцессорные межрегистровые пересылки;

относительно большой процессорный файл РОН.

В состав структурной схемы микропроцессора входят

целочисленное устройство,

устройство с плавающей точкой,

устройство управления,

диспетчер памяти,

устройство команд,

кэш-память,

шинное устройство.

В состав целочисленного устройства входят АЛУ, 32-разрядные РОН и многоразрядный сдвигатель, используемый при арифметических и циклических сдвигах, операциях умножения и деления. Команды сложения, вычитания, сдвига и логические операции выполняются за один такт. Содержимое РОН используется устройством сегментации для формирования адресов.

Устройство с плавающей точкой по структуре и программному обеспечению соответствует математическому сопроцессору.

Диспетчер памяти состоит из устройства сегментации и страничного преобразования и обеспечивает двухступенчатое формирование физического адреса ячейки памяти сначала в пределах сегмента, а затем в пределах страницы. Диспетчер поддерживает реальный и защищенный режимы работы микропроцессора.

Шинное устройство поддерживает обмен микропроцессора с памятью, контроллерами ввода-вывода и другими активными внешними устройствами.

Схемы управления имеют два типа выводов:

сигналы управления циклами магистрали,

сигналы управления состоянием микропроцессора и взаимодействием микропроцессора с другими активными устройствами магистрали.

Микропроцессор имеет внутреннюю кэш-память, единую для команд и данных. Кэш-память представляет собой быстродействующую память ограниченного объема, в которой хранятся копии последних считанных команд и операндов. Когда микропроцессор обращается за командой или данными, то сначала производится поиск требуемой информации в кэш-памяти. При отсутствии необходимой информации в кэш-памяти производится обращение к оперативной памяти и одновременная запись в кэш-память. При записи соответствие содержимого оперативной и кэш-памяти достигается с помощью механизмов сквозной записи. При сквозной записи осуществляется одновременное изменение содержимого как кэш-памяти, так и оперативной памяти.

Устройство команд содержит блок предвыборки для создания очереди команд, готовых к выполнению, и дешифратор команд. Блок предвыборки позволяет с опережением получить команды из памяти перед их фактическим исполнением. Дешифратор команд получает команды от блока предвыборки и преобразует их в управляющие сигналы. В дешифраторе одновременно обрабатываются коды операций, байты адресации и смещения. Выходные сигналы дешифратора определяют аппаратные микрокоманды для устройства сегментации, целочисленного устройства и устройства с плавающей точкой.

Блок микропрограммного управления формирует управляющие микропрограммы.

Структура микропроцессорной системы и основные режимы ее работы – выполнение основной программы, обслуживание прерываний, прямой доступ к памяти

Практически любая развитая микропроцессорная система (поддерживает три основных режима обмена по магистрали:

программный обмен информацией;

обмен с использованием прерываний;

обмен с использованием прямого доступа к памяти (ПДП).

Программный обмен информацией является основным в любой микропроцессорной системе. Он предусмотрен всегда, без него невозможны другие режимы обмена. В этом режиме процессор является единоличным хозяином системной магистрали. Все операции (циклы) обмена информацией в данном случае инициируются только процессором, все они выполняются строго в порядке, предписанном исполняемой программой.

Процессор читает (выбирает) из памяти коды команд и исполняет их, читая данные из памяти или из устройства ввода/вывода, обрабатывая их, записывая данные в память или передавая их в устройство ввода/вывода. Путь процессора по программе может быть линейным, циклическим, может содержать переходы (прыжки), но он всегда непрерывен и полностью находится под контролем процессора. Ни на какие внешние события, не связанные с программой, процессор не реагирует. Все сигналы на магистрали в данном случае контролируются процессором.

Обмен по прерываниям используется тогда, когда необходима реакция микропроцессорной системы на какое-то внешнее событие, на приход внешнего сигнала. В случае компьютера внешним событием может быть, например, нажатие на клавишу клавиатуры или приход по локальной сети пакета данных. Компьютер должен реагировать на это, соответственно, выводом символа на экран или же чтением и обработкой принятого по сети пакета.

В общем случае организовать реакцию на внешнее событие можно тремя различными путями:

с помощью постоянного программного контроля факта наступления события (так называемый метод опроса флага);

с помощью прерывания, то есть насильственного перевода процессора с выполнения текущей программы на выполнение экстренно необходимой программы;

с помощью прямого доступа к памяти, то есть без участия процессора при его отключении от системной магистрали.

Первый случай с опросом флага реализуется в микропроцессорной системе постоянным чтением информации процессором из устройства ввода/вывода, связанного с тем внешним устройством, на поведение которого необходимо срочно реагировать.

Во втором случае в режиме прерывания процессор, получив запрос прерывания от внешнего устройства, заканчивает выполнение текущей команды и переходит к программе обработки прерывания. Закончив выполнение программы обработки прерывания, он возвращается к прерванной программе с той точки, где его прервали.

Здесь важно то, что вся работа, как и в случае программного режима, осуществляется самим процессором, внешнее событие просто временно отвлекает его.

Естественно, никакого ускорения работы системы прерывание не дает. Его применение позволяет только отказаться от постоянного опроса флага внешнего события и временно, до наступления внешнего события, занять процессор выполнением каких-то других задач.

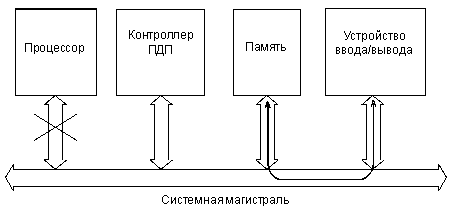

Прямой доступ к памяти (ПДП) — это режим, принципиально отличающийся от двух ранее рассмотренных режимов тем, что обмен по системной шине идет без участия процессора. Внешнее устройство, требующее обслуживания, сигнализирует процессору, что режим ПДП необходим, в ответ на это процессор заканчивает выполнение текущей команды и отключается от всех шин, сигнализируя запросившему устройству, что обмен в режиме ПДП можно начинать.

Операция ПДП сводится к пересылке информации из устройства ввода/вывода в память или же из памяти в устройство ввода/вывода. Когда пересылка информации будет закончена, процессор вновь возвращается к прерванной программе, продолжая ее с той точки, где его прервали. Это похоже на режим обслуживания прерываний, но в данном случае процессор не участвует в обмене.

Понятно, что в этом случае требуется введение в систему дополнительного устройства (контроллера ПДП), которое будет осуществлять полноценный обмен по системной магистрали без всякого участия процессора. Причем процессор предварительно должен сообщить этому контроллеру ПДП, откуда ему следует брать информацию и/или куда ее следует помещать. Контроллер ПДП может считаться специализированным процессором, который отличается тем, что сам не участвует в обмене, не принимает в себя информацию и не выдает ее.

Рисунок - Информационные потоки в режиме ПДП.

В принципе контроллер ПДП может входить в состав устройства ввода/вывода, которому необходим режим ПДП или даже в состав нескольких устройств ввода/вывода.

Иерархическая организация памяти микро-эвм.

Система памяти является функциональной частью микроЭВМ, предназначенной для записи, хранения и выдачи информации.

Рисунок – Типы памяти в микроЭВМ

Память имеет иерархическую (многоуровневую) структуру. В микроЭВМ выделяют следующие уровни памяти:

Сверхоперативное запоминающее устройство, или регистровая память микропроцессора представляет собой совокупность регистров общего назначения микропроцессора. Операции с этим типом памяти являются наиболее быстродействующими.

Внутренняя кэш-память – это оперативное запоминающее устройство, встроенное непосредственно в микропроцессор. Внутренняя кэш-память работает на тактовой частоте микропроцессора.

Внешняя кэш-память предназначена для уменьшения количества обращений к другим менее быстродействующим устройствам памяти, устанавливается на системной плате и работает на частоте шины.

Оперативная память предназначена для хранения информации (программ и данных), непосредственно участвующей в вычислительном процессе в текущий интервал времени. Оперативная память используется для оперативного обмена информацией между микропроцессором, внешней памятью и периферийными подсистемами.

Постоянное ЗУ используется для хранения таблиц, констант, кодов команд программ, стандартных подпрограмм, например подпрограмм BIOS, DOS.

Внешнее ЗУ используется для длительного хранения больших объемов информации.

По месту расположения ЗУ разделяют на процессорные, внутренние и внешние. Наиболее скоростные виды памяти (регистры, кэш-память первого уровня) обычно размещают на общем кристалле с центральным микропроцессором, а регистры общего назначения считаются частью микропроцессора. Внутреннюю память образуют ЗУ, расположенные на системной плате. К внутренней памяти относят оперативную память, а также кэш-память второго и последующего уровней (кэш-память второго уровня может также размещаться на кристалле микропроцессора). Медленные ЗУ большой емкости называют внешней памятью, так как к ядру микроЭВМ они подключаются аналогично устройствам ввода-вывода.

Запоминающие устройства характеризуются следующими основными параметрами:

Разрядность данных (определяется разрядностью ячейки памяти),

Информационная емкость (определяется количеством бит или байт информации, которое может храниться в ЗУ),

Быстродействие ЗУ. Для количественной оценки быстродействия используют три параметра:время доступа, время обращения, скорость передачи.

Система ввода-вывода микроЭвм. Общие принципы построения систем ввода-вывода. Организация обмена информацией с периферийными устройствами

Система ввода-вывода (СВВ) предназначена для выполнения следующих функций:

ввод,

вывод,

долговременное хранение информации,

обработка информации,

управление этой обработкой.

В состав системы ввода-вывода входят:

периферийные устройства,

контроллеры (адаптеры) периферийных устройств, отвечающие за управление периферийными устройствами и обмен между ними и ядром ЭВМ,

системные шины и их контроллеры,

интерфейсы,

контроллеры прерываний и прямого доступа к памяти (ПДП).

Структура систем ввода-вывода представляет собой совокупность взаимосвязанных внутренних и внешних интерфейсов (шин), посредством которых все устройства (модули) объединены в единую систему, называемую компьютером. Причем каждая шина имеет определенную скорость передачи информации, и к ней подсоединяются устройства с соответствующим быстродействием. Все шины, как правило, могут работать параллельно, обеспечивая высокую производительность вычислительной системы. Шины соединяются между собой с помощью специальных устройств – мостов. Кроме того, в структуру систем ввода-вывода входят устройства управления шинами и схемы организации процессов передачи информации при различных режимах ввода-вывода.

В ЭВМ применяются три режима ввода/вывода:

программно-управляемый ввод-вывод (называемый также программным вводом-выводом),

ввод-вывод по прерываниям,

прямой доступ к памяти (ПДП).

Первый из них характеризуется тем, что инициирование и управление вводом-выводом осуществляется программой, выполняемой процессором, а внешние устройства играют сравнительно пассивную роль и сигнализируют только о своем состоянии, в частности, о готовности к операциям ввода/вывода. Во втором режиме ввод-вывод инициируется не процессором, а внешним устройством, генерирующим специальный сигнал прерывания. Реагируя на этот сигнал готовности устройства к передаче данных, процессор передает управление подпрограмме обслуживания устройства, вызвавшего прерывание. Действия, выполняемые этой подпрограммой, определяются пользователем, а непосредственными операциями ввода-вывода управляет процессор. Наконец, в режиме прямого доступа к памяти, который используется, когда пропускной способности процессора недостаточно, действия процессора приостанавливаются, он отключается от системной шины и не участвует в передачах данных между основной памятью и быстродействующими внешними устройствами.