- •Расчетно-графическая работа

- •1.Задание на ргр

- •1.1.Общие аспекты проектирования процессора

- •1.2.Исходные данные

- •2.Архитектура процессора

- •2.1.Форматы команд

- •2.2.Описание формата команд, определенных по индивидуальному заданию

- •2.3.Форматы данных

- •2.4.Расчет и выбор разрядности основных узлов процессора

- •2.5 Виды адресации

- •3. Структурная организация процессора

- •3. Структурная организация процессора

- •3.1 Общая структура процессора

- •3.2 Выбор и обоснование элементной базы

- •3.3 Блок(и) обработки данных (бод)

- •3.5 Регистровая память (рп)

- •4. Схемы алгоритмов работы процессора

- •4.1 Общий алгоритм цикла работы процессора

- •4.2 Выборка команд

- •4.3 Извлечение команды

- •4.4.Формирование исполнительных адресов и выборка операндов из памяти

- •4.5.Выполнение операций из индивидуального задания

- •5. Микропрограммное управление

- •5.1 Формат микрокоманды

2.5 Виды адресации

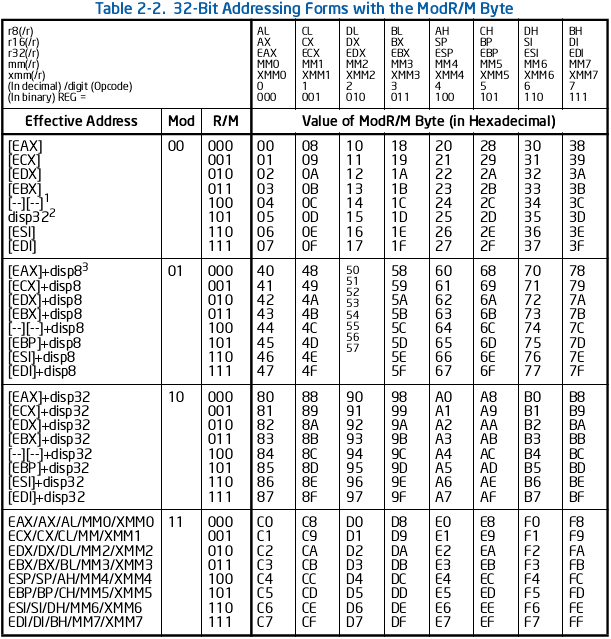

В архитектуре IA-32 определен большой и гибкий набор режимов адресации, используемых для доступа к отдельным элементам и областям памяти. Как минимум один операнд из двух, которые используются в команде, должен находиться в регистре. Значение поля Reg байта mod r/m определяет номер этого регистра. Второй операнд выбирается в зависимости от значения полей mod и r/m. Способы вычисления EA в зависимости байта mod r/m от можно посмотреть в таблицах 2.1. В данном проекте используется индексная(mod равен 01 или 10, r/m равен 100 или 101) и регистровая адресация(mod равен 11).

Таблица 2.2.Способы адресации при 32-разрядном режиме

3. Структурная организация процессора

3. Структурная организация процессора

3.1 Общая структура процессора

Процессор состоит из двух операционных блоков и управляющего автоматов и выполняет все действия, связанные с обработкой или преобразованием данных.

Рисунок

3.1 Общая структура процессора

Блок микропрограммного управления предназначен для реализации рабочего цикла процессора путем обработки микрокоманд, находящихся в отдельном ПЗУ. Данный блок является управляющим автоматом.

Операционные блоки для чисел с фиксированной и плавающей точкой, управляемые БМУ и производящие несложные арифметические действия.

Оперативная память - запоминающее устройство, способное хранить 32-битные слова.

ШОС - шина осведомительных сигналов, которые поступают в БМУ.

ШУ - шина управления – предназначена для передачи управляющих сигналов от Блока микропрограммного управления.

Блок интерфейсов - набор мультиплексируемых шин для обмена данными между блоками.

3.2 Выбор и обоснование элементной базы

Особенностью схемотехнического проектирования на интегральных схемах является большая сложность правильного выбора элементной базы. Это связано с неоднозначностью выбора вариантов построения отдельных узлов, блоков и устройств из-за широкой номенклатуры микросхем.

При выборе элементной базы основными критериями являются такие параметры элементов схем, как быстродействие и производительность, цена и надежность, универсальность используемых элементов, степень интеграции элементов, то есть простота реализации и применения, а также важным параметром является потребляемая мощность и нагрузочная способность.

Микросхемы серии К1804 разработаны на основе ТТЛШ и полностью согласуются по входным и выходным параметрам со стандартными ТТЛШ-схемами.

3.3 Блок(и) обработки данных (бод)

Блоки обработки данных будут реализованы на микросхемах МПС К1804 ВС2.

Особенности работы и функционирования МПС К1804 ВС2

Рисунок

3.2 Структурная

схема микросхемы КМ1804ВС2

МПС КМ1804ВС2 имеет в своем составе арифметико-логическое устройство, способное выполнять несложные арифметические и логические операции. Данные на АЛУ могут подаваться из разных источников (АЛУ отдельной МПС работает с двумя 4-х разрядными операндами):

а) шина данных DA

б) шина данных DB

в) данные из РЗУ

г) содержимое регистра Рг. Q

Коммутаторы Км. S, Км. R на входах АЛУ обеспечивают возможность выбора источников операндов АЛУ. В зависимости от состояния входа ЕА коммутатор Км. R выбирает либо шину DA внешних данных, либо данные А РЗУ в качестве одного из источников операнда АЛУ. Сигналы на входах ОЕВ и I0 управляют работой Км. S, который выбирает либо данные B РЗУ, либо входы DB, либо содержимое Рг. Q.

Сигналы на входах выбора источника |

Источник операндов АЛУ |

||||

ЕА |

I0 |

OEB |

Операнд R |

Операнд S |

|

0 0 0 1 1 1 |

0 0 1 0 0 1 |

0 1 X 0 1 X |

Данные А РЗУ Данные А РЗУ Данные А РЗУ Вход DA Вход DA Вход DA |

Данные В РЗУ Вход DB Данные Q Данные В РЗУ Вход DB Данные Q |

|

Таблица

3.1 Источники

операндов АЛУ

МПС КМ 1804 ВС2 имеет в своем составе 16 четырех разрядных регистров (РЗУ), данные из которых могут поступать на входы АЛУ. Выбор соответствующего регистра осуществляется шинами A и B (разрядность шин - 4 бита). Запись в РЗУ возможна только по адресу В с выходов Y.

МПС имеет собственное устройство управления, которое формирует внутренние управляющие сигналы (например, задание функции для выполнения в АЛУ).

АЛУ МПС К1804ВС2, способно выполнять большое число арифметических и логических операций, но в проектируемом процессоре предусмотрены только 2 команды, поэтому набор функций, требуемых для их реализации существенно сокращается.