- •Расчетно-графическая работа

- •1.Задание на ргр

- •1.1.Общие аспекты проектирования процессора

- •1.2.Исходные данные

- •2.Архитектура процессора

- •2.1.Форматы команд

- •2.2.Описание формата команд, определенных по индивидуальному заданию

- •2.3.Форматы данных

- •2.4.Расчет и выбор разрядности основных узлов процессора

- •2.5 Виды адресации

- •3. Структурная организация процессора

- •3. Структурная организация процессора

- •3.1 Общая структура процессора

- •3.2 Выбор и обоснование элементной базы

- •3.3 Блок(и) обработки данных (бод)

- •3.5 Регистровая память (рп)

- •4. Схемы алгоритмов работы процессора

- •4.1 Общий алгоритм цикла работы процессора

- •4.2 Выборка команд

- •4.3 Извлечение команды

- •4.4.Формирование исполнительных адресов и выборка операндов из памяти

- •4.5.Выполнение операций из индивидуального задания

- •5. Микропрограммное управление

- •5.1 Формат микрокоманды

2.4.Расчет и выбор разрядности основных узлов процессора

Регистр команд (РгК) хранит текущую исполняемую команду. На разрядность РгК влияет длина самой длинной команды, обрабатываемой процессором.

РгК = 32 бита.

Регистр адреса ОП (РгАОП): для хранения адреса слова в ОП разрядность РгАОП определяется по формуле: РгАОП = log2222/22 = 20 бит (логарифм от частного емкости ОП к длине слова ОП).

Счетчик адреса команд (СчАК)(указатель команд) определяет адрес следующей выполняемой команды в ОП. Разрядность СчАК определяется: разрядность РгАОП + 3, следовательно, равна 22 бита.

Согласно рассматриваемой архитектуре, счетчиком адреса команд служит определенный регистр – EIP. Данный регистр имеет разрядность 32 бита.

Регистры чтения и записи ОП (РгЧтОП, РгЗпОП) служат для хранения слова считанного из ОП или записываемого в ОП. На разрядность данных регистров влияет длина слова ОП, которая составляет 4 байт (32 бита).

Регистр флагов (EFLAGS) – 32 бита.

Слово состояния процессора (PSW) включает в себя системный регистр управления процессором CR0 (32 бита).

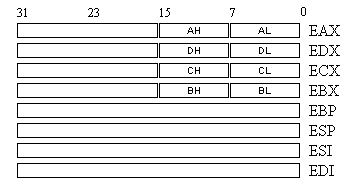

Регистры общего назначения (РОНы ) EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP имеют длину в 32 бит и содержат адреса или данные. Они поддерживают операнды-данные длиной 1, 8, 16, 32 и (при использовании двух регистров) 64 бит; битовые поля от 1 до 32 бит; операнды-адреса длиной 16 и 32 бит.

Доступ к младшим 16 бит этих регистров выполняется независимо при использовании соответствующих имен 16-битных регистров: AX, BX, CX, DX, SI, DI, BP и SP. Также могут использоваться индивидуально младший (биты 0-7) и старший (биты 8-15) байты регистров AX, BX, CX, DX. Им соответствуют обозначения AH, DH, CH, BH и AL, DL, CL, BL.

Формат регистров общего назначения:

Рисунок 2.2. Формат регистров общего назначения

Хотя регистр ESP тоже относится к регистрам общего назначения, он содержит указатель на вершину стека и его не стоит использовать для других целей.

Сегментные регистры CS, SS, DS, ES, FS,GS.

Процессоры Intel аппаратно поддерживают сегментную организацию программы. Это означает, что любая программа состоит из трех сегментов: кода, данных и стека. Логически машинные команды в архитектуры IA-32 построены так, что при выборке каждой команды для доступа к данным программы или стеку неявно используется информация из вполне определенных сегментных регистров. В зависимости от режима работы процессора по их содержимому определяются адреса памяти, с которых начинаются соответствующие сегменты.

Формат сегментных регистров:

Рисунок 2.3. Формат сегментных регистров

Указатель команд EIP

EIP является 32-разрядным регистром. Он содержит смещение следующей команды, подлежащей выполнению. Относительный адрес отсчитывается от начала сегмента исполняемой задачи. Указатель команд непосредственно недоступен программисту.

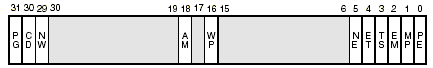

Регистр флагов EFLAGS

Регистр EFLAGS содержит группу флагов состояния, управления и системных флагов. Неопределенные биты зарезервированы, т.е. на данный момент они не имеют значения, однако могут быть использованы для специальных целей в последующих версиях микропроцессора. EFLAGS является 32 – разрядным регистром. Младшие 16 бит регистра представляют собой 16-разрядный регистр флагов и состояний, называемый FLAGS.

Содержимое регистра EFLAGS:

Рисунок 2.4. Содержимое регистра EFLAGS

Системный регистр CR0

Разрядность регистра CR0 составляет 32 бита. Регистр CR0 содержит флаги, которые управляют или показывают условия, относящиеся к системе в целом, а не к отдельной задаче.

Формат регистра CR0:

Рисунок 2.5. Формат регистра CR0