- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Rs-триггер

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •D-триггер

- •Dv-триггер

- •Синхронные триггеры с динамическим управлением записью

- •Dv-триггер и jk-триггер

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •D-триггер

- •Dv-триггер

- •19. Jk-ms и dv-ms триггеры. Схема, Временная диаграмма, определение параметров.

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

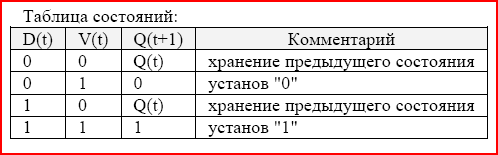

D-триггер

На практике наибольшее распространение получила схема синхронного D-триггера со статическим управлением записью.D-триггер имеет один логический входD(Delay- задержка), состояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. СхемуD-триггера можно получить изRS-триггера, если на входRподать инвертированный сигнал входаS.Однако целесообразно использовать для инвертирования уже имеющиеся элементы (рис. 3.6).

Рис. 3.6. Синхронный D-триггер со статическим управлением записью (пунктиром показан вход V для DV-триггера):

а) логическая схема; б) условное графическое обозначение D-триггера и его таблица переходов; в) условное графическое обозначение DV-триггера и его таблица переходов

Dv-триггер

Если к D-триггеру добавить еще один входV(Vorentscheidung- предварительное разрешение) для блокирования СИ (пунктирная линия на рис 3.6), то получим синхронныйDV-триггер со статическим управлением записью. Легко заметить, что входы С иVможно поменять местами без нарушения логики работы триггера.

Одноступенчатый асинхронный T – триггер.

Счетный Т-триггер. Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и -Q. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом . Как видно из диаграммы, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

Таким образом мы получаем различные пути синтеза одноступенчатых триггерных схем. В одноступенчатом триггере ограничение на длительность входного импульса будет с двух сторон(задается не только минимсальная но и максимальная длительность импульса при которой триггер будет вести себя как триггер, т.е. на выходе неQ будет инверсное состояние Q)

Одноступенчатый синхронный T – триггер.

Чтобы сгладить проблему ограничения по длине импульса в асинхронном одноступенчатом триггере можно усовершенствовать схему и сделать триггер синхронным. Т.е. взяли и добавили ещё вход С на элементы D1 и D2. Тогда действительно управляющий вход Т который разрешает работу этому Т-триггеру в счетном режиме. А вход синхронизации будет выполнять ту же самую роль что и вход Т в асинхронном режиме.

19. Jk-ms и dv-ms триггеры. Схема, Временная диаграмма, определение параметров.

DV-триггер

Временная диаграмма

Алгоритм построения временной диаграммы

Ключевые понятия для построения временной диаграммы:

Событие - это изменение любого сигнала любого сигнала.

Момент времени, для которого определяется состояние схемы, называется текущим.

Для построения временной диаграммы, сначала необходимо задать начальное состояние схемы для запоминающих элементов с учётом обратных связей. Например, Q(t0)=0.

Алгоритм построения временной диаграммы:

1. По входной диаграмме определить первое событие;

2. Поместить в список элементы, на которые поступает это событие;

3. Взять один из элементов списка и вычислить его выход (реализовать событие).

a. если новое значение не равно старому, то отметить это изменение через время задержки

и

и

относительно текущего момента времени;

относительно текущего момента времени;

b. если новое значение равно старому, то оно сохраняется.

4. Повторить шаг 3 для других элементов списка;

5. По выходной диаграмме и диаграммам выходов элементов найти ближайшее событие и перейти к шагу 2.