- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Кэш память. Организация, взаимодействие с процессором и озу.

Сумматоры. Принципы организации цепей переноса в сумматорах.

Сумматор - это некоторый элемент, который выполняет операцию арифметического (суммирование может быть ещё и логическое) суммирования двух чисел. Сумматор производит над словами некоторые операции. Значение суммы, которая образуется на выходе нашего сумматора S(Sn; S(n−1);...; S1); в общем случае рассматривается операция над двумя словами:x(xn; x(n−1);...; x1) и y(yn; y(n−1);...; y1) Сумма по каждому разряду каждого значения входного слова сумматора (разряд xi и yi) определяется по следующему алгоритму:Si = xi + yi + Pi-1;где Pi−1 - перенос из предыдущего разряда.

Эта операция производится лишь в том случае, когда сумма Si= xi + yi + Pi-1<q , где q - это основание той системы счисления, в которой работает наш сумматор. При этом условии перенос, который вырабатывается в i-м разряде Pi=0.

Сумматоры

реализуют две операции - сложение и

сдвиг.

Классификация сумматоров:

По количеству входов:

2 входа (полусумматор);

3 входа (полный сумматор).

По системе счисления:

двоичный;

двоично-десятичный;

шестнадцатеричный.

По способу организации переносов

естественный (последовательный) – обрабатывают числа разряд за разрядом, позволяя обойтись минимумом оборудования в ущерб быстродействию;

сквозной (параллельный) – выполняют операции над всеми разрядами многоразрядных чисел и используют специальное дополнительное оборудование для формирования цепей ускоренного переноса.

По способу реализации:

комбинационный;

последовательный.

Обработка многоразрядных чисел в многоразрядных сумматорах возможна двумя способами:

можно последовательно раскладывать - разряд за разрядом; в этом случае будет использоваться минимальное количество оборудования;

возможность параллельной обработки информации с одновременным сложением.

Простейшая организация обработки многоразрядных чисел - для сумматоров последовательного типа.

Эту схему можно немного модернизировать. В отличии от первой схемы, где перенос подаётся в прямом коде(???), в этом сумматоре должно быть два входа - перенос и инверсия переноса:

Достоинства: малое количество оборудования;

Недостаток: последовательная обработка информации - это достаточно длительный процесс. Если мы обрабатываем 32-х разрядные числа, то время обработки увеличивается в 32 раза.

Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

Триггером

называется устройство, имеющее два

устойчивых состояния равновесия и

способное под действием управляющих

сигналов быстро (скачкообразно) переходить

из одного состояния в другое. При

включении напряжения питания и отсутствии

внешних управляющих сигналов триггер

произвольно занимает одно из двух

состояний и может находиться в нем как

угодно долго. Триггер является элементом

памяти

и способен хранить 1 бит информации.

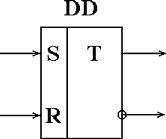

Структуру

триггера можно представить в виде

запоминающей

ячейки

(ЗЯ) и схемы

управления

(СУ) (рис. слева). Запоминающая

ячейка —

это схема, которая имеет два выхода: Q

и НЕ(Q),

разрешенные

сигналы на которых всегда противоположны,

и два входа: S

(Set

— установка)

и R (Reset

— сброс).

Асинхронный RS-триггер на элементе ИЛИ-НЕ.

Ниже показаны: принципиальная схема (рисунок 9.29, а), обозначение на электрических схемах (рисунок 9.29, б) и таблица истинности (состояний) (таблица 9.11) асинхронного RS - триггера на логических элементах ИЛИ-НЕ.

А Б

Рисунок 9.29

В таблице 9.11 приняты следующие обозначения: R и S - сигналы на входах триггера; Qt – выходной сигнал триггера до поступления входных управляющих сигналов; Qt+1 – выходной сигнал после воздействия управляющих сигналов.

Таблица переходов 9.11

|

№ |

S |

R |

Qt+1 |

|

0 |

0 |

0 |

Qt |

|

1 |

0 |

1 |

0 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

x |

Матрица переходов триггера на элементе ИЛИ-НЕ:

|

Тип перехода |

S |

R |

|

0 → 0 |

0 |

x |

|

0 → 1 |

1 |

0 |

|

1 → 0 |

0 |

1 |

|

1 → 1 |

x |

0 |

Триггер называется асинхронным, т.к. он переходит в новое состояние сразу после изменения входных сигналов. Входы S и R названы по первым буквам английских слов set – установка и reset – предустановка (сброс). Триггер устанавливается в единицу при комбинации входных сигналов S=1, R=0. Сброс в нуль происходит при S=0, R=1. Если S=R=0, то состояние схемы не меняется (Qt = Qt+1). Комбинация S=R=1, является запрещенной, т.к. положение триггера в этом случае не определено. В схеме выполняется условие возникновения скачков: баланс фаз (триггер содержит положительную обратную связь (ПОС)) и баланс амплитуд (суммарное усиление схемы больше суммарного затухания, вносимого пассивными элементами). Поэтому при изменении входных управляющих сигналов триггер быстро (лавинообразно) изменяет свое состояние. При включении питания и пассивном значении управляющих сигналов R=S=0 схема занимает произвольное положение (нулевое или единичное).

Асинхронный RS-триггер на элементе И-НЕ.

Ниже показаны: принципиальная схема (рисунок 9.30, а), обозначение на электрических схемах (рисунок 9.30, б) и таблица истинности (таблица 9.12) асинхронного RS - триггера на логических элементах И-НЕ.

А Б

Рисунок 9.30

Таблица переходов 9.12

|

№ |

S |

R |

Qt+1 |

|

0 |

0 |

0 |

x |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

Qt |

Матрица переходов:

|

Тип перехода |

S |

R |

|

0 → 0 |

1 |

x |

|

0 → 1 |

0 |

1 |

|

1 → 0 |

1 |

0 |

|

1 → 1 |

x |

1 |

Отличие этого триггера от предыдущего состоит в том, что активным значением управляющих сигналов является логический нуль, а пассивным – логическая единица.

Синхронный RS-триггер. В результате явления “состязаний” (“гонок”) на входах асинхронного RS-триггера временно могут появляться ложные комбинации, которые вызовут ошибочные срабатывания (переключения) схемы и будут ложно зафиксированы логическим устройством обработки выходных сигналов триггера. Для устранения этого недостатка используют синхронные RS-триггеры, содержащие дополнительный тактовый (синхро) вход. Синхронные RS - триггеры делятся на одноступенчатые и двухступенчатые.

Ниже показаны: обозначение на электрических схемах (рисунок 9.31,а) и принципиальные схемы (рисунок 9.31, б, в) одноступенчатого синхронного RS-триггера.

…..

…..

А Б В

Рисунок 9.31

Одноступенчатый синхронный RS-триггер (рисунок 9.31, б, в) включает асинхронный RS-триггер DD3 и два дополнительных логических элемента DD1, DD2: И (рисунок 9.31, б) или И-НЕ (рисунок 9.31, в). Более предпочтительной является вторая схема (рисунок 9.31, в), т.к. она содержит элементы одного базиса И-НЕ (см. рисунок 9.30). Одноступенчатый синхронный RS-триггер (рисунок 9.31) синхронизируется потенциалом или единичным импульсом на входе С.

Часто нужно осуществлять переключение триггера перепадом потенциала на его синхровходе С из 1 в 0 или из 0 в 1 (срезом или фронтом входного импульса). Синхронный RS-триггер, обладающий такой способностью, называется двухступенчатым. Ниже показаны: обозначение на электрических схемах (рисунок 9.32, а) и принципиальная схема (рисунок 9.32, б) двухступенчатого синхронного RS-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе.

А Б

Рисунок 9.32

Триггер выполнен на двух одноступенчатых синхронных RS-триггерах, рассмотренных выше, и инверторе DD3. Вход С (рисунок 9.32, а) называется динамическим, т.к. активным сигналом на нем является перепад из 1 в 0. Переключение триггера происходит за два такта: в первом такте входная информация записывается в первый триггер DD1, а состояние второго триггера DD2 не изменяется, т.к. на его синхровход с выхода инвертора подается нулевой импульс. Во втором такте в момент окончания единичного импульса на входе (при перепаде из 1 в 0) с выхода инвертора на синхровход триггера DD2 начинает поступать единичный потенциал и информация из первого триггера DD1 переписывается во второй DD2. Таким образом, состояние выхода меняется лишь в момент перепада из 1 в 0 входного синхросигнала.

Ниже показаны: обозначение на электрических схемах (рисунок 9.33, а) и принципиальная схема (рисунок 9.33, б) двухступенчатого синхронного RS-триггера, переключающегося перепадом из 0 в 1 на динамическом синхровходе.

А Б

Рисунок 9.33