- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Кэш память. Организация, взаимодействие с процессором и озу.

Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

Схемы, выходное состояние которых однозначно определяется только комбинацией входных сигналов, называют комбинационными. Закон функционирования КС определяется системой переключательных (логических) функций:

Синтез (построение) комбинационной схемы состоит в построении схемы на основе заданного закона ее функционирования в виде системы переключательных функций (ПФ) или таблиц истинности. При синтезе комбинационной схемы чаще всего необходимо построить схему с использованием минимального числа элементов в заданном элементном базисе, например, на элементах И-НЕ.

Комбинационные

схемы строятся из элементарных логических

элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и других.

Соединяют эти элементы так, как это

следует из логической формулы, т.е. вход

одного элемента, в котором часть

аргументов обработана как указано в

формуле, подключается ко входу другого,

где выполняется дальнейшая обработка

логической функции. В схеме не должно

быть обратных связей, т.е. соединения

выходов последующих схем со входами

предыдущих.

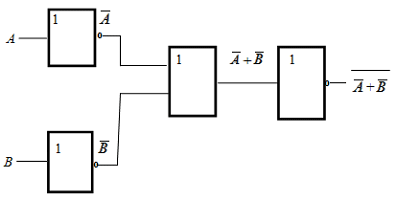

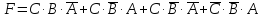

Пример:

Пусть дана логическая функция

Комбинационная схема представлена на рисунке.

Этапы синтеза:

Задание логической функции словесно, с помощью таблиц истинности или булевых выражений.

Минимизация логической функции с помощью алгебраического или графического метода (диаграммы Вейча, карты Карно).

Запись булевого выражения минимизированной переключательной функции.

Преобразование булевого выражения минимизированной ПФ для реализации её в заданном базисе И-НЕ или ИЛИ-НЕ.

Составление функциональной схемы, т.е. изображение нужных логических элементов и связей между ними.

Технологии минимизации. Минимизацией называют процедуру упрощения аналитического выражения, представляющего переключательную (логическую) функцию, направленную на то, чтобы булево выражение ПФ содержало минимальное количество членов с минимальным числом переменных. Способы минимизации: алгебраический; с помощью диаграмм Вейча (карт Карно).

Алгебраический способ минимизации ПФ - используя тождества и теоремы булевой алгебры.

Пример

1.

Исходное булево выражение:

Применяя

теорему склеивания

,

получим булево выражение

,

получим булево выражение ,

которое равносильно (эквивалентно)

исходному, но значительно проще его.

,

которое равносильно (эквивалентно)

исходному, но значительно проще его.

Диаграммы

Вейча

построены так, что их соседние клетки

содержат члены исходной ПФ, отличающиеся

значением одной переменной: один член

содержит эту переменную в прямой форме,

а другой – в инверсной. Благодаря этому

возникает наглядное представление о

различных вариантах склеивания смежных

членов.

Исходным продуктом для применения диаграмм Вейча является представление ПФ таблицей истинности, в которой возможные наборы переменных упорядочены по возрастанию или по убыванию их десятичных эквивалентов.

Вид диаграмм Вейча зависит от числа переменных минимизируемой ПФ - n и от того, как упорядочены наборы переменных в таблице. Если наборы упорядочены по возрастанию их десятичных эквивалентов, то диаграммы Вейча для n=2,3,4 имеют вид, приведенный на рисунке.

Число клеток диаграммы равно количеству наборов переменных: Nкл=Nнаб=2n.

Каждая клетка соответствует определенному набору переменных и имеет номер, одинаковый с номером набора.

Строки и столбцы диаграммы, помеченные чертой, определяют наборы, в которых переменные принимают единичные значения (входят в прямой форме). Строки и столбцы, не помеченные чертой, соответствуют наборам, в которых те же переменные принимают нулевые значения (входят в инверсной форме). В клетки записываются значения ПФ на соответствующем наборе (нулевое или единичное). Если на каком-то наборе функция не определена, то в клетке диаграммы ставится прочерк (или x).

ПФ считается неопределенной, если:

1) данный набор переменных в реальном логическом устройстве невозможен;

2) значение функции на данном наборе безразлично.

После заполнения диаграммы можно приступить непосредственно к минимизации, которую производят по единицам или нулям. В первом случае результатом минимизации будет булево выражение в ДНФ, а во втором – в КНФ.

Краткий алгоритм:

Функция, выраженная в СДНФ (СКНФ), записывается в диаграмму Вейча путём проставления единиц (нулей) в соответствующие координаты.

Производится объединение единиц (нулей), стоящих рядом, в так называемые m-кубы. Можно объединять единицы (нули), которые образуют правильный прямоугольник, содержащий 2, 4, 8, 16 единиц (нулей).

Замечание. Необходимо объединять максимально возможное количество смежных клеток, содержащих единицы (нули).

Замечание. Одна и та же единица (нуль) может охватываться несколько раз разными кубами.

Замечание. Верхняя и нижняя строки – смежные (можно объединить). Левый и правый столбцы – смежные. Угловые клетки – тоже смежные (диаграмму можно мысленно свернуть в тор).

Замечание. Перед выполнением минимизации в клетки, содержащие прочерки (где ПФ не определена), можно записать дополнительные единицы (нули), что способствует получению более простого конечного булевого выражения. При этом следует помнить, что хотя бы один раз необходимо объединить лишь основные единицы (нули). Дополнительные единицы (нули) могут увеличивать суммарное число единиц (нулей), входящих в куб, то есть уменьшать число переменных в результирующих конъюнкциях (дизъюнкциях).

Выписываются координаты получившихся m-кубов.

Объединённая дизъюнкция (конъюнкция) конъюнктивных (дизъюнктивных) координат всех m-кубов и есть минимальная форма.

Целью минимизации является получение минимальной ДНФ или КНФ, содержащей минимум членов с минимальным количеством входящих в них переменных.

Преобразование из базисов СДНФ и СКНФ в базис «Штрих Шеффера» и «Стрелка Пирса» (проверить, работает ли это как для Шеффера, так и для Пирса, сам алгоритм расписан вроде как только для Шеффера):

Проставляются скобки;

Все знаки конъюнкции и дизъюнкции заменяются на Штрих Шеффера.

Исключение: если вся функция состоит из одной импликанты, то она берётся с отрицанием.

Исключение: В состав функции входит импликанта из одной буквы – эта импликанта берётся с отрицанием.