- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

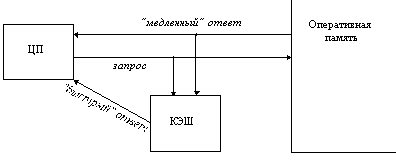

- •Кэш память. Организация, взаимодействие с процессором и озу.

Кэш память. Организация, взаимодействие с процессором и озу.

Кэш

микропроцессора —

кэш (сверхоперативная память), используемый

микропроцессором компьютера для

уменьшения среднего времени доступа к

компьютерной памяти. Кэш-память

- это способ организации совместного

функционирования двух типов запоминающих

устройств, отличающихся временем доступа

и стоимостью хранения данных, который

позволяет уменьшить среднее время

доступа к данным за счет динамического

копирования в "быстрое" ЗУ наиболее

часто используемой информации из

"медленного" ЗУ. Рассмотрим частный

случай использования кэш-памяти для

уменьшения среднего времени доступа к

данным, хранящимся в оперативной памяти.

Для этого между процессором и оперативной

памятью помещается быстрое ЗУ, называемое

просто кэш-памятью .Содержимое

кэш-памяти представляет собой совокупность

записей обо всех загруженных в нее

элементах данных.

Каждая запись об элементе данных включает

в себя адрес, который этот элемент данных

имеет в оперативной памяти, и управляющую

информацию: признак модификации и

признак обращения к данным за некоторый

последний период времени. Всистемах,

оснащенных кэш-памятью,

каждый запрос к оперативной памяти

выполняется в соответствии со следующим

алгоритмом:1)

Просматривается содержимое кэш-памяти

с целью определения, не находятся ли

нужные данные в кэш-памяти; кэш-память

не является адресуемой, поэтому поиск

нужных данных осуществляется по

содержимому - значению поля "адрес в

оперативной памяти", взятому из

запроса. 2)Если данные обнаруживаются

в кэш-памяти, то они считываются из нее,

и результат передается в процессор.

Если нужных данных нет, то они вместе

со своим адресом копируются из оперативной

памяти в кэш-память, и результат выполнения

запроса передается в процессор. При

копировании данных может оказаться,

что в кэш-памяти нет свободного места,

тогда ваместо в кэш-памяти объявляется

свободным.