- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Кэш память. Организация, взаимодействие с процессором и озу.

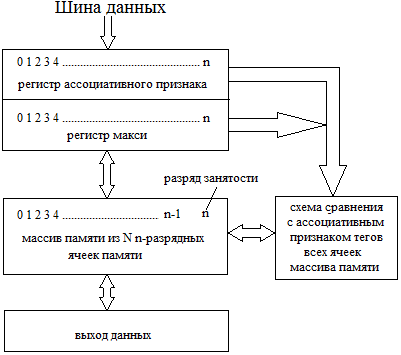

Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

Ассоциативный доступ реализует поиск информации по некоторому признаку, а не по ее расположению в памяти (адресу или месту в очереди). В наиболее полной версии все хранимые в памяти слова одновременно проверяются на соответствие признаку, например, на совпадение определенных полей слов (тегов — от английского слова tag) с признаком, задаваемым входным словом (теговым адресом). На выход выдаются слова, удовлетворяющие признаку. Дисциплина выдачи слов, если тегу удовлетворяют несколько слов, а также дисциплина записи новых данных могут быть разными. Основная область применения ассоциативной памяти в современных ЭВМ — кэширование данных.

В

ассоциативных запоминающих устройствах

поиск информации производится по

ассоциативному признаку, записанному

в каждую ячейку памяти.

В регистр маски записывается слово, разрешающее запрос по всем или только некоторым разрядам ассоциативного признака, применение маски позволяет сократить или расширить область поиска.

Поиск информации производится параллельно по всем ячейкам путем сравнения запроса с ассоциативным признаком каждой ячейки.

Результат поиска формирует специальная комбинационная схема, вырабатывающая сигналы, оповещающие об отсутствии слов, удовлетворяющих условиям поиска, о наличии только одного слова, о наличии нескольких слов, имеющих такой ассоциативный признак.

После формирования и обработки оповещающих сигналов схемой управления производится считывание необходимой информации. При записи отыскивается свободная ячейка по значению разряда занятости, в первую найденную свободную ячейку записывается информация.

Проверка разряда занятости производится по установке n-го разряда (разряда занятости) маски. При использовании дополнительных комбинационных схем в ассоциативной памяти можно выполнять различные логические операции, определяя максимальное или минимальное число, количество слов, имеющих одинаковый ассоциативный признак и т.д. Ячейки памяти ассоциативного запоминающего устройства должны быть элементами статической памяти, в ассоциативной памяти обращение производится ко всем ячейкам одновременно и не должно прерываться циклами регенерации. Ассоциативная память наиболее быстродействующая, но очень дорогая, так как требует введения дополнительно схемы сравнения, позволяющей осуществить поиск, для каждой ячейки памяти. Поэтому такая память обычно не используется в чистом виде, а быстродействующие устройства памяти типа Кэш обычно выполняются как частично ассоциативные.

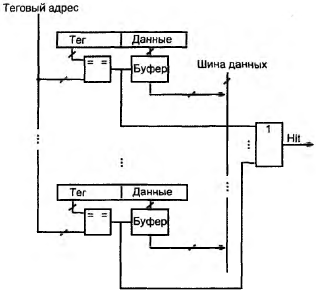

В

полностью

ассоциативной кэш-памяти

(FACM, Fully

Associated

Cache

Memory),

каждая ячейка хранит данные, а в поле

"тег" — полный физический адрес

информации, копия которой записана. При

любых обменах физический адрес

запрашиваемой информации сравнивается

с полями "тег" всех ячеек и при

совпадении их в любой ячейке устанавливается

сигнал Hit.

При чтении и значении сигнала Hit = 1 данные выдаются на шину данных, если же совпадений нет (Hit = 0), то при чтении из основной памяти данные вместе с адресом помещаются в свободную или наиболее давно не используемую ячейку кэш-памяти.

При записи данные вместе с адресом сначала, как правило, размещаются в кэш-памяти (в обнаруженную ячейку при Hit = 1 и свободную при Hit = 0).Копирование данных в основную память выполняется под управлением специального контроллера, когда нет обращений к памяти.

Память типа FACM является весьма сложным устройством и используется только при малых емкостях, главным образом в специальных приложениях. В то же время этот вид кэш-памяти обеспечивает наибольшую функциональную гибкость и бесконфликтность адресов, т. к. любую единицу информации можно загрузить в любую ячейку кэш-памяти.