- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Кэш память. Организация, взаимодействие с процессором и озу.

Запоминающая ячейка статического типа, устройство и принцип работы.

Элементарной

ячейкой статического ОЗУ с произвольной

выборкой является триггер на транзисторах

Т1-Т4 (рис. 3.7) с ключами Т5-Т8 для доступа

к шине данных. Причем Т1-Т2 - это нагрузки,

а Т3-Т4 - нормально закрытые элементы.

Сопротивление элементов Т1-Т2 легко регулируется в процессе изготовления транзистора путем подгонки порогового напряжения при легировании поликремниевого затвора методом ионной имплантации. Количество транзисторов (6 или 8) на ячейку зависит от логической организации памяти микропроцессорной системы.

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Кроме того статические ОЗУ применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.

Запоминающая ячейка динамического типа, устройство и принцип работы.

Запоминающая ячейка Динамического типа.

Cn – бумажного типа и находится в транзисторе.

Конденсатора на самом деле нет.

Это паразитная емкость, возникшая из параллельной емкости транзистора.

Полевой транзистор может хранить заряд емкости.

Значение хранится некоторое время и требует периодического восстановления информации - регенерация.

Обычно ячейки памяти динамического типа объединяют динамическую матрицу,

Что при любом обращении ячейки, находящейся в строке, выполняется цикл регенерации для всех ячеек в этой строке.

Программируемые логические интегральные схемы. Основные принципы построения плм.

Микросхемы программируемой логики или ПЛИС (программируемые логические интегральные схемы) — одно из наиболее динамично развивающихся направлений современной цифровой электроники. Привлекательность данной технологии заключается в предоставляемой конечному пользователю возможности быстрого создания цифровых устройств с произвольной внутренней структурой. По сравнению со специализированными цифровыми микросхемами (Application Specific Integral Circuit, ASIC), цикл разработки устройств на ПЛИС занимает значительно меньшее время и неизмеримо дешевле (благодаря тому, что изменение принципиальной электрической схемы выполняется путем перепрограммирования одного и того же экземпляра микросхемы). Таким образом, вместо металлических соединений, реализуемых в процессе производства ASIC, в ПЛИС используются соединения, коммутируемые программируемыми ключами. Для задания этих соединений в ПЛИС существует теневая (конфигурационная) память, хранящая таблицу соединений.

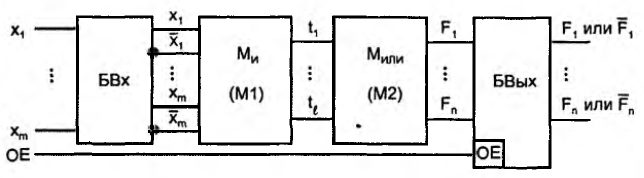

Программируемые логические матрицы появились в середине 70-х годов. Основой их служит последовательность программируемых матриц элементов И и ИЛИ. В структуру входят также блоки входных и выходных буферных каскадов (БВх и БВых).

Входные

буферы, если не выполняют более сложных

действий, преобразуют однофазные входные

сигналы в парафазные и формируют сигналы

необходимой мощности для питания матрицы

элементов И. Выходные буферы обеспечивают

необходимую нагрузочную способность

выходов, разрешают или запрещают выход

ПЛМ на внешние шины с помощью сигнала

ОЕ, а иногда выполняют и более сложные

действия. Основными

параметрами ПЛМ (рис. 7.1) являются число

входов т, число термов l

и число выходов п.

Переменные xi...xm подаются через БВх на входы элементов И (конъюнкторов), и в матрице И образуются l термов. Под термом здесь понимается конъюнкция, связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу конъюнкторов или, что то же самое, числу выходов матрицы И. Термы подаются далее на входы матрицы ИЛИ, т. е. на входы дизъюнкторов, формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций n. Таким образом, ПЛМ реализует дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций (двухуровневую логику). ПЛМ способна реализовать систему п логических функций от т аргументов, содержащую не более l термов. Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей И. Какие именно термы будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

ПЛМ позволяют реализовать массив возможно совместных логических функций за счёт пережигания на кристалле ПЭВМ. Недостатки: одноразовое программирование; минимальная реализация КС.