- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Кэш память. Организация, взаимодействие с процессором и озу.

Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

Счётчиком

называют последовательную схему,

предназначенную для увеличения/уменьшения

хранимого кода на единицу или заданную

константу. Счетчиками

называют устройства для подсчета числа

входных импульсов и фиксации этого

числа в каком-либо коде. В процессе

работы счетчик последовательно изменяет

свое состояние.

Счетчик также характеризуется: 1)Модулем счета М — определяет число возможных состояний счета. После поступления на счетчик М счетных сигналов начинается новый цикл, повторяющий предыдущий. 2) Разрядностью. 3) Величиной инкремента/декремента. Счётчики могут быть: а) Синхронными; б) асинхронными.

В синхронных схемах все изменения согласуются по времени с подачей считаемого сигнала на общую шину, объединяющую синхронизирующие входы С триггеров счетчика (рис. а).

В асинхронном счетчике отсутствует общая шина, на которую поступает считаемый сигнал. На вход С триггеров асинхронного счетчика сигналы могут поступать как с выхода другого триггера, так и от схем, непосредственно не связанных с синхронизирующими импульсами (рис. б).

Для асинхронных счётчиков удобных систематизированных методов нет, из-за различий во внутреннем строении триггеров проявляющихся при асинхронной работе. Поэтому при разработке надо иметь чёткое представление о внутреннем строении триггера и не ограничиваться таблицей переходов, которая описывает только синхронную работу триггера.

Счетчики

делятся по способу переноса: Последовательный

перенос -

счетные импульсы поступают только на

вход первого разряда, а с его выхода –

на вход второго и т.д. (счетчики с

последовательным переносом отличаются

простотой, но при этом имеют низкое

быстродействие); Параллельный перенос–

счетные импульсы поступают одновременно

на все разряды (такие счетчики имеют

более сложную организацию, но обеспечивают

высокое быстродействие); Сквозной

перенос; Комбинированный

(параллельно-последовательные счетчики),

представляющие собой комбинацию первых

двух способов подачи счетных импульсов

(такие счетчики используются для

получения больших значений модуля

счета).

При каскадировании счетчиков с целью получения большего значения модуля счета необходимо организовать перенос между двоично-десятичными разрядами. Необходимо сформировать двоичный сигнал декодирования последнего состояния счетчика — ТС (terminal count) - производиться с помощью элемента ИЛИ.

Увеличение разрядности двоично-десятичных счетчиков требует организации выходного сигнала переноса CEO (clock enable out) в соответствии с выражением: CEO = ТС & CE.Многоразрядные счетчики получают путем соединения выхода CEO одного разряда с входом CE следующего разряда и объединением входов C и CLR всех счетчиков соответственно.

Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

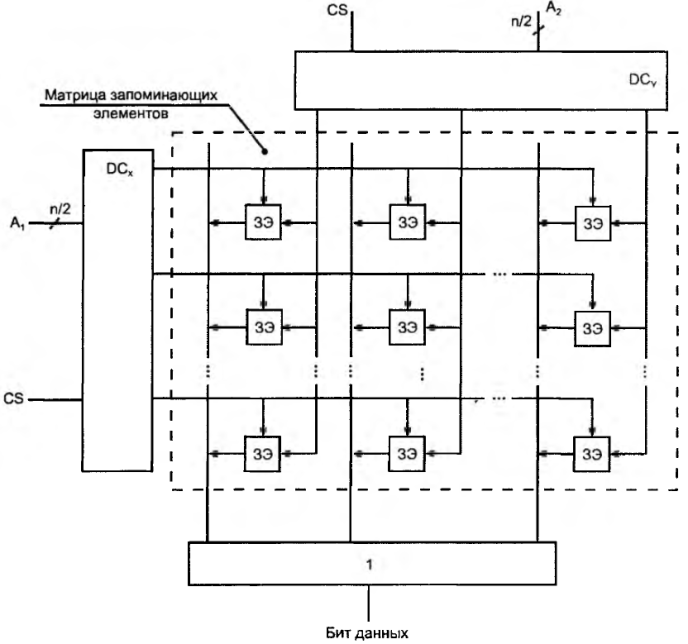

Ячейки

памяти составляют двумерный массив,

т.е. матрицу и те из них, что находятся

на одной строке условно называются

строкой, а те, что друг под другом -

условно столбцом и образуют зону

хранения.

Функция выборки обеспечивается дешифраторами.

Бит данных поступает на усилитель записи\чтения.

Усилители записи/чтения необходимы для преобразования уровня сигнала в понятный для других устройств вид.

Регистр адреса содержит адрес ячейки к которой нужно получить доступ, при этом часть регистра – это адрес строки, а вторая часть – адрес столбца. Данные с регистра адреса подаются на дешифраторы.