- •Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •7.Потребляемая мощность.

- •Перeключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических элементов. Уго элементов.

- •Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим. Минимизация Методом Квайна Мак-Класски.

- •Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах. (досмотреть)

- •Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •Сумматоры. Принципы организации цепей переноса в сумматорах.

- •Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs- триггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе dVтриггера.

- •Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение триггера на базе jKтриггера.

- •Таблицы и матрицы переходов:

- •Построение произвольного триггера на базе jk – триггера

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •Схемы триггеров со статическим и динамическим управлением записью.

- •Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

- •Jk-mSиDv-mSтриггеры. Схема, временная диаграмма, определение параметров.

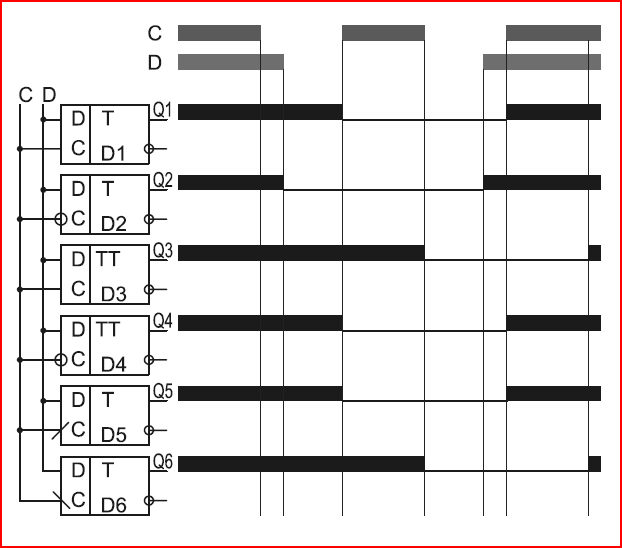

- •Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

- •Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Регистры хранения и регистры сдвига. Обобщенная схема регистра сдвига.

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

- •Счетчик по модулю м. Проектирование счетчиков. Изменение модуля пересчета.

- •Проектирование счетчика с заданным набором состояний на rSтриггерах.

- •Проектирование счетчика с заданным набором состояний на dVтриггерах.

- •Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Таблицы и матрицы переходов:

- •Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •Уго микросхемы памяти.

- •Микросхемы памяти. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Реализация фал на микросхеме памяти.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение принцип работы.

- •Обобщенная структура плис fpga. Назначение и устройствоClb.

- •Реализация логических функций в плис, lut- назначение и устройство.

- •Блоки ввода вывода Плис, Теневая память. Программируемые соединения.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Кэш память. Организация, взаимодействие с процессором и озу.

Триггер с динамическим управлением записью. Особенности работы. Временная диаграмма.

Отличительной чертой триггеров с динамическим управлением записью является то, что информация в триггер поступает только в момент изменения сигнала на входе С или из 0 в 1, или из 1 в 0. В первом случае триггер имеет прямой динамический вход С, а во втором — инверсный динамический вход С.

Синхронные триггеры с динамическим управлением записью обладают более высоким по сравнению с двухступенчатыми триггерами быстродействием. Данные триггеры также нечувствительны к ложным сигналам на логических входах при обоих уровнях сигнала на входе С.

Для правильной работы этого типа триггеров сигналы на логические входы должны подаваться заранее до прихода активного фронта синхроимпульса (время предварительной установки). При этом необходимо выдерживать их неизменными еще некоторое время (время удержания) после окончания этого фронта синхроимпульса. Нарушение данных требований приводит к непредсказуемому переключению триггера.

Характеристики:

Задержки переключения

Время предварительной установки

Время удержания

Реакция триггеров с различной структурой на входное воздействие (временная диаграмма)

Регистры. Классификация. Уго регистров. Регистры хранения и регистры сдвига. Реверсивный регистр.

Регистр

— устройство для хранения данных.

Представляет собой набор триггеров,

к-ый позволяет хранить и видоизменять

многоразрядный бинарный код (слово).

Разрядность

регистра

— количество хранимых значений, набор

образующих этот регистр триггеров.

Регистры

выполняют 2 функции:

1)Хранение данных 2)Сдвиг (видоизменение

хранимого многоразрядного бинарного

кода).

Сдвиги: 1) В сторону старших разрядов («сдвиг влево»); 2) В сторону младших («сдвиг вправо»). а) Циклические — биты, выходящие за пределы разрядной сетки, записываются в последний разряд регистра, противоположный направлению сдвига (Выход старшего/ младшего разряда — на вход младшего/старшего). б) Нециклические — биты, выходящие за пределы.

Регистры

1) Хранения

— только хранит слов.2) Сдвиговые

— то же + сдвиг вправо/влево. Сдвиг

происходит во время синхросигнала 3)

Реверсивные

— то же + возможность указать направление

сдвига.

Регистры

по способу приема и выдачи данных:1)

параллельные

— прием и выдача слов производится по

всем разрядам одновременно

2)

последовательные

— слова принимаются и выдаются разряд

за разрядом.3) послед.-параллельные

— такие регистры имеют входы/выходы

одновременно последовательного и

параллельного типа.

При

реализации различных операций в

арифметическом и других устройствах

компьютеров широкое применение находят

различные виды сдвигов информации.

Операция сдвига, как правило, выполняется

на регистрах сдвига. Регистр

сдвига представляет собой схему на

триггерах, соединения между которыми,

называемые цепями сдвига, обеспечивают

передачу двоичной информации от одних

триггеров регистра к другим. Схема

четырехразрядного регистра сдвига на

один разряд вправо на D-триггерах.

Последовательный входной сигнал DП0 — это новый бит, который «вдвигается» с одного конца на данном такте. Этот бит появляется на последовательном выходе Q3 спустя 4 такта и теряется на следующем такте. Таким образом, n-разрядный регистр сдвига с последовательным вводом и последовательным выводом можно использовать для задержки сигнала на n тактов. Регистры, выполняющие как левый, так и правый сдвиги, называют реверсивными регистрами сдвига. Данный регистр помимо шины сдвига С имеет управляющий вход У. Его назначение состоит в том, чтобы из двух микроопераций сдвига, выполняемых регистром, выбрать одну, требуемую в данный момент времени. Таким образом, сигнал, поступающий на вход У, настраивает определенную цепь сдвига от одних триггеров к другим и запрещает работу остальных цепей.