- •Курсова робота

- •Анотація

- •Аннотация

- •1Будова мікроконтролера at90s2313:, огляд алгоритмів,схемних та програмних рішень поставленої задачі

- •Огляд архітектури at90s2313

- •Будовамікроконтролера at90s2313

- •1.2.1 Файл регістрів загального призначення

- •1.2.2 Арифметико-логічний пристрій – алп

- •1.2.3 Статичне озу даних

- •1.2.4 Покажчик стека sp

- •1.2.5 Сторожовий таймер

- •1.2.6 Аналоговий компаратор

- •1.2.7 Регістр управління і стану аналогового компаратора (acsr).

- •Порти введення / виводу–порт

- •1.2.9 Порти введення / виводу - порт d

- •1.2.10 Програмування флеш пам'яті і eeprom

- •1.2.11 ПрограмуванняFlаshпам'яті

- •1.2.12 Програмуванняпам'яті даних

- •1.2.13 Читання пам’яті програм

- •1.2.14 Читання памяті даних

- •Особливості мікроконтролера at90s2313:

- •2 Розробка схем структурної,принципової та алгоритму програми

- •2.1 Структурна схема

- •2.2 Схема електрична принципова

- •2.3 Алгоритм роботи програми

- •3 Розробка програми на мові програмування assembler

- •4 Розробка програми на мові програмування с

- •Моделювання в proteusvsm

- •Висновки

- •Перелік посилань

- •Додаток а Розробка програми на мові програмування Assembler

- •Додаток б Розробка програми на мові програмування с

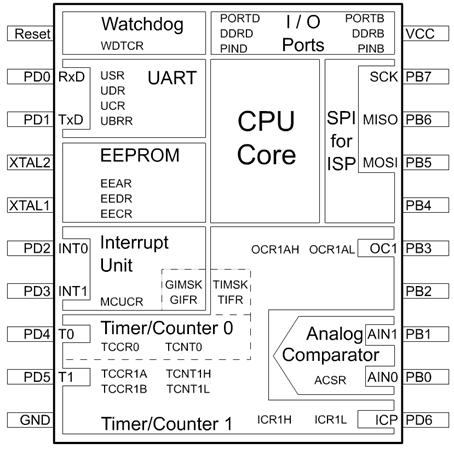

Будовамікроконтролера at90s2313

До складу мікроконтролера входять:

1) генератор тактового сигналу (GCK);

2)процесор (CPU);

3) постійний запам'ятовуючий пристрій для збереження програми виконаний за технологією Flash (FlashROM);

4) оперативний запам'ятовуючий пристрій статичного типу для збереження даних (SRAM);

5) постійний запам'ятовуючий пристрій для збереження даних, виконаний за технологією EEPROM (EEPROM);

6) набір периферійних пристроїв для вводу/виводу даних і керуючих сигналів, і виконання інших функцій.

До складу процесора (CPU) входять:

лічильник команд (PC);

арифметико-логічний пристрій (ALU);

блок регістрів загального призначення (GPR, General Purpose Regіsters) і інші елементи.

Крім регістрів загального призначення в мікроконтролері є регістри спеціальних функцій, що у сімействі AVR називаються регістрами введення/виведення (І/O Regіsters,IOR). За участю цих регістрів здійснюється:

1)керування роботою мікроконтролера і окремих його пристроїв;

2)визначення стану мікроконтролера і окремих його пристроїв;

3)ввід даних у мікроконтролер й окремі його пристрої, виведення даних і виконуються інші функції.

Для нумерації регістрів введення/виведення використовуються номери від 0 до 63 (від $00 до $3F, де $ - показник шістнадцятирічного коду). Кожному регістру присвоєне ім'я, пов'язане з функцією, яку виконує цей регістр.

Мікроконтролери різних типів мають різний склад регістрів введення/виведення, при цьому регістри з однаковими номерами можуть мати різні імена.

Мікроконтролери сімейства AVR є пристроями синхронного типу. Дії, що виконуються у мікроконтролері, прив'язані до імпульсів тактового сигналу.

Генератор тактового сигналу (GCK) використовується, як:

1) внутрішній генератор із зовнішнім кварцовим чи керамічним резонатором (XTAL);

2) внутрішній RC-генератор (ІRC);

3) внутрішній генератор із зовнішнім RC-колом (ERC);

4) зовнішній генератор (ЕХТ).

У мікроконтролерів, які мають внутрішній генератор із зовнішнім резонатором (XTAL), резонатор підключається до виводів XTAL1 н XTAL2, що через конденсатори малої ємності (20-30 пФ) з'єднуються із шиною GND. Тактова частота визначається робочою частотою резонатора. XTAL1 і XTAL2 є входом і виходом, відповідно, який інвертує підсилювач, що з використанням кварцового чи керамічного резонатора працює як вбудований генератор, як показано на рис.2. При використанні зовнішнього джерела тактової частоти вивід XTAL2 повинний залишитися вільним, сигнал подається на вивід XTAL1.

Рисунок 1.2 – Внутрішній вигляд мікроконтролера AT90S2313

Процесор (CPU) формує адресу наступної команди, вибирає команду з пам'яті й організовує її виконання. Код команди має формат "слово" (16 біт) або "два слова".

До складу процесора крім лічильника команд (PC), арифметико-логічного пристрою (ALU) і блоку регістрів загального призначення (GPR) входять:

1) регістр стану мікроконтролера SREG;

2) регістр-показник стека SP або SPL і SPH.

ALU з'єднано безпосередньо з усіма 32 швидкодіючими регістрами загального призначення.

Операції ALU підрозділяються на три основні категорії:

арифметичні

логічні

операції над бітами