- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •НАЧАЛЬНЫЕ СВЕДЕНИЯ О ПЛИС

- •Интегральные схемы типа FPGA

- •Перестраиваемый логический блок

- •Генераторы логических функций

- •Триггер

- •Блоки ввода/вывода сигналов

- •Программируемые соединения

- •Динамические параметры конфигурируемого логического блока

- •ОРГАНЫ УПРАВЛЕНИЯ УНИВЕРСАЛЬНОГО ЛАБОРАТОРНОГО СТЕНДА

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ

- •СИНТЕЗ КОМБИНАЦИОННЫХ МНОГОВЫХОДНЫХ СХЕМ

- •Реализация булевых функций с помощью постоянного запоминающего устройства

- •ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

- •СИНХРОННЫЕ ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ДВУХСТУПЕНЧАТЫХ ТРИГГЕРОВ

- •ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНТЕЗ СИНХРОННЫХ СЧЕТЧИКОВ

- •Матрица переходов триггера

- •ПРИМЕР

- •ПРОЕКТИРОВАНИЕ СЧЕТЧИКОВ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

- •ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

- •ПРОЕКТИРОВАНИЕ РЕГИСТРА НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •Статические и динамические состязания сигналов

- •Функциональные и логические состязания сигналов

- •Синтез схем, свободных от логических состязаний

- •Анализ комбинационных схем с целью выявления состязаний

- •СОСТЯЗАНИЯ СИГНАЛОВ В ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМАХ

- •Последовательностные схемы

- •Условия надежного функционирования асинхронной схемы

- •Критические состязания

- •Существенные состязания

- •Анализ асинхронных последовательностных схем

- •Устранение критических состязаний

- •ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ СОСТЯЗАНИЙ СИГНАЛОВ

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •Логические элементы

- •Мультиплексоры

- •Описание цифрового осциллографа

- •Запуск и настройка осциллографа

- •Настройка изображения сигнала на экране осциллографа

- •Получение устойчивого изображения сигнала

- •Выбор цены деления по оси Х и Y

- •Выбор фронта сигнала по входу Х осциллографа

- •Измерение временных интервалов (измерение задержек)

ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

Универсальные регистры с входами различного функционального назначения имеют и разнообразные динамические параметры.

Впаспорте регистра обычно указывают следующие параметры:

минимальные длительности синхронизирующих и установочных импульсов;

задержки переключения регистра по синхронизирующему и установочному входам;

время предварительной установки сигналов на управляющих входах и входах данных;

время удержания сигналов на входах данных.

Минимальные длительности импульсов по входам CLR (tиCLR) и С (tиС) определяются соответствующими параметрами триггеров, на которых построен регистр.

Задержки переключения регистра по входам CLR и С также определяются задержками переключения триггеров, составляющих регистр.

Время предварительной установки сигналов

Время предварительной установки для управляющих сигналов

У (tуст.УС) и сигналов данных D (tуст.DC) определяет тот минимальный интервал времени, на который поступление управляющей ин-

формации и данных должно опережать активный фронт синхроимпульса.

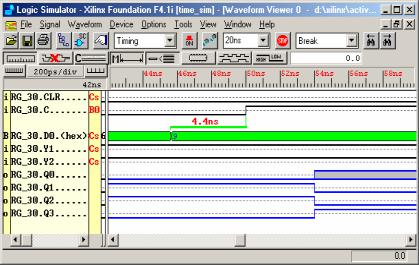

Измерение времени предварительной установки сигналов данных D для спроектированной схемы регистра выполняется по временной диаграмме, получаемой при временном моделировании схемы регистра.

Процедура измерения следующая:

в регистр загружают некоторый код, например, 0110;

перед поступлением очередного синхроимпульса этот код на внешних входах данных меняют на инверсный, т.е. на 1001. Это

133

требование связано с необходимостью изменения сигналов на каждом входе данных;

затем сдвигают момент изменения входов, постепенно приближая его к фронту 0/1 синхроимпульса до тех пор, пока не произойдет ошибка при загрузке кода. Ошибочная загрузка кода проявляется на выходах регистра в виде неопределенного сигнала на одном или нескольких выходах (рис. 5.11);

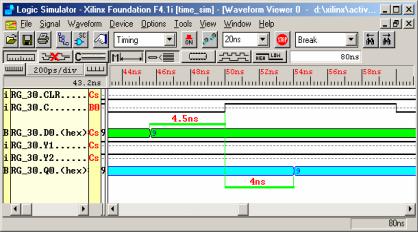

если найдено минимальное время нарушения времени предварительной установки сигналов данных, то при увеличении этого времени на 0.1 нс ошибка в загрузке исчезнет (рис. 5.12). Это время и будет временем предварительной установки сигналов дан-

ных: tуст.DC.= 4.5 нс.

Рис. 5.11. Нарушение времени предварительной установки сигналов данных

134

Рис. 5.12. Время предварительной установки сигналов данных

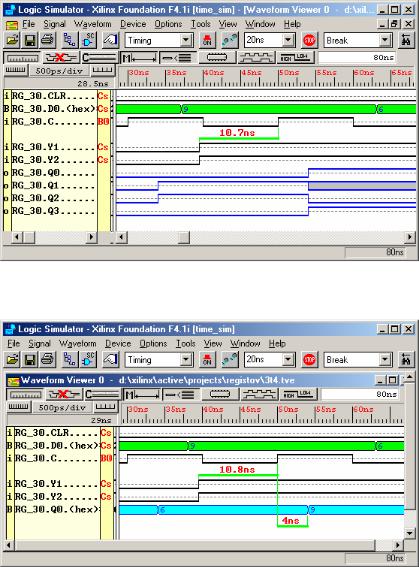

Измерение времени предварительной установки для управляющих сигналов У также выполним по временной диаграмме, получаемой с помощью временного моделирования. Для этого при фиксированных данных изменяют сигналы на управляющих входах в непосредственной близости к фронту 0/1 синхроимпульса. В остальном методика оценки времени предварительной установки управляющих сигналов У ничем не отличается от вышеприведенной оценки данного времени для сигналов данных D.

На рис. 5.13 и 5.14 приведены временные диаграммы, иллюстрирующие измерения данного параметра.

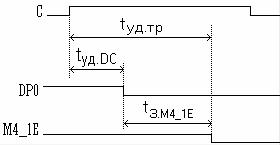

Как следует из приведенных диаграмм время предварительной установки управляющих сигналов для рассматриваемой схемы регистра будет равно tуст.УС = 10.8 нс.

135

Рис. 5.13. Нарушение времени предварительной установки для управляющих сигналов

Рис. 5.14. Время предварительной установки для управляющих сигналов

136

Время удержания сигналов

Время удержания — это интервал времени, в течение которого сигнал на входах данных последовательного или параллельного приема информации должен оставаться неизменным после активного фронта синхроимпульса. Соблюдение этого условия гарантирует надежное распознавание регистром поступившей информации.

Оценку времени удержания сигнала на входах данных (tуд.DС) выполним по временной диаграмме, приведенной на рис. 5.15. Изменение сигнала данных вызывает переключение мультиплексора М4_1Е (см. рис. 5.6 и 5.15). Переходный процесс завершится на логическом входе триггера регистра. Для надежной работы регистра необходимо, чтобы этот процесс завершился спустя время tуд.тр после активного фронта синхроимпульса на шине С (см. рис. 5.15). Время tуд.тр — это время удержания сигнала для триггера.

Рис. 5.15. Оценка времени удержания данных

Из рассмотрения рис. 5.15 можно записать выражение для оценки времени удержания:

tуд.DC = tуд.тр − tз.М 4_1Е .

Из этого выражения следует, что время удержания может быть положительным, равным нулю или отрицательным. В последнем случае смену входной информации можно выполнять еще до ак-

137

тивного фронта синхроимпульса без нарушения логики работы регистра.

Временные диаграммы, приведенные на рис. 5.16 и 5.17, наглядно иллюстрируют этот вывод. Для определения времени удержания данных за исходную была взята временная диаграмма (рис. 5.12). Далее данные изменялись, как показано на рис. 5.16 и 5.17. Из рассмотрения временных диаграмм следует, что время удержания данных равно tуд.DС = -1.7 нс.

Рис. 5.16. Нарушение времени удержания данных

138