К9-12В. Вопросы и ответы к ГОСам 2013 / Схемотехника ЭВМ / 02. Этапы проектирования КС на примере мультиплексора 4-1

.docx02. Этапы проектирования комбинационных схем на примере мультиплексора 4-1: определение, таблица истинности, функция, логическая схема. Увеличение размерности до 16-1.

Задача: Реализовать функцию F1(X3,X2,X1,X0)=Ʃ(0,2,6,7,8,9,13,14) на мультиплексоре.

Мультиплексором (от английского multiplexer–многократный, обозначают MUX или MS multiplexer selector) называют коммутатор, который передаёт сигнал с одного из информационных входов на выход. Мультиплексоры применяются в устройствах передачи данных и позволяют направлять данные от отдельных источников в общую линию для передачи по назначению, например, в микропроцессорах для передачи на одни и те же выводы микропроцессора значения адреса или данных, что позволяет существенно сократить количество выводов микросхемы; в системах управления мультиплексоры устанавливаются на удалённых объектах для возможности передачи информации от нескольких установленных на них датчиков по одной линии; кроме селекции потоков данных, мультиплексоры широко используются для преобразования данных из параллельного двоичного кода в последовательный.

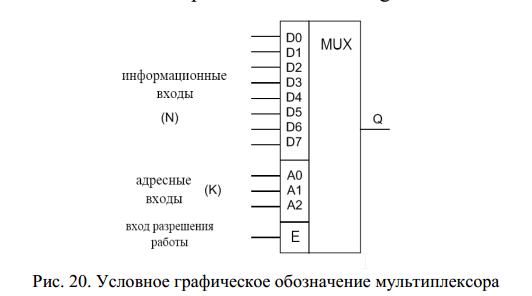

Мультиплексор – это комбинационная схема, имеющая N информационных входов, K адресных (селективных) входов и один выход. Двоичный код на адресных входах определяет номер информационного входа, значение которого передаётся на выход. Если между числом информационных входов N и числом адресных входов K действует соотношение N=2^K , то такой мультиплексор называют полным. Если N<2^K, то мультиплексор называют неполным.

Кроме того, для расширения функциональных возможностей мультиплексоры могут иметь входы разрешения Е. Данные входы используются для наращивания разрядности мультиплексоров, синхронизации их работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, т.е. могут блокировать действие всего устройства.

На рис. 21. приведены УГО, таблица истинности и логическая схема мультиплексора М2_1Е (при N=2 и K=1). Когда разрешающий вход Е=1, то мультиплексор М2_1Е выбирает один бит данных из двух информационных входов D1 или D0 в зависимости от состояния управляющего (адресного) входа A0 (S0). При Е=0 состояние выхода равно «0». В соответствии с таблицей истинности мультиплексор М2_1Е с входом разрешения Е реализует следующую функцию:

F M2_1 = E∙¬A0∙D0+E∙A0∙D1.

Таблица истинности для четырёхвходового мультиплексора М4_1Е приведена в таблице 1 (при N=4 и K=2). Когда разрешающий вход Е=1, то мультиплексор М4_1Е выбирает один бит данных из четырёх информационных входов D3, D2, D1 или D0 в зависимости от состояния управляющих (адресных) входов A1–A0 (S1–S0). При Е=0 состояние выхода равно «0».

F M4_1 = E∙¬A1∙¬A0∙D0+E∙¬A1∙A0∙D1+ E∙A1∙¬A0∙D2+E∙A1∙A0∙D3.

Увеличение разрядности мультиплексоров

Разрядность мультиплексоров можно увеличивать линейно или каскадно (пирамидально).

Еще одним вариантом увеличения разрядности мультиплексоров является применение в первой ступени дешифратора. Старшие раз-ряды кода адреса декодируются дешифратором и его выходные сигналы служат сигналами разрешения для мультиплексоров. Так как в каждый момент времени разрешена работа только одного мультиплексора, то результирующий выходной сигнал можно получить объединением выходов всех мультиплексоров с помощью схемы ИЛИ.

Логическая схема мультиплексора М16_1Е приведена на рис. 26.

|

S3 |

S2 |

S1 |

S0 |

Q |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

2 |

|

0 |

0 |

1 |

1 |

3 |

|

0 |

1 |

0 |

0 |

4 |

|

0 |

1 |

0 |

1 |

5 |

|

0 |

1 |

1 |

0 |

6 |

|

0 |

1 |

1 |

1 |

7 |

|

1 |

0 |

0 |

0 |

8 |

|

1 |

0 |

0 |

1 |

9 |

|

1 |

0 |

1 |

0 |

10 |

|

1 |

0 |

1 |

1 |

11 |

|

1 |

1 |

0 |

0 |

12 |

|

1 |

1 |

0 |

1 |

13 |

|

1 |

1 |

1 |

0 |

14 |

|

1 |

1 |

1 |

1 |

15 |

Или

Реализация функций на мультиплексорах

На мультиплексорах достаточно просто можно реализовать любую функцию от заданного числа n аргументов (переменных).

При реализации (генерации) функций на мультиплексорах не требуется ни записи функции в СДНФ, ни минимизации функции.

Для реализации функции применяются таблицы истинности. Применяется три способа настройки мультиплексоров:

1. Число адресных входов m равно числу переменных n.

2. Число адресных входов m равно (n -1) для n переменных.

3. Применение дополнительных схем на входе мультиплексора.

В первом способе на адресные входы мультиплексора подают аргументы функции ХN, …, X1, а на информационные входы коды настройки – константы 0 и 1, в такой последовательности, которая

полностью копирует последовательность единиц и нулей таблицы истинности. На рис. 27 приведён пример воспроизведения функции «голосования» – мажоритарного элемента 2 из 3 на мультиплексоре М8_1Е.

Также применяется каскадирование мультиплексоров. Когда есть мультиплексоры по 4 входа, а надо реализовать функцию для 8 ми входов.

Таблица истинности для требуемой функции