- •Демультиплексоры, условные графические обозначения и применения.

- •Цап работающий по выходному току.

- •3. Полусумматор сумматор, его условное графическое обозначение и его применение.

- •4. Виды энергонезависимых запоминающих устройств.

- •6. Jk триггер

- •8. Одноразрядный сумматор.

- •9. Виды динамических запоминающих устройств

- •10. Шифраторы, условные графические обозначения и применения.

- •11. Ацп работающий на основе кодирования по разрядности.

- •12. Цифровой компаратор, его условное графическое обозначение и его применение.

- •13. Дешифраторы, условные графические обозначения и применения .

- •14. Ацп работающий последовательным подсчетом.

- •15. Виды микропроцессоров и их основные характеристики.

- •16. Виды запоминающих устройств и их особенности

- •17. Сравнительные характеристики сумматоров.

- •18. Двухтактовый rs-триггер, его условное графическое обозначение и применение.

- •19. Виды цап и апц, особенности их применения

- •20. Классификация триггеров, их применение в цифровых устройствах.

- •21. Виды счетчиков и область применения.

- •22. Регистр с последовательным приемом информации и параллельным распределением.

- •23. Реверсивный счетчик, условные графические обозначения и применения.

- •25. Триггеры

- •26. Мультиплексоры, условные графические обозначения и применения.

- •27. Асинхронный двоичный счетчик, его условное графическое обозначение и его применение.

- •28. Асинхронный rs триггер, его условное графическое обозначение и его применение.

- •29. Синхронный rs триггер, его условное графическое обозначение и его применение.

- •30. Архитектура микропроцессоров основные характеристики и особенности

- •31. Последовательный и параллельный интерфейс, их основные характеристики.

- •32. Энергозависимые запоминающие устройства. Флэш память, основные характеристики.

- •33. Сравнительные характеристики триггеров. Особенности применения триггеров.

- •34.Com и lpt порты, основные харакетристики, принципы работы.

- •35. Сравнительные характеристики сумматоров, Особенности применения триггеров.

- •36. Интегральные схемы, их применение в цифровых устройствах.

- •37. Принципы работы счетчиков, область применения.

17. Сравнительные характеристики сумматоров.

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

Сумматоры классифицируют по различным признакам.

В зависимости от системы счисления различают:-двоичные; -двоично-десятичные (в общем случае двоично-кодированные); -десятичные; -прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел:-одноразрядные, -многоразрядные.

По числу входов и выходов одноразрядных двоичных сумматоров:

четвертьсумматоры (элементы “сумма по модулю 2”; элементы “исключающее ИЛИ”), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд);

полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:-последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании; -параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

18. Двухтактовый rs-триггер, его условное графическое обозначение и применение.

Триггер- запоминающий элемент с двумя устойчивыми состояниями. Состояние триггера определяется по его выходному сигналу в зависимости от уровня последнего кодируется цифрами 0 или 1.

Двухтактовый RS-триггер- это тактовый запоминатель используется в регистровых сдвигах так как при перемещении информации из одного такта в другой, можно записать новую информацию в первый такт.

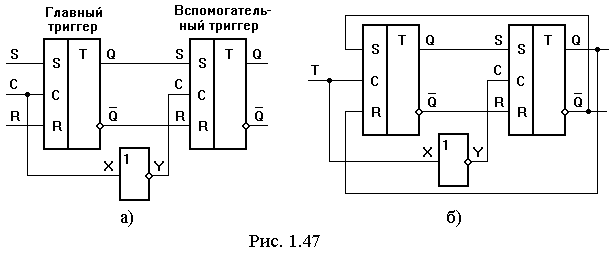

Двухтактный RS-триггер (рис. 1.47,а) состоит из двух триггеров: главного и вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера. Используя двухтактные RS-триггеры, можно построить JK-триггер. В JK-триггере устранена неопределенность, возникающая в RS-триггере при одновременном снятии активных логических сигналов с входов R и S.

На рисунке 1.47,б приведена схема счетного триггера, построенного на основе двухтактного RS-триггера.

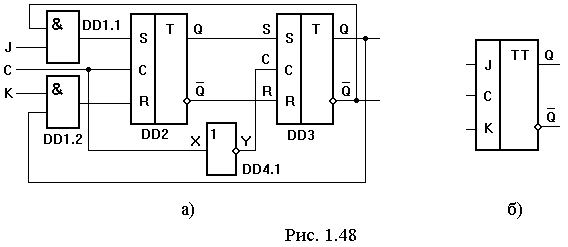

Функциональная

схема JK-триггера,

построенного с использованием

двухтактных (двухступенчатых)

RS-триггеров,

приведена на рисунке 1.48,а, а его условное

обозначение на принципиальных схемах

– на рисунке 1.48,б.

В условных обозначениях триггеров, построенных с использованием двухтактного синхронного RS-триггера, ставят две буквы Т. Если входы J и K данного триггера соединить вместе и подать на них сигнал логической единицы, а импульсы подавать на вход С, то получим счетный триггер.

Широкое распространение получили JK-триггеры, построенные с использованием синхронных RS-триггеров с динамическим управлением.

Применение

Выходной сигнал двухтактного триггера изменяется по спаду синхроимпульса, т.е. имеет место задержка. В отдельных случаях это может быть неприемлемо.

RS-триггер нашел широкое распространение в схемах ЭВМ. Одиночные триггеры этого типа часто используются в различных блоках управления. В асинхронных RS-триггерах имеется один существенный недостаток, обусловленный самой логикой их построения, т.е. в них сигналы R и S должны быть разнесены во времени. Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS-триггеры, Т-, JK-, D- триггеры и целый ряд комбинированных RST-, JKRS-, DRS-трштеров.