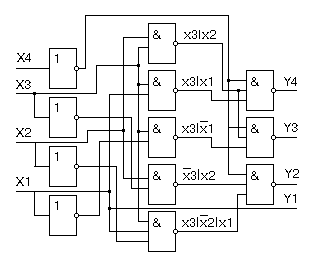

10.Преобразователь кода 8421 в 2421

|

являются запрещенными. Преобразователи кодов применяются в системах интерфейсов.

8421 |

2421 |

||||||||||||

X4 |

X3 |

X2 |

X1 |

Y4 |

Y3 |

Y2 |

Y1 |

||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||||||

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

||||||

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

||||||

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

||||||

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

||||||

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

||||||

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

||||||

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

||||||

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

||||||

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

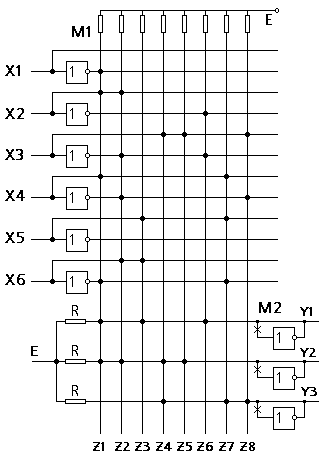

11.Программируемая логическая матрица (плм)

|

При записи программы в ПЛМ прожигаются плавкие предохранители, соединяющие транзисторы МДП с шинами матрицы. Матрица М1 называется матрицей конъюнкции. На горизонтальные шины подаются переменные. На вертикальных шинах образуются конъюнкции. На

вертикальных шинах появляется единичный сигнал только тогда, когда все транзисторы, включенные в узлы матрицы и подсоединенные к этой шине закрыты. В узлах матрицы включаются транзисторы МДП.

Прожигание программы в соответствии с назначением матрицы состоит в том, что прожигается плавкий предохранитель и транзистор, подсоединяется к узлу матрицы. Если на входы транзисторов подать нули, то они будут закрыты. Матрица М2 называется матрицей дизъюнкции.На ее горизонтальных шинах появляется сигнал в том случае, если снимать сигнал через инвертор.

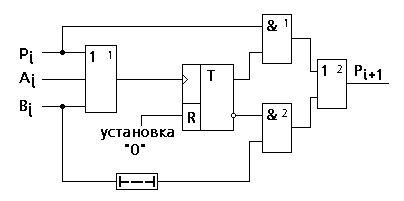

12.Накапливающий сумматор

Накапливающий сумматор является автоматом с памятью, т.е. слагаемые могут приходить поочередно в произвольные моменты времени и запоминаться в линиях задержки или в триггерах. Накапливающий. сумматор применяется в асинхронных устройствах, в которых слагаемые не привязаны к тактам тактового генератора.

|

ai |

bi |

Pi |

Si |

Pi+1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |