ответы на тесты, билеты / ответы на кр. часть 1 / Лекция 3

.docxЛекция 3. (Попов Р.И.)

1. Постройте структурную схему ЭВМ с одноуровневой системной шиной.

2. Постройте временную диаграмму цикла чтения из асинхронной памяти, с управляющими сигналами OE, WE, CS (ЛР1)

3. Постройте временную диаграмму цикла записи в асинхронную память, с управляющими сигналами OE, WE, CS (ЛР1)

4. Поясните назначение сигналов LB, UB (Lower Byte, Upper Byte) на шине с шириной данных 16 бит.

5. Постройте временную диаграмму цикла чтения на синхронной шине с подтверждением (REQ- ACK)

6. Постройте временную диаграмму цикла записи на синхронной шине с подтверждением (REQ- ACK)

7. Назовите отличительные особенности в организации внутрикристальных шин (SoC).

Внутрикристальные шины могут быть гораздо шире, чем шины на печатных платах. Это позволяет повысить эффективность передачи и уменьшить скорость модуляции. Другими словами, с увеличением ширины шины растет пропускная способность, а с уменьшением скорости модуляции снижается энергопотребление.

8. Нарисуйте схему реализации приемопередатчика SPI-SLAVE на основе сдвигающего регистра с параллельной загрузкой.

9. Поясните, каким образом осуществляется выбор SLAVE-устройства на шине SPI.

Используется сигнал SS – выбор ведомого (Slave Select). Выход SS MASTER-устройства соединён со входами SS SLAVE-устройств. Переводом того или иного сигнала SS в низкое состояние,MASTER задает, с какой подчиненной ИС он будет обмениваться данными.

10. Нарисуйте схему адресного селектора, обеспечивающего выборку микросхем SRAM (256 байт) согласно следующей карте адресного пространства 0x00-0xFF: SRAM1 ; 0x100 – 0x17F: SRAM2; 0x180-0x27F: SRAM3

11. Каким образом может использоваться счетчик с модулем пересчета N в составе приемопередатчиков последовательных интерфейсов. Нарисуйте схему делителя частоты с устанавливаемым коэффициентом деления.

12. Постройте временную диаграмму, иллюстрирующую последовательность передачи слова данных по интерфейсу UART.

Упрощенный вариант:

13. Поясните назначение бита четности при последовательной передаче данных.

Би́том чётности называют контрольный бит, служащий для проверки общей чётности двоичного числа (чётности количества единичных битов в числе). Бит чётности или контрольный разряд формируется при выполнении операции «Исключающее-ИЛИ» поразрядно. Рассмотрим схему, использующую девятибитные кодовые слова, состоящие из восьми бит данных, за которыми следует бит чётности. Число 10111101 содержит 6 '1' битов. Бит чётности будет 0, получаем кодовое слово 101111010;Число 01110011 содержит 5 '1' битов. Бит чётности будет 1, получаем кодовое слово 011100111.

Этот бит служит для обнаружения ошибок, которые могут возникнуть при передаче данных из-за помех на линии. Приемное устройство заново вычисляет четность данных и сравнивает результат с принятым битом четности. Если четность не совпала, то считается, что данные переданы с ошибкой.

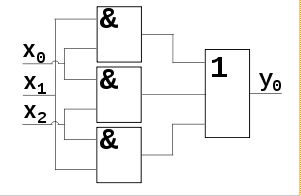

14. Укажите назначение схем мажоритарного контроля при построении приемников последовательных интерфейсов. Нарисуйте схему мажоритарного контроля с тремя входами.

А) Мажорита́рный элеме́нт (мажоритарный клапан, переключатель по большинству, ППБ) — логический элемент из класса пороговых, с чётным или нечётным числом входов и одним выходным сигналом, значение которого совпадает со значением, на большинстве входов

Б)

Задача

маскирования (исправления) ошибок.

В этом случае

наличие ошибок определенного типа и

количества не нарушает работу устройства,

поскольку их влияние устраняется

автоматически. В этой области используется,

например, троекратное резервирование

устройств с выработкой результата путем

«голосования» с помощью мажоритарных

элементов. Эти элементы вырабатывают

выходные данные «по большинству»

входных. Если из трех устройств одно

стало работать неправильно, это не

скажется на результате. Только ошибка

двух из трех каналов проявляется в

результате.

15. Поясните назначение стартовых и стоповых последовательностей в асинхронных последовательных интерфейсах.

Передача каждого байта начинается со старт-бита, сигнализирующего приемнику о начале посылки, за которым следуют биты данных и, возможно, бит четности (Parity). Завершает посылку стоп-бит, гарантирующий паузу между посылками.

Стартовый сигнал изменяет состояние линии интерфейса и служит для запуска генератора в приемнике.

Стоповый сигнал переводит линию в исходное состояние и останавливает работу генератора.

Суть стартстопного принципа управления состоит в том, что стартовый импульс в сообщении запускает местный синхрогенератор приемника, который работает на частоте передатчика, и линия стробируется в соответствии с частотой местного синхронизатора, а стоповый импульс в сообщении останавливает синхрогенератор.

16. Поясните различие между синхронными и асинхронными последовательными интерфейсами.

Организация асинхронного последовательного обмена данными с внешним устройством осложняется тем, что на передающей и приемной стороне последовательной линии связи используются настроенные на одну частоту, но физически разные генераторы тактовых импульсов и, следовательно, общая синхронизация отсутствует.

В синхронных интерфейсах сигнал синхронизации передается по одной из линий. Асинхронные интерфейсы тактируется от внутренних генераторов приемника и передатчика.

Синхронные:

PS/2

SPI

I2C

Асинхронные:

UART

USB

Ethernet

17. Назовите причины, по которым параллельные интерфейсы не используются для передачи данных на значительные расстояния.

Из-за проблем с разфазировкой тактового сигнала, протяженность системной шины должна быть небольшой

Проблемы использования параллельных интерфейсов:

-

Сложность синхронизации сигналов во всех линиях

-

Сложность конструкции

-

Цена

Термин "параллельный интерфейс" означает, что данные передаются не побитно, а в виде машинных слов. Для каждого разряда байта в кабеле интерфейса предназначен отдельный провод. Кроме того, параллельно данным передается различная служебная информация. Пропускная способность параллельного интерфейса выше, чем у последовательного, однако, больше и суммарная длина кабелей (при машинном слове в 8 бит в 8 раз больше соответственно, чем у последовательного интерфейса, не считая служебные шины).

Ко всему прочему параллельная передача плохо поддаётся синхронизации, поскольку очевидно, что на большом расстоянии биты одного слова будут доходить к приёмнику с разной задержкой. Таким образом, потребуется как минимум установка буфера для сигналов, а так же некоторые сигналы подтверждения и лишний такт генератора, на котором будет открываться буфер.

18. Нарисуйте структурную схему цифрового устройства, построенного по принципу FSMD. Поясните принцип её работы.