- •Двоичная система счисления

- •Преобразование двоичных чисел в десятичные

- •Преобразование десятичных чисел в двоичные

- •Восьмеричная система счисления.

- •Шестнадцатеричная система счисления

- •Практическая работа №2. Арифметическое сложение двоичных чисел в форме с плавающей и фиксированной запятой.

- •Числа с фиксированной и плавающей запятой

- •Числа с фиксированной запятой

- •Числа с плавающей запятой

- •Двоичная арифметика

- •Сложение

- •Вычитание

- •Умножение

- •Деление

- •Прямой, обратный и дополнительный коды

- •Прямой код

- •Обратный код

- •Дополнительный код

- •Сложение и вычитание в дополнительном коде

- •Признак переполнения разрядной сетки

- •Практическая работа №3. Минимизация переключательной функции методом карт Карно.

- •Лабораторная работа №1. Исследование преобразователя двоичного кода.

- •Лабораторная работа № 2. Изучение работы виртуального логического конвертора

- •Теоретические сведения физические основы эвм

- •Решение задач на тему: логические схемы

- •Система electronics workbench

- •Лабораторная работа № 3. Виртуальный генератор слова (word generator). Вычитание

- •Краткая теория

- •Вычитание

- •Лабораторная работа №4. Исследование работы асинхронного и синхронного rs-триггера

- •Краткая теория

- •Краткая теория

- •Лабораторная работа №6. Исследование схемы контроля на четность.

- •Краткая теория

- •Лабораторная работа №7. Изучение кода Хэмминга.

- •Краткая теория.

- •Литература:

Вычитание

Вычитание числа В из А выполняется путем суммирования отрицательного числа В в дополнительном коде с числом А. Представление отрицательного двоичного числа можно получить путем инвертирования всех битов числа и добавлением 1. Прибавление этой единицы эффективно реализуется в полном сумматоре путем замены его первого каскада (полусумматора) на полный сумматор, вход переноса которого подключается к напряжению с уровнем логической 1.

Контрольные вопросы и задания

Объяснить предназначение виртуального генератора слов.

Перечислить основные функции генератора слов.

Объяснить, почему выбраны шестнадцатиразрядные числа 0, 1, 11, 12, 13, 14, 15, 16, 17 для анализа работы сумматора.

Постройте пятиразрядный сумматор и проанализируйте с помощью генератора слов.

Какие шестнадцатиразрядные числа необходимо ввести для анализа работы сумматора?

Как обеспечить вычитание двух чисел?

Лабораторная работа №4. Исследование работы асинхронного и синхронного rs-триггера

Цель: Изучение назначения и принцип работы асинхронного и синхронного RS-триггера.

Оборудование: Электронная лаборатория Electronics Workbench.

Краткая теория

Любая информация в компьютере представляется в двоичном виде, поэтому рассмотрим запоминание и хранение элементарной порции информации - одного бита. Электронная схема, запоминающая один бит информации, называется триггером.

Триггеры имеют два устойчивых состояния. Эти состояния определяются по логическим уровням на выходах триггера. Триггер снабжается двумя выходами: прямым Q и инверсным Q. Состояние триггера определяет логический уровень на выходе Q. Говорят, что триггер находится в состоянии логической единицы, если на выходе Q уровень напряжения, соответствующий логической единице.

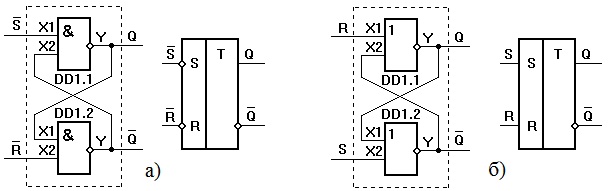

Наибольшее

распространение получили RS-триггеры,

построенные на логических элементах

2И-НЕ (рисунок 35, а) или 2ИЛИ-НЕ (рисунок

35, б). RS-триггер имеет два логических

входа: R - установка 0 (от слова reset); S -

установка 1 (от слова set).

Рис. 35

Рассмотри работу триггера, построенного на логических элементах 2ИЛИ-НЕ. Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль - со входа R, другой - с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния.

Для описания работы триггера используют таблицу состояний (переходов).

Обозначим:

Q(t) - состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

Q(t+1) - состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ.

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

0 |

0 |

0 |

0 |

Режим хранения информации R=S=0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

Режим установки нуля R=1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

* |

R=S=1 запрещённая комбинация |

1 |

1 |

1 |

* |

Таблица переходов RS триггера в базисе И-НЕ.

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

0 |

0 |

0 |

* |

R=S=0 запрещённая комбинация |

0 |

0 |

1 |

* |

|

0 |

1 |

0 |

0 |

Режим установки нуля R=0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

Режим установки единицы S=0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

Режим хранения информации R=S=0 |

Рассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Рис.36

На рисунках 36а, в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 36,б.

Рассмотрим функциональную схему синхронного RS-триггера, приведенную на рисунке 36а. При С=0 на входах R, S асинхронного триггера на элементах DD1.1 и DD1.2 действуют сигналы логического нуля (логический нуль является пассивным логическим уровнем для логических элементов 2ИЛИ-НЕ), поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется. При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше асинхронный RS-триггер с прямыми входами. Рассмотренный только что синхронный RS-триггер относится к триггерам со статическим управлением.

Таблица переходов синхронного RS-триггера.

R |

S |

C |

Q(t) |

Q(t+1) |

Пояснения |

0 |

0 |

1 |

0 |

0 |

Режим хранения информации R = S = 0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

Режим установки единицы S =1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

Режим установки нуля R=1 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

* |

R = S = 1 запрещённая комбинация |

1 |

1 |

1 |

1 |

* |

Контрольные вопросы и задания

Что такое триггер, какого типа они бывают ?

Проведите исследования приведенных выше схем триггеров.

Лабораторная работа №5.

Исследование работы D-, T-и JK-триггеров

Цель: Изучение назначения и принцип работы D- и T-триггеров.

Оборудование: Электронная лаборатория Electronics Workbench.