Проектирование управляющих автоматов. Общие принципы проектирования

Управляющий автомат проектируется по заданной ГСА с использованием двух моделей Мура и Мили с различной стратегией кодирования, с учетом используемых элементов памяти. Выбирается наиболее экономичная реализация и разрабатывается для нее функциональная логическая схема. Сложность схемы рассчитывается с использованием пересчета в эквивалентные корпуса.

Для расчета схемы:

Построить таблицу переходов/выводов

Составить общее уравнение переходов/выводов

Рассчитать стоимость схемы для выбранной стратегии кодирования

Управляющий автомат Мура.

Состояниями в модели Мура обозначаются операторные вершины и входы «ждущих вершин».

Состояния обозначаются q0, q1, q2, … - последовательно от начальной ждущей вершины с сигналом запуска автомата х0.

Циклы ожидания внешних событий могут не содержать операторные вершины – отмечается вход или выход любой условной вершины.

Если с входом условной вершины соединяется два или более выходов операторных или других условных вершин, то вход отмечается, как узел Q, нумерация узлов произвольная.

Память состояний автомата Мура может быть выполнена:

На DV-регистрах с использованием унитарного кодирования состояний

На DV-регистрах с использованием максимального кодирования состояний

На сдвигающих регистрах, используя унитарное кодирование. Регистр организован, как суммирующий сдвигатель влево, при сбросе регистра в мл. разряд записывается «1»

На регистре-счетчике, используя максимальное кодирование состояний. При сбросе счетчика устанавливается начальное состояние, соответствующее выбранному при кодировании коду.

Составить структурную таблицу переходов/выходов, учитывая выделение состояний qi и Qi. Узлы учитываются в условиях перехода, как промежуточные «мгновенные» состояния. На основе структурной таблицы составляются общие для всех вариантов схем уравнения переходов:

QI <= Q*X

где: QI– следующее состояние

Q – текущее состояние

Х – конъюнкция переменных хi, обеспечивающих условия перехода между состояниями

Отдельно от каждого варианта организации памяти выполняются расчеты схемы, оформляются таблицы оценки сложности и преобразования кодов q в значение функций управления на входах элементов памяти.

Для всех регистров используются информационные входы diзаписи:

di= 1 по синхросигналу записыв. в i разряд «1»

di= 0 – записывается «0»

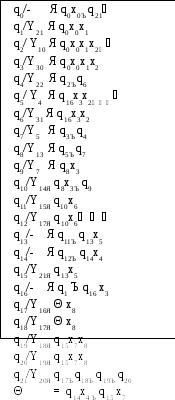

Таблица переходов/выходов

|

|

x |

|

q//Θ |

Y |

|

q0 |

x0 x0x1 x0x1x2 x0x1x2 |

|

q0 q1 q3 q2 |

– Y21 Y30 Y10 |

|

q1 |

1 |

|

q16 |

– |

|

q2 |

1 |

|

q4

|

Y22 |

|

q3 |

1 |

|

q7 |

Y5 |

|

q4 |

1

|

|

q7

|

Y5 |

|

q5 |

1 |

|

q8

|

Y13

|

|

q6 |

1 |

|

q4

|

Y22

|

|

q7 |

1 |

|

q8

|

Y13

|

|

q8 |

x3 x3 |

|

q9 q10 |

Y17 Y14 |

|

q9 |

1 |

|

q10 |

Y14 |

|

q10 |

x6 x6 |

|

q11 q12 |

Y15 Y17 |

|

q11 |

1 |

|

q13 |

– |

|

q12 |

1 |

|

q14 |

– |

|

q13 |

x5 x5 |

|

q13 q15

|

– Y21 |

|

q14 |

x4 x4 |

|

q14 Θ |

– – |

|

q15 |

x7 x7 x8 x7 x8 |

|

Θ q20 q19 |

– Y19 Y18 |

|

q16 |

x3 x3 x2 x3 x2 |

|

q16 q6 q5 |

– Y31 Y4 |

|

q17 |

1 |

|

q21

|

Y20

|

|

q18 |

1 |

|

q21

|

Y20

|

|

q19 |

1 |

|

q21

|

Y20

|

|

q20 |

1 |

|

q21 |

Y20 |

|

q20 |

1 |

|

q21 |

Y20 |

|

q21 |

1 |

|

q0 |

–

|

|

Θ |

x8 x8 |

|

q17 q18

|

Y16 Y17

|

q/Θ

q/Θ