- •Электровакуумные приборы

- •Электронная эмиссия

- •Катоды электронных ламп

- •Электровакуумный диод

- •Четырехэлектродная лампа – тетрод

- •Полевой транзистор

- •Биполярный транзистор

- •Вентили

- •Интегральные схемы

- •Реализация булевых функций

- •Мультиплексоры

- •Декодеры

- •Компараторы

- •Программируемые логические матрицы

- •Арифметические схемы

- •Схемы сдвига

- •Сумматоры

- •Арифметико-логические устройства

- •Тактовые генераторы

- •С инхронные sr-защелки.

- •Синхронные d-защелки.

- •Триггеры.

- •Регистры

- •Организация памяти

- •Адреса памяти

- •Упорядочение байтов

- •Код исправления ошибок

- •Типы оперативной памяти

- •Энергонезависимая память

- •Микросхемы процессоров

- •Компьютерные шины

- •Принципы работы шины.

- •Ширина шины

- •Синхронизация шины

- •С инхронные шины

- •Асинхронные шины

- •Арбитраж шины

- •Рассмотрим сначала централизованный арбитраж.

- •Магнитные диски

- •Дискеты

Асинхронные шины

Хотя использовать синхронные шипы благодаря дискретным временным интервалам достаточно удобно, здесь все же есть некоторые проблемы.

Например, если процессор и память способны закончить передачу за 3,1 цикла, они вынуждены продлить ее до 4,0 циклов, поскольку неполные циклы запрещены.

Еще хуже то, что если однажды был выбран определенный цикл шины и в соответствии с ним разработала память и карты ввода-вывода, то и будущем трудно делать технологические усовершенствования.

Например, предположим, что через несколько лет после выпуска системы, изображенной на рис. 3.35, появилась новая память с временем доступа не 15, а 8 не. Это время позволяет избавиться от периода ожидания и увеличить скорость работы машины. А теперь представим, что появилась память с временем доступа 4 не. При утом улучшения производительности уже не будет, поскольку в данной разработке минимальное время чтения — 2 цикла.

Если синхронная шина соединяет ряд устройств, одни из которых работают быстро, а другие — медленно, шина подстраивается под самое медленное устройство, а более быстрые не могут использовать свой потенциал полностью.

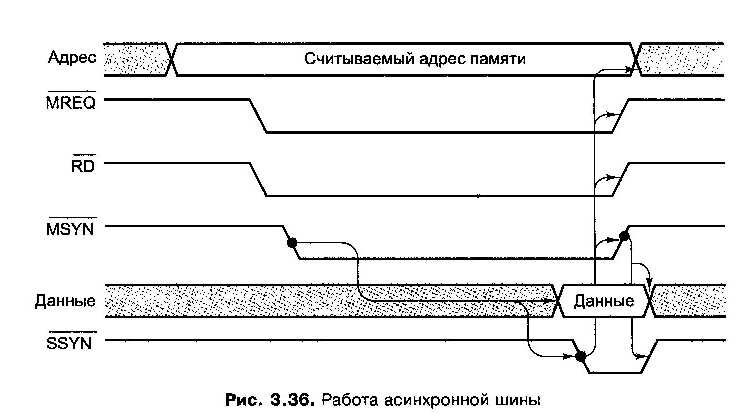

По этой причине были разработаны асинхронные шины, то есть шины без задающего генератора (рис. 3,36). Здесь ничего не привязывается к генератору. Когда задающее устройство устанавливает адрес, сигнал MREQ, RD или любой другой требуемый сигнал, оно выдает специальный синхронизирующий сигнал MSYN (Master SYNchronization- мастер, ведущий). Когда подчиненное устройство получает этот сигнал, оно начинает выполнять свою работу настолько быстро, насколько это возможно.

К огда

работа заканчивается, подчиненное

устройство пылает сигнал SSYN (Slave

SYNchronization – раб, ведомый), который означает

для задающего устройства, что данные

доступны. Оно фиксирует их, а затем

сбрасывает адресные линии вместе с

сигналами MREQ, RD и MSYN.

огда

работа заканчивается, подчиненное

устройство пылает сигнал SSYN (Slave

SYNchronization – раб, ведомый), который означает

для задающего устройства, что данные

доступны. Оно фиксирует их, а затем

сбрасывает адресные линии вместе с

сигналами MREQ, RD и MSYN.

Сброс сигнала MSYN означает для подчиненного устройства, что цикл закончен, поэтому устройство сбрасывает сигнал SSYN, и все возвращается к первоначальному состоянию, когда все сигналы сброшены.

Стрелочки на временных диаграммах асинхронных шин (а иногда и синхронных шин) показывают причину и следствие какого-либо действия (см. рис. 3.36).

Установка сигнала MSYN приводит к включению информационных линий, а также к установке сигнала SSYN.

Установка сигнала SSYN, в свою очередь, вызывает отключение адресных линий, а также линий MREQ, RD и MSYN.

Наконец, сброс сигнала MSYN вызывает сброс сигнала SSYN, и на этом процесс считывания заканчивается.

Набор таких взаимообусловленных сигналов называется полным квитированием. Здесь, в сущности, наблюдается 4 события:

1.Установка сигнала MSYN.

2.Установка сигнала SSYN в ответ на сигнал MSYN.

3.Сброс сигнала MSYN в ответ на сигнал SSYN,

4,Сброс сигнала SSYN в ответ на сброс сигнала MSYN.

Важно, что взаимозависимость сигналов не является синхронной. Каждое событие вызывается предыдущим событием, а не импульсами генератора.

Если какая-то пара устройств (задающее и подчиненное) работает медленно, это никак не влияет на другую пару устройств, которая может работать гораздо быстрее.

Несмотря на очевидные преимущества асинхронной шины, большинство шин являются синхронными, поскольку синхронную систему построить проще, чем асинхронную. Кроме того, в разработку синхронных шин вложено очень много средств.