- •Электровакуумные приборы

- •Электронная эмиссия

- •Катоды электронных ламп

- •Электровакуумный диод

- •Четырехэлектродная лампа – тетрод

- •Полевой транзистор

- •Биполярный транзистор

- •Вентили

- •Интегральные схемы

- •Реализация булевых функций

- •Мультиплексоры

- •Декодеры

- •Компараторы

- •Программируемые логические матрицы

- •Арифметические схемы

- •Схемы сдвига

- •Сумматоры

- •Арифметико-логические устройства

- •Тактовые генераторы

- •С инхронные sr-защелки.

- •Синхронные d-защелки.

- •Триггеры.

- •Регистры

- •Организация памяти

- •Адреса памяти

- •Упорядочение байтов

- •Код исправления ошибок

- •Типы оперативной памяти

- •Энергонезависимая память

- •Микросхемы процессоров

- •Компьютерные шины

- •Принципы работы шины.

- •Ширина шины

- •Синхронизация шины

- •С инхронные шины

- •Асинхронные шины

- •Арбитраж шины

- •Рассмотрим сначала централизованный арбитраж.

- •Магнитные диски

- •Дискеты

Арифметико-логические устройства

Большинство компьютеров содержат одну схему для выполнения над двумя машинными словами операций И, ИЛИ и сложения.

О бычно

эта схема для n-разрядных

слов состоит из n

идентичных схем — по одной для каждой

битовой позиции. На рисунке представлена

такая схема, которая называется

арифметико-лотческим устройством (АЛУ).

бычно

эта схема для n-разрядных

слов состоит из n

идентичных схем — по одной для каждой

битовой позиции. На рисунке представлена

такая схема, которая называется

арифметико-лотческим устройством (АЛУ).

Это устройство может вычислять одну из 4-х следующих функций:

A И B;

А ИЛИ В;

;

А + В (арифметическая сумма)

Выбор реализуемой функции зависит от двоичного кода формируемого сигналами на линиях F0 и F1: 00, 01, 10 или 11.

В левом нижнем углу схемы находится двухразрядный декодер, который генерирует сигналы разрешения (1) на одну из четырех выходных линий, которая разрешает прохождение выходного сигнал выбранной функции через последний вентиль ИЛИ.

В верху схемы находится логическое устройство для вычисления функций А И В, А ИЛИ В и , но только один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из линий разрешения выбрал декодер. Так как ровно один из выходных сигналов декодера может быть равен 1, то и запускаться будет ровно один из трех вентилей И, или два вентиля И на выходе полного сумматора, независимо от значений А и В.

АЛУ может выполнять не

только логические и арифметические

операции над переменными

А и В, но и делать их равными нулю, отрицая

ENA

(сигнал разрешения

А)

или

ENB

(сигнал разрешения В).

Можно

также выполнять операции с

![]() ,

установив сигнал

INVA

(инверсия А).

,

установив сигнал

INVA

(инверсия А).

При нормальных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INVA равен 0. В этом случае А и В просто поступают в логическое устройство без изменений,

В

нижнем правом углу находится полный

сумматор для подсчета суммы А

и В, а

также для выполнения переносов. Переносы

необходимы, поскольку несколько

таких схем могут быть соединены для

выполнения операций над целыми словами.

нижнем правом углу находится полный

сумматор для подсчета суммы А

и В, а

также для выполнения переносов. Переносы

необходимы, поскольку несколько

таких схем могут быть соединены для

выполнения операций над целыми словами.

Одноразрядные схемы, подобные показанной на рисунке называются разрядными микропроцессорными секциями. Они позволяют разработчику строить АЛУ любой разрядности.

Схема 8-разрядного АЛУ, составленного из восьми одноразрядных секций имеет вид:

Сигнал INС (инкримент - увеличение на единицу) нужен только для операций сложения. Он дает возможность вычислять такие суммы, как A+1 и A + B +1.

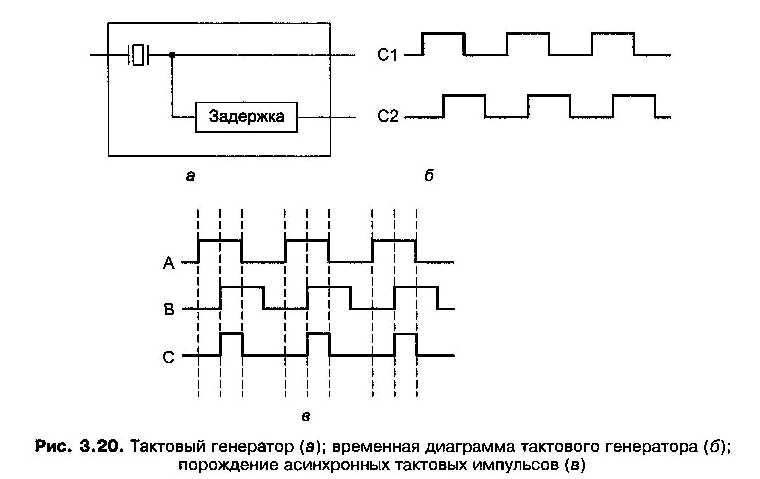

Тактовые генераторы

Порядок выполнение операций во многих цифровых схемах определяет работу всей схемы. Иногда одна операция должна предшествовать другой, иногда две операции должны происходить одновременно.

Для контроля временных параметров в цифровые схемы встраиваются тактовые генераторы, позволяющие обеспечить синхронизацию.

Тактовый генератор — это схема, которая вырабатывает серию импульсов. Все импульсы одинаковы по длительности. Интервалы между последовательными импульсами также одинаковы.

Временной интервал между началом одного импульса и началом следующего называется временем такта. Частота импульсов обычно составляет от 1 до 500 МГц, что соответствует времени такта от 1000 до 2 нс. Частота тактового генератора обычно контролируется кварцевым генератором, позволяющим добиться высокой точности.

В компьютере за время одного такта может произойти множество событий. Если они должны осуществляться в определенном порядке, то такт следует разделить на подтакты.

Чтобы достичь лучшего разрешения, чем у основного тактового генератора, нужно сделать ответвление от задающей линии тактового генератора и вставить схему, создающую определенную временную задержку.

Т

ак

порождается вторичный

сигнал тактового генератора, сдвинутый

по фазе относительно первичного

сигнала.

ак

порождается вторичный

сигнал тактового генератора, сдвинутый

по фазе относительно первичного

сигнала.

Временная диаграмма, показанная на рисунке, предлагает четыре точки начала отсчета времени для дискретных событий:

Фронт C1 ;

Спад C1;

Фронт С2.

Спад С2,

Связав различные события с разными перепадами (фронтами и спадами), можно достичь требуемой последовательности выполнения действий. Если в пределах одного такта нужно более четырех точек начала отсчета, можно сделать еще несколько ответвлений от задающей линии с различным временем задержки.

В некоторых схемах важны временные интервалы, а не дискретные моменты времени. Например, некоторое событие может происходить не на фронте импульса, а в любое время, когда уровень импульса С1 высокий. Другое событие может происходить только в том случае, когда уровень импульса С2 высокий.

Если

необходимо более двух интервалов, нужно

предоставить больше линий передачи

синхронизирующих импульсов или сделать

так, чтобы состояния с высоким

уровнем импульса у двух тактовых

генераторов частично пересекались во

времени.

В последнем случае можно выделить 4

отдельных интервала:

![]() и

и

![]() ,

и

,

и

![]() ,

,

![]() и

,

и

,

и

,

и

,

Тактовые генераторы могут быть синхронными. В этом случае время существования импульса с высоким уровнем равно времени существования импульса с низким уровнем (см. рис. 3.20т б).

Чтобы получить асинхронную серию импульсов (см. сигнал С на рис. 3.20, в), нужно сдвинуть сигнал задающего генератора, использовав цепь задержки. Затем нужно соединить полученный сигнал с изначальным сигналом с помощью логической функции И.