- •1.Основные термины и понятия.

- •Системы обработки данных

- •2.Основные факторы,

- •3.Определяющие принципы организации эвм

- •2 Фактор

- •3 Фактор

- •Типы компьютеров

- •Одноразовые компьютеры

- •Микроконтроллеры

- •Игровые компьютеры

- •Персональные компьютеры

- •Серверы

- •Комплексы рабочих станций

- •Мэйнфреймы

- •Структурная организация компьютера.

- •Система команд

- •2 Организация системных шин в компьютере

- •2.1 Передача данных в компьютере

- •Шины бывают следующих типов:

- •Параллельные шины

- •Последовательные шины

- •2.2 Общая шина

- •2.3 Системные шины fsb, qpi и HyperTransport

- •2.4 Шина pci

- •2.5 Шина pci Express

- •2.6 Последовательные шины Serial ata и usb

- •3 Организации памяти в эвм

- •3.1 Иерархическая организация памяти и принцип локальности ссылок

- •3.2 Взаимодействие процессора и различных уровней памяти

- •3.3 Адресная память

- •Латентность памяти и тайминги [20]

- •3.4 Ассоциативная память

- •3.5 Организация кэш-памяти

- •3.5.2 Типы кэш-памяти

- •Кэш с прямым отображением

- •Полностью ассоциативный кэш

- •Множественно-ассоциативный кэш

- •3.5.4 Дисковая кэш-память

- •3.7 Целостность данных

- •Методы обеспечения целостности данных:

- •3.8. Когерентность данных в мультипроцессорных системах

- •3.9. Эксклюзивная и инклюзивная организация кэш-памяти

- •3.4 Ассоциативная память

- •Р и с. 3.4. Ассоциативная память

- •3.5 Организация кэш-памяти

- •3.5.2 Типы кэш-памяти

- •К эш с прямым отображением

- •3.5.3 Множественно-ассоциативная четырехканальная кэш-память процессора i486

- •3.5.4 Дисковая кэш-память

- •Магнитные диски

- •Дискеты

- •Паралельные вычислительные сиситемы

- •Матричная система

- •Векторно - конвейерный принцип обработки данных

- •Прогнозирование ветвлений

- •Многопроцессорные архитектуры

- •Многомашинные вс

- •Системы с массовым параллелизмом

- •Кластерные системы

- •Многоядерная архитектура (Multicore)

- •Проблемы Multicore

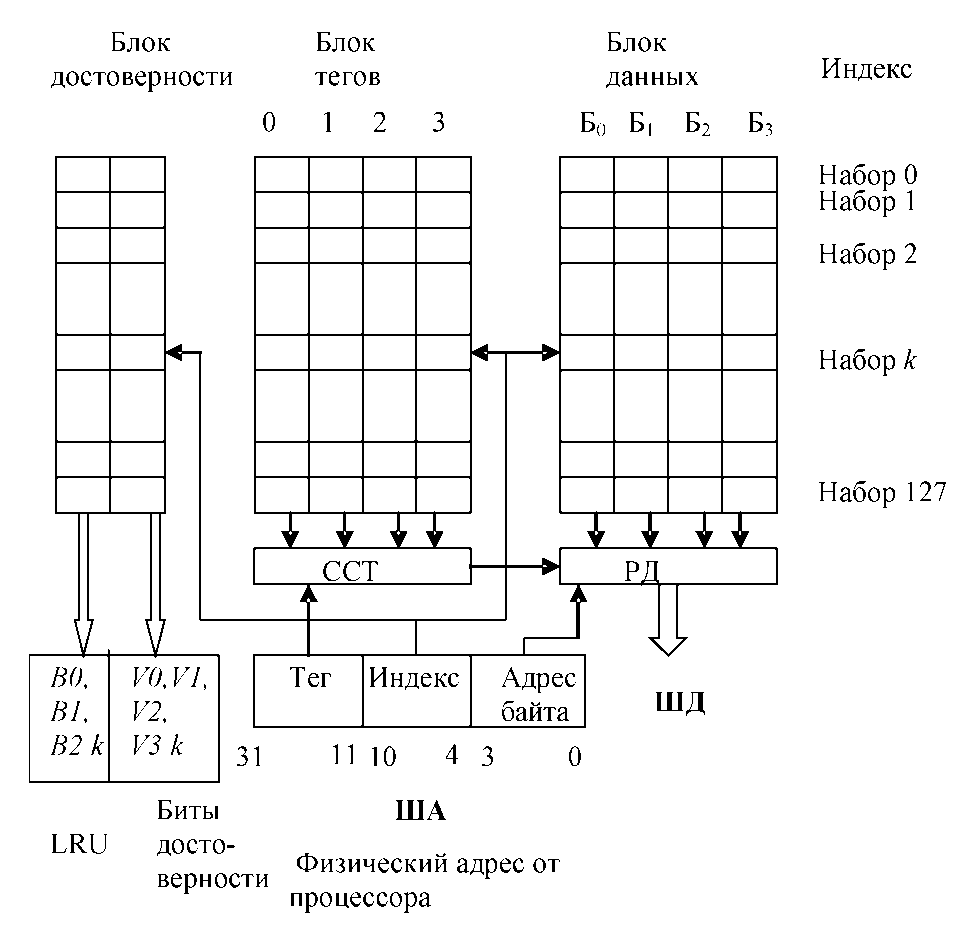

3.5.3 Множественно-ассоциативная четырехканальная кэш-память процессора i486

В современных процессорах используется 4-х, 6-ти и 8-ми канальная кэш-память.

Увеличение числа каналов (входов) кэш-памяти приводит к быстрому увеличению сложности аппаратной реализации той части кэша, которая обеспечивает ассоциативный поиск строк по тегам.

Рассмотрим типичную организацию кэш-памяти первого уровня для данных на примере процессора Intel i486 (рис. 3.9).

Строка кэш-памяти содержит 16 байт. Кэш состоит из блока данных, блока тегов и блока

Р и с. 3.9. Четырехвходовая множественно-ассоциативная

кэш-память

и с. 3.9. Четырехвходовая множественно-ассоциативная

кэш-память

процессора i486

достоверности. Блок данных кэш-памяти разбит на 128 непересекающихся подмножеств по 4 строки в каждом подмножестве. Следовательно, это четырехканальная кэш-память

(4-way cache). Каждому входу соответствует банк памяти Бо, Б1, Б2, Б3. Четыре строки с одним и

тем же индексом k образуют набор k. Таким образом, общая емкость кэш-памяти равна: 16 байт х 4 х 128 = 8192 байта или 8 КВ.

Физический адрес, поступающий от процессора, содержит три поля:

7-ми битовый индекс, адресующий набор;

4-х битовый адрес байта внутри строки;

21-но битовый тег строки, который заносится в блок тегов.

Сначала по индексу выбирается соответствующий набор k. Затем

в блоке тегов выбираются четыре тега, соответствующие строкам набора k. Ассоциативная схема сравнения тегов ССТ одновременно сравнивает тег в физическом адресе с четырьмя тегами из кэш-памяти. В случае совпадения тегов в регистр данных РД передается нужная строка из блока данных, а 4 младших разряда физического адреса выбирают нужный байт из 16 байтов строки.

Кроме того, в кэше имеется блок достоверности, также разделенный на 128 наборов. Каждый набор k состоит из двух полей:

4 бита достоверности V0, V1, V2, V3/k для каждой из строк k-го набора;

3 бита B0,B1,B2/k для алгоритма LRU замещения строк k-го набора, который будет рассмотрен ниже.

Биты достоверности используются для контроля целостности данных, о чем пойдет речь дальше.

Замещение ненужных строк при кэш-промахах производится по специальному алгоритму. Чаще всего используются LRU (Least Recently Used) - «наиболее давнее использование» и LFU (Least Frequently Used) - «наименее частое использование». В данной кэш-памяти применен алгоритм LRU. Он замещает ту строку в кэше, к которой дольше всего не было обращений. Биты B0,B1,B2/k содержат предысторию обращений к строкам набора k.

3.5.4 Дисковая кэш-память

Идея кэширования распространена и на другие устройства компьютера. В первую очередь это касается жестких дисков.

Возможны два варианта:

операционная система использует часть оперативной памяти в качестве кэша дисковых операций для внешних устройств, не обладающих собственной кэш-памятью, в том числе жестких дисков, flash- памяти и гибких дисков;

используется отдельная дисковая кэш-память объемом от 8 до 64 Мбайт.

Во втором случае контроллер дисковой кэш-памяти пересылает между ОП и винчестером файлы, содержащие сектора или дорожки диска.

Устройства чтения CD/DVD/BD-дисков также кэшируют прочитанную информацию для ускорения повторного обращения.

Применение кэширования внешних накопителей обусловлено следующими факторами:

скорость доступа процессора к оперативной памяти во много раз больше, чем к памяти внешних накопителей;

некоторые блоки памяти внешних накопителей используются несколькими процессами одновременно, и имеет смысл прочитать блок один раз, а затем хранить его копию блока в оперативной памяти для всех процессов.

Дисковая кэш-память использует ассоциативный принцип поиска данных, а также обнаружение тройных и исправление двойных ошибок.