- •Введение

- •Цели и задачи курса

- •1. Общие сведения о вычислительных машинах и вычислительных системах

- •1.1. Основные понятия и определения

- •1.2. Классификация эвм по назначению и типу

- •1.3. Типы эвм

- •1.4. Основные принципы организации вычислительных машин и систем

- •1.5. Основные характеристики вычислительных машин и систем

- •1.5.1 Стоимость и цена аппаратного обеспечения

- •1.5.2. Производительность вычислительных машин и систем

- •Контрольные вопросы

- •2. Фукциональный состав и назначение основных устройств вм

- •2.2. Назначение шин, шина с тремя состояниями

- •2.3. Назначение устройств ввода-вывода, способы информационного обмена

- •Контрольные вопросы

- •3. Организация процессоров

- •3.1. Введение в функциональную организацию процессора

- •3.2. Операционный блок

- •3.3. Блок управления

- •3.4. Устройства управления процессора

- •3.4.1. Классификация уу

- •3.4.2. Аппаратные уу

- •3.4.3. Микропрограммные уу

- •3.5. Интерфейсный блок

- •3.6. Назначение стека

- •Контрольные вопросы

- •4. Система команд и адресация данных

- •4.1. Группы команд

- •4.2. Адресация операндов

- •4.3. Методы адресации

- •5. Память вычислительных машин

- •5.1. Иерархическая организация системы памяти

- •5.2. Иерархическая структура зу

- •5.3. Основные характеристики зу

- •5.4. Организация связи оп с процессором

- •5.5. Ассоциативные зу

- •Контрольные вопросы

- •6. Принципы обмена данными в вычислительных машинах. Интерфейсы вычислительных машин, организация прерываний

- •6.1. Шины

- •6.1.1. Синхронная шина

- •6.1.2. Пересылка данных за несколько тактов

- •6.1.3. Асинхронные шины

- •6.1.4. Заключительные замечания

- •6.2. Назначение и классификация шинных интерфейсов

- •6.3. Организация и обмен данными между периферийными устройствами и вычислительным ядром системы

- •6.4. Организация прерываний

- •6.4.1. Программные прерывания

- •Команда int

- •6.4.2. Обработка прерываний

- •6.4.3 Таблица векторов прерываний

- •6.4.4. Запуск обработчиков прерываний

- •6.5. Последовательная передача данных

- •7. Вычислительные системы параллельной обработки данных

- •7.1. Параллельная обработка как архитектурный способ повышения производительности

- •7.2. Параллелизм и конвейеризация – способы параллельной обработки данных

- •7.2.1. Параллельная обработка данных (параллелизм)

- •7.2.2. Конвейеризация

- •7.3. Классификация архитектур вычислительных систем

- •7.4. Мультипроцессоры и мультикомпьютеры

- •7.5. Классификация мультипроцессорных систем по способу организации основной памяти

- •7.6. Закон Амдала (эффективность параллельных программ)

- •8. Компьютер ibm pc и операционная система ms dos

- •8.1.Архитектурные особенности процессоров семейства ia-32

- •8.2. Организация памяти компьютера ibm pc, работающего под управлением ms dos

- •Видеопамять

- •Пзу bios

- •Системные ресурсы компьютера

- •8.3. Основы программирования на языке Ассемблера

- •8.3.1. Выполнение программ

- •8.3.2. Написание, компиляция и отладка программы

- •8.3.3. Дополнительные средства ассемблера

- •9. Темы заданий для контрольной работы

- •Тема 1. Архитектура процессора Intel 8086.

- •Контрольные вопросы

- •9.1. Аппаратная модель процессора 8086

- •Программная модель процессора

- •Тема 2. Структура ехе- и сом- программы. Вывод на экран.

- •9.2. Структура программы на языке Ассемблера.

- •9.3. Вывод информации на экран

- •Тема 3. Циклы, ввод с клавиатуры.

- •Тема 4. Ввод чисел. Перевод чисел в различные системы счисления.

- •9.4. Перевод чисел в различные системы счисления

- •Тема 5. Работа с прерываниями: перехват и восстановление.

- •Варианты задания

- •Контрольные вопросы

- •Тема 6. Программирование таймера 8254 и генерация звука

- •Программирование звукового канала таймера.

- •9.7. Инициализация таймера

- •9.8. Назначение каналов таймера в ibm pc

- •9 .9. Генерация тона.

- •9.10. Варианты задания

- •Тема 7. Ответы на контрольные вопросы по лекционному курсу

- •Вариантов заданий Таблица 9.4

- •Литература

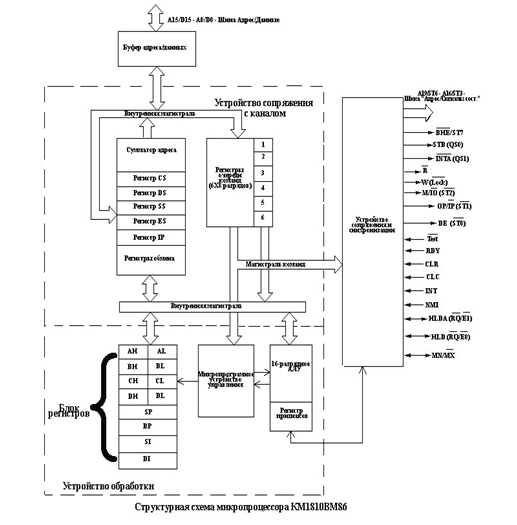

9.1. Аппаратная модель процессора 8086

Выполнение программы в ЭВМ представляет собой циклическую последовательность приведенных ниже действий, образующих цикл команды:

Формирование адреса следующей по порядку команды.

Выборка команды из памяти (чтение команды из памяти и занесение её в регистр команд МП).

3. Декодирование команды (анализ команды с целью выяснения типа подлежащей выполнению операции и операндов).

4. Считывание операнда из памяти, если это требуется по смыслу команды.

5. Собственно выполнение команды (выполнение операции, указанной в команде).

6. Запись результата в память, если это указано в команде, и переход к новому циклу команды.

Обычно в микропроцессоре эти действия выполняются последовательно во времени. В процессоре 8086 основные этапы сохранены, но они распределены внутри процессора по двум сравнительно независимым устройствам. Операционное устройство выполняет команды, а устройство шинного интерфейса выбирает команды, считывает операнды и записывает результаты. Оба устройства могут работать параллельно и в большинстве случаев обеспечивают значительное совмещение выборки и выполнения команд. В результате этого время выборки команды как-бы "исчезает" из цикла команды, так как операционное устройство выполняет команды, уже выбранные шинным интерфейсом из оперативной памяти (для их временного хранения в схеме процессора есть внутренняя регистровая память, называемая очередью (буфером) команд).

Операционное устройство содержит группу общих регистров, арифметико-логическое устройство (АЛУ), основу которого составляет комбинированный 16-разрядный сумматор с последовательно-параллельным переносом, регистр флажков и несколько регистров для временного хранения операндов и результата операции. Оно выполняет команды, обменивается данными и адресами с шинным интерфейсом, оперирует общими регистрами и флажками. В его составе имеется блок микропрограммного управления, который дешифрует команды и формирует необходимые управляющие сигналы. Операционное устройство изолированно от внешней шины, за исключением нескольких внешних сигналов.

Шинный интерфейс выполняет для операционного устройства все операции обмена. Данные передаются между процессором и памятью или портами ввода-вывода по запросам операционного устройства. Когда операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует опережающую выборку из памяти очередных команд. Команды хранятся во внутренней регистровой памяти, называемой очередью (буфером) команд.

Рис.9.1. Аппаратная модель процессора 8086

Очередь команд выполняет по существу функции регистра команды процессора. Длина очереди составляет 6 байт. Очередь команд работает по принципу FIFO ("первым пришел, первым вышел"), который сохраняет на выходе порядок поступления команд. Шинный интерфейс инициирует выборку из памяти следующего командного слова, когда в очереди оказываются два свободных (пустых) байта.

В большинстве случаев очередь команд содержит минимум один байт потока команд, и поэтому операционное устройство не ожидает выборки очередной команды. Конечно, очередь обеспечивает положительный эффект при естественном порядке выполнения команд. Когда операционное устройство выполняет команду передачи управления, шинный интерфейс сбрасывает очередь, выбирает команду по новому адресу, передает ее в операционное устройство, а затем начинает заполнение очереди из следующих ячеек памяти. Эти действия выполняются при словных и безусловных переходах, вызовах подпрограмм, возвратах из подпрограмм и при обработке прерываний. Шинный интерфейс приостанавливает выборку команд, когда операционное устройство запрашивает операцию считывания или записи в память или порт ввода-вывода.

В состав шинного интерфейса входят несколько регистров и сумматор, которые формируют 20-разрядный физический адрес памяти из двух 16-разрядных логических адресов: сегмента (базы) и смещения. При готовности операционного устройства выполнять команду оно считывает из очереди байт, а затем выполняет предписанную командой операцию. При многобайтных командах из очереди считываются и другие байты команды. Когда операционное устройство готово считать командный байт, а очередь команд пуста, оно ожидает выборки командного слова из памяти программ, которую производит шинный интерфейс. Если команда требует обращения к памяти или порту ввода-вывода, операционное устройство запрашивает шинный интерфейс на выполнение необходимого цикла шины. Когда шинный интерфейс не занят выборкой команды, он удовлетворяет запрос немедленно; в противном случае операционное устройство ожидает завершения текущего цикла шины.