- •Введение

- •Цели и задачи курса

- •1. Общие сведения о вычислительных машинах и вычислительных системах

- •1.1. Основные понятия и определения

- •1.2. Классификация эвм по назначению и типу

- •1.3. Типы эвм

- •1.4. Основные принципы организации вычислительных машин и систем

- •1.5. Основные характеристики вычислительных машин и систем

- •1.5.1 Стоимость и цена аппаратного обеспечения

- •1.5.2. Производительность вычислительных машин и систем

- •Контрольные вопросы

- •2. Фукциональный состав и назначение основных устройств вм

- •2.2. Назначение шин, шина с тремя состояниями

- •2.3. Назначение устройств ввода-вывода, способы информационного обмена

- •Контрольные вопросы

- •3. Организация процессоров

- •3.1. Введение в функциональную организацию процессора

- •3.2. Операционный блок

- •3.3. Блок управления

- •3.4. Устройства управления процессора

- •3.4.1. Классификация уу

- •3.4.2. Аппаратные уу

- •3.4.3. Микропрограммные уу

- •3.5. Интерфейсный блок

- •3.6. Назначение стека

- •Контрольные вопросы

- •4. Система команд и адресация данных

- •4.1. Группы команд

- •4.2. Адресация операндов

- •4.3. Методы адресации

- •5. Память вычислительных машин

- •5.1. Иерархическая организация системы памяти

- •5.2. Иерархическая структура зу

- •5.3. Основные характеристики зу

- •5.4. Организация связи оп с процессором

- •5.5. Ассоциативные зу

- •Контрольные вопросы

- •6. Принципы обмена данными в вычислительных машинах. Интерфейсы вычислительных машин, организация прерываний

- •6.1. Шины

- •6.1.1. Синхронная шина

- •6.1.2. Пересылка данных за несколько тактов

- •6.1.3. Асинхронные шины

- •6.1.4. Заключительные замечания

- •6.2. Назначение и классификация шинных интерфейсов

- •6.3. Организация и обмен данными между периферийными устройствами и вычислительным ядром системы

- •6.4. Организация прерываний

- •6.4.1. Программные прерывания

- •Команда int

- •6.4.2. Обработка прерываний

- •6.4.3 Таблица векторов прерываний

- •6.4.4. Запуск обработчиков прерываний

- •6.5. Последовательная передача данных

- •7. Вычислительные системы параллельной обработки данных

- •7.1. Параллельная обработка как архитектурный способ повышения производительности

- •7.2. Параллелизм и конвейеризация – способы параллельной обработки данных

- •7.2.1. Параллельная обработка данных (параллелизм)

- •7.2.2. Конвейеризация

- •7.3. Классификация архитектур вычислительных систем

- •7.4. Мультипроцессоры и мультикомпьютеры

- •7.5. Классификация мультипроцессорных систем по способу организации основной памяти

- •7.6. Закон Амдала (эффективность параллельных программ)

- •8. Компьютер ibm pc и операционная система ms dos

- •8.1.Архитектурные особенности процессоров семейства ia-32

- •8.2. Организация памяти компьютера ibm pc, работающего под управлением ms dos

- •Видеопамять

- •Пзу bios

- •Системные ресурсы компьютера

- •8.3. Основы программирования на языке Ассемблера

- •8.3.1. Выполнение программ

- •8.3.2. Написание, компиляция и отладка программы

- •8.3.3. Дополнительные средства ассемблера

- •9. Темы заданий для контрольной работы

- •Тема 1. Архитектура процессора Intel 8086.

- •Контрольные вопросы

- •9.1. Аппаратная модель процессора 8086

- •Программная модель процессора

- •Тема 2. Структура ехе- и сом- программы. Вывод на экран.

- •9.2. Структура программы на языке Ассемблера.

- •9.3. Вывод информации на экран

- •Тема 3. Циклы, ввод с клавиатуры.

- •Тема 4. Ввод чисел. Перевод чисел в различные системы счисления.

- •9.4. Перевод чисел в различные системы счисления

- •Тема 5. Работа с прерываниями: перехват и восстановление.

- •Варианты задания

- •Контрольные вопросы

- •Тема 6. Программирование таймера 8254 и генерация звука

- •Программирование звукового канала таймера.

- •9.7. Инициализация таймера

- •9.8. Назначение каналов таймера в ibm pc

- •9 .9. Генерация тона.

- •9.10. Варианты задания

- •Тема 7. Ответы на контрольные вопросы по лекционному курсу

- •Вариантов заданий Таблица 9.4

- •Литература

7.6. Закон Амдала (эффективность параллельных программ)

В идеале, решение задач на Р – процессорах должно производиться в Р-раз быстрее, чем на одном и/или ложно позволять решить задачу с данными в Р-раз большими.

На самом деле, такое ускорение практически никогда не достигается. Причина этому хорошо иллюстрируется законом Амдала:

S – Ускорение работы программы на «р» процессорах.

f – Доля непараллельного кода в программе.

Эта формула справедлива и при программировании общей памяти и в моделях передачи сообщений.

Для SMP-систем (модели общей памяти) долю непараллельного кода образуют те операторы, которые выполняют только главную нить программы.

Для MPP- систем (механизм передачи сообщений) непараллельная часть кода образуется только теми операторами, выполнение которых дублируется все5ми процессорами.

Оценить эту величину в процессе анализа кода программы невозможно.

Из формулы следует, что Р-кратное ускорение может быть достигнуто только, когда доля непараллельного кода равна 0. Очевидно, что добиться этого практически невозможно.

В некотором смысле закон Амдала устанавливает предельное число процессоров, на котором программа будет выполняться с приемлемой эффективностью в зависимости от доли непараллельного кода.

8. Компьютер ibm pc и операционная система ms dos

Т.к. для выполнения практических заданий контрольной работы студентам- заочникам необходимо написать несколько программ на языке ассемблера МП86 и ответить на контрольные вопросы по архитектуре процессора 8086 то далее подробно рассматривается соответствующий теоретический материал.

8.1.Архитектурные особенности процессоров семейства ia-32

Операционная система MS-DOS, язык ассемблера МП86 и методы программирования микропроцессоров корпорации Intel разрабатывались применительно к 16-разрядному процессору i8086 и тому режиму, который впоследствии получил название реального. Появление процессора 80386 знаменовало собой начато нового этапа в развитии операционных систем и прикладного программирования - этапа многозадачных графических операционных систем защищенного режима типа Windows и 32-разрядных прикладных программ. При этом все архитектурные средства 88/86-го процессора входят в состав любого современного процессора, который, таким образом, можно условно разделить на две части - МП 86 и дополнительные средства, обеспечивающие защищенный режим, 32-разрядную адресацию и прочее. Из этих дополнительных средств можно выделить те, которые обеспечивают защищенный режим, и в реальном режиме не используются (во всяком случае, явным образом; в действительности, процессор, даже работая в реальном режиме, использует, по крайней мере, некоторые из этих средств). Сюда, например, относятся регистры таблиц дескрипторов, регистры тестирования и отладки, привилегированные команды защищенного режима, система страничного отображения адресов и др. С другой стороны, часть новых свойств современных процессоров можно использовать и в реальном режиме, выполняя программы под управлением MS-DOS.

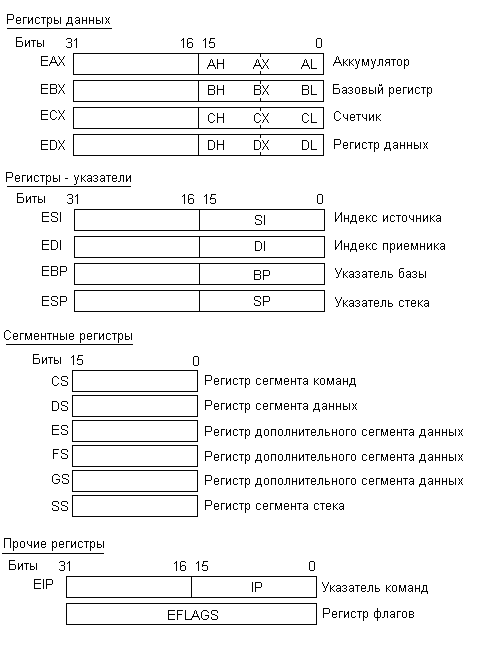

Сюда, прежде всего, относится использование 32-битовых операндов, некоторых новых команд процессора и расширенных возможностей старых команд. 32-разрядные процессоры содержат несколько десятков программно - адресуемых регистров (не считая регистров сопроцессора), из которых шесть являются 16-разрядными, а остальные - 32-разрядными. Регистры принято объединять в семь групп: регистры общего назначения (или регистры данных), регистры-указатели, сегментные регистры, управляющие регистры, регистры системных адресов, отладочные регистры и регистры тестирования. Кроме того, в отдельную группу выделяют счетчик команд и регистр флагов.

Регистры, используемые в реальном режиме, показаны на рис. 8.1. Как видно из рисунка регистры общего назначения и регистры-указатели отличаются от аналогичных регистров МП 86 тем, что они являются 32-разрядными. Соответственно, к их мнемоническим обозначениям добавлена буква Е (от extended, расширенный). Для сохранения совместимости с ранними моделями процессоров допускается обращение к младшим половинам всех регистров, которые имеют те же мнемонические обозначения, что и в МП 86 (АХ, ВХ,СХ, DX, SI, DI, ВР и SP). Естественно, сохранена возможность работы с младшими (AL, BL, CL и DL) и старшими (АН, ВН, СН и DH) половинками регистров МП 86. Однако старшие половины 32-разрядных регистров не имеют мнемонических обозначений и непосредственно недоступны. Для того, чтобы прочитать, например, содержимое старшей половины регистра ЕАХ (биты 31...16) придется сдвинуть все содержимое ЕАХ на 16 бит вправо (в регистр АХ) и прочитать затем содержимое АХ.

Все регистры общего назначения и указатели программист может использовать по своему усмотрению для временного хранения адресов и данных размером от байта до двойного слова. Так, например, возможно использование следующих команд:

mov ЕАХ,0FFFFFFFFh ;Работа с двойным словом (32 бит)

mov AX,0FFFFh ;Работа со словом (16 бит)

mov AL, 0FFh ;Работа с байтом (8 бит)

Все сегментные регистры, как и в МП 86, являются 16-разрядными. В их состав включено еще два регистра - FS и GS, которые могут использоваться для хранения сегментных адресов двух дополнительных сегментов данных.

Рис.8.1. Основные регистры 32-разрядных процессоров.

Таким образом, при использовании расширенных возможностей современных процессоров программе одновременно доступны четыре сегмента данных, а не два, как в МП 86. Регистр указателя команд также является 32-разрядным и обычно при описании процессора его называют EIP. Младшие шестнадцать разрядов этого регистра соответствуют регистру IP процессора МП 86. Весь регистр EIP используется только в 32-разрядных приложениях; в 16-разрядных программах адреса могут быть только 16-разрядными и, соответственно, для адресации в программном сегменте используется младшая половина регистра EIP. Регистр флагов принято называть EFLAGS (от extended flags, расширенные флаги). Хотя он имеет длину 32 бит, только младшие 18 бит (да и то не все) содержат значащую информацию. Дополнительно к шести флагам состояния (CF, PF, AF, ZF, SF и OF) и трем флагам управления состоянием процессора (TF, IF и DF) он включает новые флаги задачи, рестарта и виртуального режима, а также двухбайтовое поле привилегий ввода-вывода. Все эти биты используются только в защищенном режиме, и здесь рассматриваться не будут.