- •Введение

- •Цели и задачи курса

- •1. Общие сведения о вычислительных машинах и вычислительных системах

- •1.1. Основные понятия и определения

- •1.2. Классификация эвм по назначению и типу

- •1.3. Типы эвм

- •1.4. Основные принципы организации вычислительных машин и систем

- •1.5. Основные характеристики вычислительных машин и систем

- •1.5.1 Стоимость и цена аппаратного обеспечения

- •1.5.2. Производительность вычислительных машин и систем

- •Контрольные вопросы

- •2. Фукциональный состав и назначение основных устройств вм

- •2.2. Назначение шин, шина с тремя состояниями

- •2.3. Назначение устройств ввода-вывода, способы информационного обмена

- •Контрольные вопросы

- •3. Организация процессоров

- •3.1. Введение в функциональную организацию процессора

- •3.2. Операционный блок

- •3.3. Блок управления

- •3.4. Устройства управления процессора

- •3.4.1. Классификация уу

- •3.4.2. Аппаратные уу

- •3.4.3. Микропрограммные уу

- •3.5. Интерфейсный блок

- •3.6. Назначение стека

- •Контрольные вопросы

- •4. Система команд и адресация данных

- •4.1. Группы команд

- •4.2. Адресация операндов

- •4.3. Методы адресации

- •5. Память вычислительных машин

- •5.1. Иерархическая организация системы памяти

- •5.2. Иерархическая структура зу

- •5.3. Основные характеристики зу

- •5.4. Организация связи оп с процессором

- •5.5. Ассоциативные зу

- •Контрольные вопросы

- •6. Принципы обмена данными в вычислительных машинах. Интерфейсы вычислительных машин, организация прерываний

- •6.1. Шины

- •6.1.1. Синхронная шина

- •6.1.2. Пересылка данных за несколько тактов

- •6.1.3. Асинхронные шины

- •6.1.4. Заключительные замечания

- •6.2. Назначение и классификация шинных интерфейсов

- •6.3. Организация и обмен данными между периферийными устройствами и вычислительным ядром системы

- •6.4. Организация прерываний

- •6.4.1. Программные прерывания

- •Команда int

- •6.4.2. Обработка прерываний

- •6.4.3 Таблица векторов прерываний

- •6.4.4. Запуск обработчиков прерываний

- •6.5. Последовательная передача данных

- •7. Вычислительные системы параллельной обработки данных

- •7.1. Параллельная обработка как архитектурный способ повышения производительности

- •7.2. Параллелизм и конвейеризация – способы параллельной обработки данных

- •7.2.1. Параллельная обработка данных (параллелизм)

- •7.2.2. Конвейеризация

- •7.3. Классификация архитектур вычислительных систем

- •7.4. Мультипроцессоры и мультикомпьютеры

- •7.5. Классификация мультипроцессорных систем по способу организации основной памяти

- •7.6. Закон Амдала (эффективность параллельных программ)

- •8. Компьютер ibm pc и операционная система ms dos

- •8.1.Архитектурные особенности процессоров семейства ia-32

- •8.2. Организация памяти компьютера ibm pc, работающего под управлением ms dos

- •Видеопамять

- •Пзу bios

- •Системные ресурсы компьютера

- •8.3. Основы программирования на языке Ассемблера

- •8.3.1. Выполнение программ

- •8.3.2. Написание, компиляция и отладка программы

- •8.3.3. Дополнительные средства ассемблера

- •9. Темы заданий для контрольной работы

- •Тема 1. Архитектура процессора Intel 8086.

- •Контрольные вопросы

- •9.1. Аппаратная модель процессора 8086

- •Программная модель процессора

- •Тема 2. Структура ехе- и сом- программы. Вывод на экран.

- •9.2. Структура программы на языке Ассемблера.

- •9.3. Вывод информации на экран

- •Тема 3. Циклы, ввод с клавиатуры.

- •Тема 4. Ввод чисел. Перевод чисел в различные системы счисления.

- •9.4. Перевод чисел в различные системы счисления

- •Тема 5. Работа с прерываниями: перехват и восстановление.

- •Варианты задания

- •Контрольные вопросы

- •Тема 6. Программирование таймера 8254 и генерация звука

- •Программирование звукового канала таймера.

- •9.7. Инициализация таймера

- •9.8. Назначение каналов таймера в ibm pc

- •9 .9. Генерация тона.

- •9.10. Варианты задания

- •Тема 7. Ответы на контрольные вопросы по лекционному курсу

- •Вариантов заданий Таблица 9.4

- •Литература

3.6. Назначение стека

Стек - это память с линейно упорядоченными ячейками и специальным механизмом доступа, исключающим необходимость указания адреса при записи и чтении. В зависимости от используемого правила доступа, называемого дисциплиной, различают два типа организации стековой памяти: очередь и стек. Дисциплина определяется применительно к входным (записываемым) и выходным (читаемым) последовательностям слов. Очередь реализует дисциплину FIFO (First-In-First-Out - первый поступивший удаляется первым). Стек в отличие от очереди организован в соответствии с дисциплиной LIFO (Last-In-First-Out - последний поступивший извлекается первым), т.е. информация из стека выбирается в обратном по отношению к записи порядке. В МП обычно используют стек. Физически стек представляет собой набор регистров (аппаратурный стек) или ячеек оперативной памяти, снабженный указателем стека SP.

Указатель SP, в качестве которого используют реверсивный счетчик, всегда адресует «вершину стека», под которой понимается ячейка стека, доступная для чтения. По мере записи и считывания данных из стека содержимое указателя SP меняется: при записи или загрузке в стек, например при исполнении команд PUSH, значение указателя SP уменьшается - стек растет в сторону младших адресов, а при чтении или выталкивании данных из стека, в частности при исполнении команд POP, значение указателя SP увеличивается. Указанное правило при обращении к стеку реализуется автоматически, и поэтому при операциях со стеком возможно безадресное задание операнда. Стековая память является безадресной.

Важнейшей характеристикой стека является его размер. МП может содержать относительно небольшой по размеру аппаратный стек (число внутренних регистров стековой памяти, как правило, не превышает 8 - 16) или не содержать такового совсем. Более распространена архитектура МП, использующая практически неограниченный внешний стек, моделируемый в ОП с произвольным доступом.

Стек играет важную роль в микропроцессорных системах как средство сохранения адресов возврата и состояния данных при работе с подпрограммами. Использование стека приводит к существенным упрощениям при организации вложенных подпрограмм, когда одна программа вызывает другую, которая в свою очередь может вызвать третью и т.д. В таких случаях при каждом вызове адрес возврата текущей программы и другая необходимая информация (содержимое РОН) загружаются в стек. При возврате информация в обратном порядке выбирается из стека. Заметим, что при организации стека, моделируемого в памяти с произвольным доступом, время обращения к элементам данных стека равно времени обращения к памяти. Однако стек наряду с отмеченными особенностями его использования эффективнее обычной памяти. Во-первых, используемые при обращении к стеку, команды PUSH и POP короче стандартных команд обращения к памяти, так как в них один из операндов неявно адресуется через регистр SP, и, во-вторых, инкремент или декремент указателя SP с образованием нового адреса производится автоматически.

В современных процессорах стек применяется для разных целей: временного хранения данных, когда для них нет смысла выделять фиксированные места в памяти; организации прерываний, вызовов процедур и возвратов из них; передачи и возврата параметров при вызовах процедур. Кроме того, стековая память является важнейшей компонентой процессоров со стековой архитектурой.

Структуру стекового процессора имеет специализированный арифметический сопроцессор (блок вычислений с плавающей точкой FPU) современных МП Pentium. Чтобы пояснить его назначение, кратко характеризуем предысторию его появления.

В связи с ограничениями на сложность схем ОБ младшие модели МП могли выполнять только операции над числами с фиксированной точкой с ограниченной длиной слова. Обработка чисел повышенной разрядности и чисел в формате с плавающей точкой в таких МП реализовывались программно. Это приводило к значительному снижению производительности.

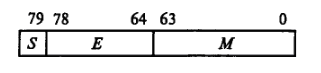

Рис. 3.4. Расширенный формат вещественных чисел:

S – знак числа; E – порядок числа; M – мантисса числа

Для эффективной реализации операций над числами в стандартных форматах в конце 70-х гг. XX в. был предложен принцип специализации. Суть его заключается в разработке специализированных процессорных модулей (сопроцессоров) со своими системами команд, которые ориентированы на конкретные приложения. Арифметический сопроцессор с плавающей точкой является примером такого модуля. Сопроцессоры обычно работают под управлением центрального процессора и совместно используют ОП. Сопроцессор не имеет своей отдельной программы и не может считывать команды из памяти, однако он может обращаться к памяти для записи и считывания данных. Часть кодов команд центрального процессора резервируется для команд сопроцессора. Сопроцессор не может выполнять команды центрального процессора, но свои команды выполняет очень быстро (по сравнению с их программной эмуляцией командами центрального процессора). В процессе работы и процессор, и сопроцессор из общего командного потока выбирают свои команды и выполняют их. Сопроцессор выполняет свои «долгие» арифметические операции параллельно с центральным процессором, при этом последний может продолжать выполнение потока собственных команд.

Такое архитектурное решение фирма Intel применила в семействе программно совместных МП 8086, 80286, 80386, 80486 (i486). Обобщенно архитектуру процессов этого семейства обозначают х86. Для младших членов семейства сопроцессоры были реализованы в виде специализированных СБИС - 8087 (для 8086), 80287 (для 80286), 80387 (для 80386). Благодаря росту уровня интеграции микросхем в МП i486 и всех моделях Pentium арифметический сопроцессор реализован в виде устройства операций с плавающей точкой FPU как составная часть процессора, т.е. является внутренним блоком МП. Размещение устройства FPU на кристалле процессора значительно повышает производительность численных вычислений. Совместно с центральным процессором сопроцессор образует мощный тандем, производительность которого в задачах численной обработки в 10-50 раз выше производительности одного центрального процессора. С точки зрения программиста, система с сопроцессором выглядит как единый процессор с расширенными возможностями ОБ, большим набором команд, форматов чисел и числом регистров. Взаимодействие между центральным процессором и FPU невидимо для пользователя.