- •Особливості Pentium полягають у використанні суперскалярної технології, що дозволяє одночасно виконувати дві операції. Класи мікропроцесорів

- •Застосування мп

- •Структура мікропроцесорів

- •Характеристики мікропроцесорів

- •Основні поняття мікропроцесорних систем

- •Мікропрограмний принцип керування операціями

- •Способи відображення мікропрограм

- •Способи керування операціями

- •1.4. Архітектура мікропроцесорів

- •1.5. Основи програмування мовою асемблер

- •2.1. Однокристальні 16-розрядні мікропроцесори

- •2.3. Архітектура 32-розрядних мікропроцесорів

1.4. Архітектура мікропроцесорів

Поняття архітектури мікропроцесора визначає його складові частини, зв’язки та взаємодію між ними. Архітектура містить: 1) структурну схему МП; 2) програмну модель МП (описання функцій регістрів); 3) інформацію про організацію пам'яті (ємність пам’яті та способи її адресації); 4) опис організації процедур введення-виведення.

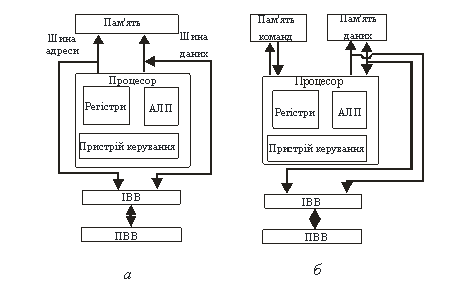

Фоннейманівську архітектуру (рис. 1.7,а) запропонував у 1945 р. американський математик Джон фон Нейман. Особливістю цієї архітектури є те, що програма і дані знаходяться у спільній пам’яті, доступ до якої здійснюється по одній шині даних і команд.

Рис. 1.7 Основні типи архітектури: а – фоннейманівська; б – гарвардська

Гарвардську архітектуру (рис.1.7,б) вперше було реалізовано у 1944 році в релейній обчислювальній машині Гарвардського університету (США). Особливістю цієї архітектури є те, що пам’ять даних і пам’ять програм розділені і мають окремі шину даних і шину команд, що дозволяє підвищити швидкодію МПС.

Структурні схеми МП обох архітектур містять: процесор, пам’ять, ІВВ і ПВВ. Пам’ять і ІВВ для різних типів МП можуть бути як внутрішніми (тобто розміщуватися на тому ж кристалі, що і процесор, так і зовнішніми. Процесор містить регістри, арифметично-логічний пристрій (АЛП) та пристрій керування і виконує функції обробки даних та керування процесами обміну інформацією. Пам’ять забезпечує зберігання кодів команд програми і даних. Інтерфейси призначені для зв’язку з ПВВ. Усі елементи структурної схеми з’єднані за допомогою шин.

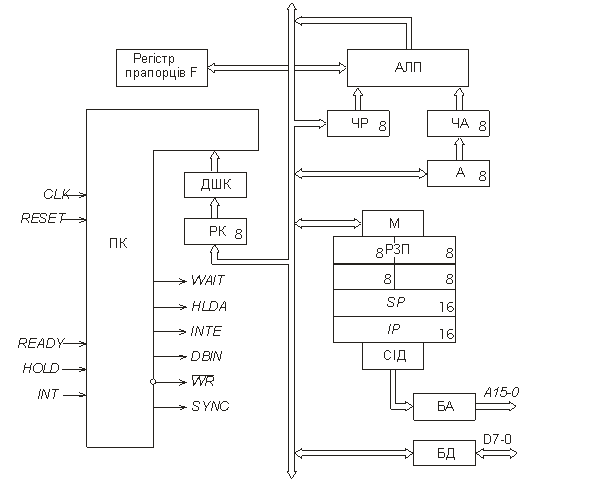

Розглянемо більш докладно МП з фоннейманівською архітектурою на прикладі узагальненого 8-розрядного однокристального МП, структурну схему якого показано на рис. 1.8. Схема має єдину внутрішню 8-розрядну шину, по якій передаються дані, коди команд та адреси.

Структурна схема містить: пристрій керування ПК, дешифратор команд (ДШК), регістр команд (РК), арифметично-логічний пристрій (АЛП), акумулятор (А), часовий акумулятор (ЧА), часовий регістр (ЧР), регістр прапорців F, блок 8-розрядних регістрів загального призначення (РЗП), мультиплексор, вказівник стека (Stack-Pointer SP), вказівник команд (Instruction-Pointer IP), буферний регістр адреси (БА), буферний регістр даних (БД), схему інкременту/декременту (СІД).

Пристрій керування відповідно до дешифрованих кодів команд та зовнішніх сигналів генерує керуючі сигнали для всіх блоків структурної схеми.

Дешифратор команд формує сигнали для пристрою керування згідно з дешифрованим кодом команди. У 8-розрядному регістрі команд зберігається машинний код команди (один байт).

.

Рис. 1.8 Структурна схема 8-розрядного мікропроцесора

Арифметично-логічний пристрій – це комбінаційна схема на основі суматора і логічних елементів, яка сигналами з виходів пристрою керування налагоджується на ту чи іншу арифметичну або логічну операцію, наприклад, додавання, віднімання, І, АБО, ВИКЛЮЧАЛЬНЕ АБО, НІ, зсув.

Акумулятор є 8-розрядним регістром, в якому зберігається один з операндів у двооперандних командах, а також результат операції. Наприклад, у команді додавання

ADD B; A+BA

вказано лише один операнд – 8-розрядний регістр B, який є одним з регістрів загального призначення. Другим операндом є акумулятор. Результат додавання вмісту акумулятора та регістра B переноситься в акумулятор, що символічно записується в коментарі до команди.

Часовий акумулятор та часовий регістр являють собою 8-розрядні буферні регістри, які дозволять відокремити входи АЛП від його виходу, тобто виключити „гонку” сигналів.

Регістр прапорців F (Flags – прапорці), або регістр ознак являє собою декілька тригерів (п’ять або шість), які встановлюються в одиничний (або скидаються в нульовий) стан залежно від результату операції в АЛП.

Регістри загального призначення – блок 8-розрядних регістрів, в яких зберігаються дані та проміжні результати. У деяких МП РЗП позначаються літерами латинського алфавіту: B, C, D, H, L, в інших – R0, R1, R2,… .

Блок РЗП можна розглядати як швидкодіючий ОЗП, що має найбільшу швидкодію серед ОЗП різноманітних типів, оскільки він розміщений безпосередньо на кристалі ВІС МП. Деякі типи 8-розрядних процесорів, крім 8-розрядних РЗП, містять 16-розрядні індексні регістри для організації непрямої адресації, інші припускають звернення до пари 8-розрядних регістрів як до одного 16-розрядного.

Мультиплексор – пристрій, що з’єднує один з регістрів РЗП із внутрішньою шиною МП.

Вказівник стека SP – 16-розрядний регістр, у якому зберігається адреса останньої зайнятої комірки стека.

Вказівник команд IP – 16-розрядний регістр, у якому зберігається адреса команди, що виконується. Після вибірки кожного байта команди з пам’яті програм вміст IP збільшується на одиницю. У літературі цей регістр інколи називаютьРС (Program Counter - програмний лічильник).

Буферний регістр адреси та буферний регістр даних – регістри з трьома станами виходу, призначені для формування сигналів на лініях шин адреси і даних відповідно.

Схема інкременту/декременту – пристрій, що дає змогу без участі АЛП збільшити або зменшити на одиницю вміст одного з регістрів РЗП, IP або SP.

Конструктивно ВІС 8-розрядного процесора виконано в корпусі з 40 виводами, з яких 16 припадає на шину адреси, 8 – на шину даних, 2 (4) – на ввімкнення живлення, а інші – на лінії шини керування. Основні лінії шини керування показано на рис. 1.8:

Вхідні сигнали керування

Ф1, Ф2 (F1,F2) - це дві послідовності тактових імпульсів, що неперехрещюються між собою, з однаковою частотою та різною тривалістю.

RESET - це сигнал обнулення, що обнуляє склад лічильника програм, та сигнали типу HCDA, INTE.

READY - сигнал, що вказує МП на готовність пам’яті, або зовнішніх пристроїв до вводу або виводу даних.

HOLD - сигнал захвату; виробляється зовнішніми пристроями для захвату доступу до шини адрес. Цей сигнал використовується для прямого доступу к пам’яті.

INT - сигнал запиту на переривання. Цей сигнал сприймається мікропроцесором в сиані зупинення або в кінці останнього машинного циклу.

Вихідні сигнали

SYNC - сигнал синхронізації; вказує на початок кожного машинного циклу; під час його дії на шині даних з’являється інформація про стан МП

DBIN - сигнал приймання інформації; він вказує на те, що шини МП знаходяться в режимі приймання і МП чекає інформацію на шину даних.

![]() - сигнал

видавання інформації; він вказує на те,

що МП видає інформацію на шину даних

(для її запису в пам’ять або для передачі

зовнішнім пристроям)

- сигнал

видавання інформації; він вказує на те,

що МП видає інформацію на шину даних

(для її запису в пам’ять або для передачі

зовнішнім пристроям)

WAIT - сигнал очикування; він підтверджує, що МП знаходиться в стані очикування.

HLDA - сигнал підтвердження захвату; він генерується МП у відповідь на сигнал HOLD, при цьому МП підтверджує, що його шини знаходяться в третьому стані і зовнішні пристрої могут звертатися до пам’яті на пряму, обходячи МП. Використовується для прямого доступу до пам’яті.

INTE - сигнал дозволу переривання; підтверджує, що тригер дозволу переривання МП знаходиться в стані “1”.

Програмною моделлю МП називається сукупність програмно-доступних регістрів, тобто тих регістрів, вміст яких можна зчитати або змінити за допомогою команд. Програмну модель МП складають акумулятор, РЗП, регістр прапорців, вказівник стека та вказівник команд.

Організація пам’яті. Максимально можлива ємність пам’яті мікропроцесорної системи визначається кількістю розрядів шини адреси. Більшість 8-розрядних процесорів (i8080, i8085, Z80, Motorola 6800) мають 16-розрядну шину адреси, тобто дозволяють адресувати 216 = 64 Кбайт пам’яті.

Організація введення-виведення. 8-розрядні МП мають можливість передати або прийняти дані із зовнішніх ПВВ, які з’єднуються із системною шиною МП системи за допомогою портів введення-виведення, які являють собою 8-розрядні регістри із схемами вибірки та керуванням читанням/записом. Кількість таких пристроїв визначається можливим діапазоном 8-розрядних адрес портів, тобто 28 = 256 портів введення і 256 портів виведення. Як порти введення можуть бути використані буферні регістри, наприклад: КР580ИР82, КР589ИР12 або інтерфейс введення-виведення паралельної інформації КР580ВВ55.

Введення або виведення даних може здійснюватися двома способами: 1) з використанням окремого адресного простору ПВВ; 2) з використанням спільного з пам’яттю адресного простору, тобто з відображенням на пам’ять.

Перший спосіб дозволяє виконувати введення і виведення даних за командами введення IN та виведення OUT. Використання другого способу передбачає розташування адрес портів у спільному з пам’яттю адресному просторі. При цьому операції звернення до портів не відрізняються від операцій звернення до пам’яті.

Таблиця значень розрядів слова стану МП для різних МЦ

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

1.Вибір команди (М1) |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

2.Зчитування з памяти (MR) |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

3.Запис у память (MW) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

4.Зчитування стеку (SR) |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

5.Запис у стек (SW) |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

6.Ввод інформації (IN) |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

7.Вивід інформації (OUT) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

8.Підтвердж.дозволу на перерів. |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

9.Підтвердження зупінки |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

10. Підтвердж.перерів. при зупинці |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |