- •1. Классификация микропроцессоров

- •По сложности архитектуры и набору команд можно разделить мп с cisc- и risc-архитектурой.

- •6. Структура микропроцессора. Схема управления прямым доступом.

- •8. Режимы работы микропроцессорной системы.

- •9. Архитектура микропроцессорных систем. Гарвардская архитектура (принципы построения, место применения).

- •10. Организация обмена информацией в микропроцессорной системе. Принстонская архитектура (принципы построения, место применения).

- •11. Указать особенности универсальных и специализированных микропроцессоров.

- •12. Организация шинного обмена данными.

- •13. Структура памяти. Стек. Микропроцессорной системы.

- •14. Команды микропроцессора.

- •22. Циклы обмена данными по магистралям микропроцессорной системы. Стробы в управлении микропроцессорной системой

- •23. Циклы обмена данными по магистралям микропроцессорной системы. Обмена по прерываниям.

- •25. Перечислить факторы, влияющие на прохождение сигналов по магистрали.

- •27. Адресация микропроцессорной системе.

- •Запоминающие устройства можно разделить по следующим важнейшим классификационным признакам.

- •16. Аналогово-цифровой преобразователь. Привести структурную схему.

- •17. Цифро-аналоговый преобразователь. Привести структурную схему.

- •18. Внешние устройства ввода-вывода. Интерфейс rs-232.

- •20. Визуальные языки программирования.

- •21. Шифратор/дешифратор адреса.

- •26. Поясните установку терминаторов на магистраль.

- •31. Параллельные порты и дискретный ввод-вывод.

- •32. Последовательные интерфейсы и сетевые средства передачи данных.

- •33. Применение широтно-импульсной модуляции в микропроцессорах.

- •Структура памяти микропроцессорных систем;

Запоминающие устройства можно разделить по следующим важнейшим классификационным признакам.

По физическим принципам работы ЗУ делятся на магнитные, электронные, оптические, механические, криогенные.

По способу организации доступа к памяти различают ЗУ с произвольным доступом (адресные) и ЗУ с последовательным доступом (безадресные).

По способности сохранять информацию при отключенном питание. Делятся на ЗУ, не способные сохранять информацию при отключении питания, и энергонезависимые ЗУ; По способу хранения информации различают статические и динамические ЗУ. В статических ЗУ физическое состояние носителя информации в процессе хранения не изменяется. В динамических ЗУ состояние носителя постоянно изменяется.

По функциональному назначению различают сверхоперативные ЗУ (СОЗУ), оперативные ЗУ (ОЗУ), постоянные ЗУ (ПЗУ), перепрограммируемые постоянные ЗУ (ППЗУ), стековые ЗУ. Программируемые логические матрицы (ПЛИС, PLD – programmable logic device) – это особый вид интегральных микросхем, предназначеных для преобразования комбинаций входного кода в определенную комбинацию выходного кода в соответствии с заданными булевыми функциями.Программируемые логические матрицы применяются в качестве конечных автоматов, устройств управления с аппаратной реализацией,логических преобразователей адресов, управляющей памяти и др.

16. Аналогово-цифровой преобразователь. Привести структурную схему.

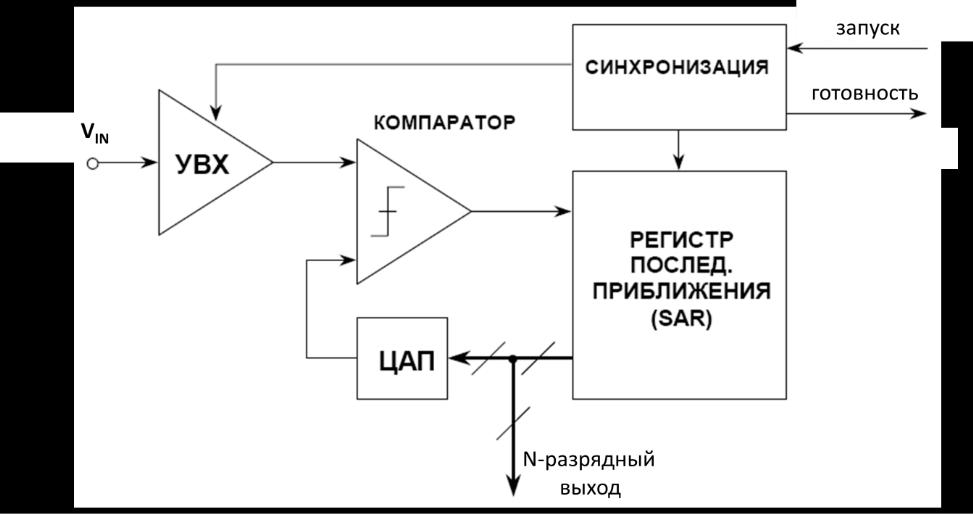

АЦП последовательных поразрядных приближений. На рис. 6.4 приведена функциональная схема такого АЦП.

В преобразовании предусматривается

N-разрядный регистр, в котором

последовательно, разряд за разрядом,

начиная со старшего разряда, формируется

двоичное число, соответствующее цифровой

форме представления поданного на вход

микросхемы аналогового напряжения VIN.

Процесс

формирования этого числа состоит в

следующем. В начале преобразования

регистр сдвига SAR сбрасывается в нуль.

Затем запускается цикл аналого-цифрового

преобразования с записи единицы в

выходной триггер старшего разряда

регистра. Получающееся в регистре число

с помощью ЦАП преобразуется в аналоговое

напряжение, которое на аналоговом

компараторе сравнивается с входным

напряжением VIN, мгновенное значение

которого запоминается на устройстве

выборки-хранения УВХ на всем протяжении

цикла преобразования АЦП.

Более высоким

быстродействием (меньшим временем

преобразования) обладают АЦП

параллельного действия,

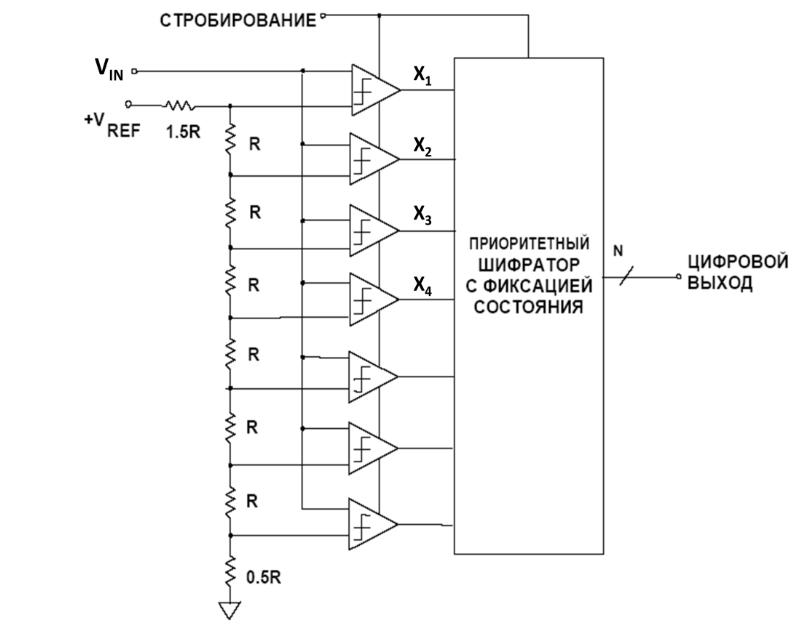

так называемые Flash-ADC. Такие АЦП включают

источник опорного напряжения, резистивный

делитель, компараторы напряжения,

преобразователь кодов, выходной буферный

регистр и генератор тактовых импульсов

[6]. Для преобразования аналогового

сигнала в N-разрядный код требуется 2N–1

компараторов и 2N резисторов, размещенных,

как это показано на рис. 6.5.

преобразовании предусматривается

N-разрядный регистр, в котором

последовательно, разряд за разрядом,

начиная со старшего разряда, формируется

двоичное число, соответствующее цифровой

форме представления поданного на вход

микросхемы аналогового напряжения VIN.

Процесс

формирования этого числа состоит в

следующем. В начале преобразования

регистр сдвига SAR сбрасывается в нуль.

Затем запускается цикл аналого-цифрового

преобразования с записи единицы в

выходной триггер старшего разряда

регистра. Получающееся в регистре число

с помощью ЦАП преобразуется в аналоговое

напряжение, которое на аналоговом

компараторе сравнивается с входным

напряжением VIN, мгновенное значение

которого запоминается на устройстве

выборки-хранения УВХ на всем протяжении

цикла преобразования АЦП.

Более высоким

быстродействием (меньшим временем

преобразования) обладают АЦП

параллельного действия,

так называемые Flash-ADC. Такие АЦП включают

источник опорного напряжения, резистивный

делитель, компараторы напряжения,

преобразователь кодов, выходной буферный

регистр и генератор тактовых импульсов

[6]. Для преобразования аналогового

сигнала в N-разрядный код требуется 2N–1

компараторов и 2N резисторов, размещенных,

как это показано на рис. 6.5.

На каждый компаратор

подается опорное напряжение, значение

которого для соседних точек отличается

на величину, соответствующую одному

младшему значащему разряду (LSB) (более

старшие разряды — в верхних по схеме

элементах). На один вход каждого

компаратора подается напряжение с

соответствующей точки делителя, а на

второй вход всех компараторов одновременно

поступает аналоговый сигнал VIN. Таким

образом, на входе каждого компаратора

постоянно присутствует заданный

уровень

напряжения, с которым осуществляется

сравнение аналогового сигнала.

Максимальное

значение величины аналогового сигнала

VIN определяется соотношением:

(VIN)max=(1–½N)VREF, где VREF – опорное напряжение.

уровень

напряжения, с которым осуществляется

сравнение аналогового сигнала.

Максимальное

значение величины аналогового сигнала

VIN определяется соотношением:

(VIN)max=(1–½N)VREF, где VREF – опорное напряжение.