- •Введение

- •1 Постановка задачи

- •2 Анализ предметной области

- •3 Разработка арифметико-логического устройства

- •4 Разработка гипотетического микропроцессора

- •5 Разработка структуры микро-эвм на базе гипотетического микропроцессора

- •6 Разработка программы эмуляции работы микро-эвм на базе гипотетического микропроцессора

5 Разработка структуры микро-эвм на базе гипотетического микропроцессора

5.1 Разработка ЗУ

Запоминающее устройство микро ЭВМ разделим на две группы: постоянное запоминающее устройство (ПЗУ) и оперативное запоминающее устройство (ОЗУ). В реальных системах микропроцессорных устройств и персональных компьютеров в ПЗУ хранятся программы обеспечивающие работу ЭВМ, которые условно можно разделить на следующие группы:

- тестирование исправности устройств входящих в состав микро ЭВМ при включении ЭВМ ;

- загрузка операционной системы;

- взаимодействие операционной системы и устройств, входящих в состав ЭВМ, посредством BIOS;

Изучение выше перечисленных задач не входит в задание курсового проекта. Поэтому при разработке ПЗУ, ограничились следующими условиями: ПЗУ разрабатываемой микро ЭВМ обеспечивает загрузку сегментных регистров; для демонстрации работы процессора прототипа обращение к ячейкам ПЗУ, обращение к ячейкам ПЗУ производится начиная с адреса FF000h.

При разработке структуры ОЗУ принимаем следующие условия: используем в качестве ОЗУ микросхемы динамической памяти, объем и разрядность ОЗУ выбираем из условий моделирования работы ЭВМ использующих микропроцессор 80286.

5.1.1 Разработка ПЗУ

В связи с небольшим объемом хранящимся в ПЗУ для микро ЭВМ выберем матричное ПЗУ со словарной внутренней организацией 32 Х 32 X 8. Для обращения к конкретным ячейкам памяти в схеме ПЗУ предусматриваем дешифратор строк, по линиям адресной шины А0А5, дешифратор столбцов по линиям адресной шины А6А9, буфер шины данных. схему управления. Функциональная схема ПЗУ представлена на рисунке 5.1.

Рисунок 5.1 Функциональная схема ПЗУ

Схема ПЗУ из матрицы элементов запоминающих устройств обращение к которым происходит по выборке 6-разрядной линии строк и 4-разрядной линии столбцов, которые позволяют обращаться одновременно к 8 ячейкам памяти. Таким образом, емкость ПЗУ составляет 1024 байта. Данные, хранящиеся в ПЗУ, выдаются на шину данных по разрешающему сигналу чтения данных RD. Схему управления ПЗУ и буфер шины данных формируем, используя микросхему КР580ВА86. Поскольку ПЗУ используется только для чтения данных сигнал направления передачи постоянно включен в состояние от А к В, на ввод Т микросхемы подается 1.

5.1.2 Разработка ОЗУ

Для демонстрации работы схемы формирования физического адреса микропроцессора прототипа, принимаем емкость ОЗУ равную 1048576 байт. Для обращения к ОЗУ такого объема потребуется 20-разрядная шина адреса. При этом область памяти размером 64 килобайта расположенная в самых верхних адресах не используется, поскольку это адресное пространство выделено для ПЗУ.

В качестве микросхем памяти для ОЗУ, принимаем микросхемы с динамической памятью. Достоинством микросхем данного типа является высокое быстродействие, при относительно малой цене. Основным недостатком необходимость периодической регенерации зарядов ячеек памяти. Регенерация производится одновременно на всех ячейках одного столбца, после чего выбирается следующий столбец. Выборка столбцов производится через промежутки времени, задаваемые внутренним таймером. Во время регенерации цепи передачи данных и адреса блокируются. Для обеспечения работы ОЗУ и процессора в схеме управления ОЗУ предусмотрена возможность синхронизации работы схемы регенерации и микропроцессора. Схема управления ОЗУ обеспечивает включение режима регенерации в те моменты, когда процессор не обращается к памяти ЭВМ.

Рисунок 5.2 Функциональная схема ОЗУ

Взаимодействие схемы регенерации ОЗУ с процессором выходит за рамки задания курсового проекта, поэтому в структуре ЭВМ управление регенерацией ОЗУ не показано. В результате как и в схеме ПЗУ в качестве схемы управления и двунаправленного буферного регистра применим микросхему КР580ВА86.

5.2 Разработка шин

Информационные линии, обеспечивающие взаимодействие микропроцессора с другими устройствами ЭВМ разделим на три группы:

- шина данных;

- шина адреса;

- сигналы управления объединенные в шину управления.

Шина адреса состоит, по аналогии с ЭВМ построенных на микропроцессоре прототипе 80286, из 20 информационных линий. Для обеспечения высокой нагрузочной способности процессора адресной шине между процессором и устройством памяти включим буферную микросхему КР580ИР82. Каждая микросхема КР580ИР82 обеспечивает обслуживание 8 информационных линий, поэтому

Шина дынных реального процессора 80286 имеет 16 информационных линий, что обеспечивает работу с данными размером в два байта. Согласно задания на курсовой проект все операции производятся с данными размером 1 байт, поэтому в разрабатываемой ЭВМ на базе гипотетического процессора применим шину данных имеющую 8 информационных линий. Для обеспечения высокой нагрузочной способности между шиной данных микропроцессора и шиной данных ЭВМ включим микросхему КР580ВА86.

Поскольку разрабатываемая микро ЭВМ не имеет внешних устройств, количество линий шины управления ограничим следующими линиями:

- разрешение чтения данных RD;

- разрешение записи данных WR:

- захват шины HLDA;

- готовность шины READY;

- прерывание выполнения программы BUSY;

- запрос на прерывание INTR;

Сигналы RD, WR, HLDA и WR обеспечивают взаимодействие микропроцессора с ОЗУ И ПЗУ, а сигналы BUSY и INTR пошаговый режим работы микро ЭВМ.

5.3 Описание БИС окружения

Согласно задания, разрабатываемая ЭВМ должна включать в себя следующие БИС:

- тактовый генератор К1810ГФ84;

- буферные регистры КР580ИР82;

- шинные формирователи КР580ВА86.

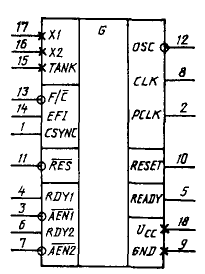

5.3.1 Тактовый генератор К1810ГФ84

Микросхема КР1810ГФ84 представляет собой тактовый генератор и задающее устройство для микропроцессора. Ее назначение – формирование тактовых сигналов для микропроцессора и периферийных устройств, а также сигналов начальной установки RESET и готовность READY.

Рисунок 5.3 Условное графическое обозначение и типовая схема включения КР1810ГФ84

Рассмотрим назначение выходов микросхемы. Два из них RESET и READY описаны выше. К входам Х1 и Х2 подключается кварцевый резонатор, обеспечивающий стабильность частоты тактового генератора. В случае отсутствия резонатора необходимой частоты, возможна работа резонатора на его гармониках. В этом случае к выводу TANK подключается LC контур. Остальные входы используются при различных построениях архитектуры ЭВМ. Выход CLK основной выход тактового генератора. Выход OCS инвертированный по отношению к выходу CLK служит источником формирования сигналов для управления динамическими ОЗУ.

Установка ЭВМ в начальное состояние производится кнопкой сброс, а при включении питания схемой RC-цепи. Пример одной схем включения микросхемы КР1810ГФ84 показан на рисунке 5.3.

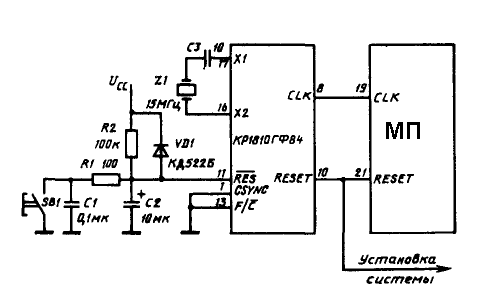

5.3.2 Буферный регистр КР580ИР82

Микросхема КР589ИР82 – 8-разрядный адресный регистр, предназначенный для связи микропроцессора с системной шиной, обладающей повышенной нагрузочной способностью. Каждая микросхема состоит из восьми одинаковых функциональных блоков содержащих D-триггер "защелку", обеспечивающую три состояния на выходе ( 0,1, "отключено") и мощный выходной вентиль без инверсии.

Рисунок 5.4 Условное графическое обозначение и функциональная схема КР580ИР82

Назначение выводов микросхемы следующее:

- D0 – D7 входные информационные сигналы;

- Q0 – Q7 выходные информационные сигналы;

- STB стробирующий сигнал;

- OE сигнал разрешения передачи данных.

В зависимости от состояния сигнала STB микросхема работает в двух режимах: режиме шинного формирователя и режиме хранения. При высоком уровне сигнала STB и низком ОЕ информация, поступающая на входы D0 – D7 повторяется на выходах Q0 – Q7. При переходе сигнала на низкий уровень происходит сохранение поступившей информации. До тех пор пока на входе STB низкий уровень изменение сигналов на входах D0 – D7 не влияет на состояние выходов Q0 – Q7. При переходе сигнала ОЕ из состояния низкого уровня в высокий выхода Q0 – Q7 переходят в 3-е состояние.

Сигналы управления буферным регистром формируются шинным контролером, подробная разработка которого не входит в задачу данного курсового проекта.

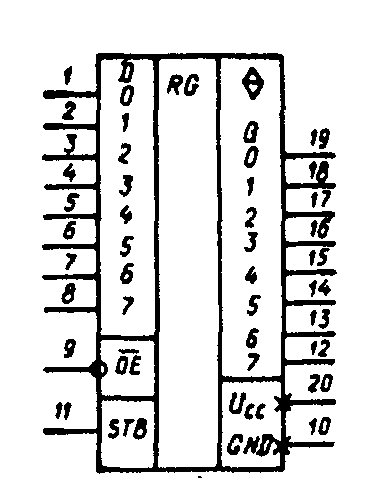

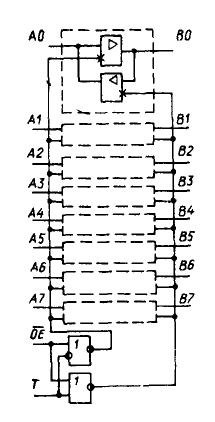

5.3.3 Шинный формирователь КР580ВА86

Микросхема КР580ВА86 двунаправленный 8-разрядный шинный формирователь, предназначенный для обмена данными между микропроцессором и системной шиной данных ЭВМ. Обладают повышенной нагрузочной способностью. Микросхема КР580ВА86 – формирователь без инверсии с тремя состояниями на выходе. Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления.

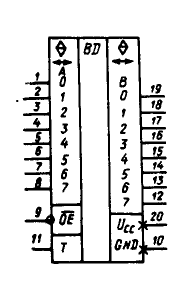

Рисунок 5.5 Условное графическое обозначение и функциональная схема КР580ВА86.

Назначение выводов микросхемы следующее:

- А0 – А7 входные (выходные) информационные сигналы;

- В0 – В7 выходные (входные) информационные сигналы:

- T выбор направления передачи;

- OE сигнал разрешения передачи данных.

При высоком уровне сигнала на входе ОЕ разрешена передача данных. Если на входе Т высокий уровень передача данных происходит в направлении от А к В, при низком наоборот от В к А. При низком уровне сигнала на входе ОЕ выводы А0 – А7 и В0 – В7 переходят в третье состояние.

Сигналы управления шинным формирователем подаются, как и для адресных регистров, формируются шинным контроллером.

5.4 Разработка структуры микро-ЭВМ

Структура микро ЭВМ показана на рисунке 5.6. При разработке структуры микро ЭВМ учитывалось следующие:

- набор операций выполняемых микро ЭВМ;

- состав базисных БИС окружения процессора;

- отсутствие в составе ЭВМ внешних устройств ввода вывода;

- отсутствие в составе ЭВМ графического адаптера дисплея и т.п..

Подключение БИС окружения на рисунке 5.6. показаны условно.

5.5 Описание функционирования микро-ЭВМ

При подаче напряжения на узлы ЭВМ, схемой формирования сигнала начальной установки на входе RES тактового генератора - микросхема КР1810ГФ84 на короткое время устанавливается низкий уровень. В результате тактовый генератор формирует на выходе RESET в течении 14 тактов также устанавливается низкий уровень. Аналогично сигналы RES и RESET устанавливаются при отпускании кнопки СБРОС, что соответствует перезагрузке компьютера.

Рисунок 5.6 – Схема разработанной микропроцессорной системы

За период 14 тактов, при низком уровне сигнала RESET на входе микропроцессора, микропроцессор производит очистку всех регистров кроме регистра IP. В регистр сегмента кода CS заносится значение FFFFh и соответствующее значение со сдвигом влево на 4 бита устанавливается на шине адреса. Сигналы управления принимают следующие значения COD = 1, IO = 0, I1 = 1. Такое состояние управляющих сигналов сообщает внешним устройствам, что процессор готов к чтению команды из памяти. В результате после завершения начальной установки процессора, будет начата передача процессору программы хранящейся в ПЗУ. В реальных микропроцессорных системах в ПЗУ по адресу с нулевым смещением хранится программа обеспечивающая тестирование устройств процессора и в случае успешного прохождения теста загрузку в ОЗУ операционной системы из внешних устройств памяти.

Разработка взаимодействия микропроцессора с устройствами внешней памяти и разработка операционной системы выходят за рамки данного курсового проекта. Поэтому узлы внешних устройств ввода-вывода показанные на рисунке 5.6 штриховыми линиями, представлены очень упрощенно. Так как наше микро ЭВМ не имеет операционной системы как таковой, программу выполнения заданного набора команд и исходные данные для расчета располагаем на внешнем устройстве ввода – вывода, из которого программа и данные загружаются в ОЗУ условно. Детализация процессов и алгоритма загрузки программы и исходных данных в рамках курсового проекта не проводилась. В связи с этим в ПЗУ будет хранится минимальный набор команд обеспечивающих установку регистров сегмента команд, сегмента данных и чтение первой команды из ОЗУ ЭВМ. Выбор программы обеспечивающей выполнение заданного набора операций задается набором DIP-переключателей в схеме управления.

При установке на шине адреса значения FFFF0h , селектор адресов ЗУ разрешает чтение данных из ПЗУ. Как указано выше в результате работы программы записанной в ПЗУ производится запись данных в сегментные регистры, счетчик команд и формирование на шине адреса номера ячейки памяти ОЗУ хранящую первую команду выполняемой программы.

Разработанная ЭВМ может выполнять заданную программу в двух режимах: пошаговом и автоматическом. При пошаговом режиме схема управления на каждом четом такте, поступающем по входу PCLK (что соответствует одному такту процессора) формирует сигнал низкого уровня на входе INTP, приводящей к переводу процессора в режим ожидания. При этом значения всех регистров процессора сохраняются. Перевод сигнала INTP из низкого уровня в высокий осуществляется схемой управления при нажатии кнопки ШАГ. Переход из пошагового режима в автоматический может осуществляться в процессе выполнения программы. Чтение состояния DIP-переключателей производится при начальной установке, т.е. при включении компьютера или нажатии кнопки СБРОС. Поэтому изменение состояния DIP- переключателей во время выполнения программы, не вызывает никаких изменений в выполняемой программе.