- •1. Дати характеристику повного дешифратора

- •2. Навести принципову схему 4-канального мультиплексора з двома адресними входами

- •3. Дати характеристику неповного дешифратора

- •4. Етапи побудови логічної схеми

- •5. Дати характеристику мультиплексора

- •6. Прийоми, що використовуються у випадку, коли число ле більше за необхідне

- •7. Як реалізовується збільшення розрядів дешифратора?

- •8. Як реалізовується підключення дешифратора на селекцію (вибір) заданих вхідних кодів?

- •9. Операціїї, що виконують пріорітетні шифратори.

- •10. Навести класифікацію цифрових пристроїв за способом кодування двійкових змінних

- •11. Генератор тактових імпульсів

- •12. Два роди кодування імпульсних сигналів.

11. Генератор тактових імпульсів

Генератор тактової частоти (генератор тактових імпульсів) генерує електричні імпульси заданої частоти (зазвичай прямокутної форми) для синхронізації різних процесів в цифрових пристроях - ЕОМ, електронних годинниках і таймерах, мікропроцесорної та іншої цифрової техніки. Тактові імпульси часто використовуються як еталонна частота - вважаючи їх кількість, можна, наприклад, вимірювати часові інтервали.В мікропроцесорній техніці один тактовий імпульс, як правило, відповідає одній атомарної операції. Обробка однієї інструкції може проводитися за один або кілька тактів роботи мікропроцесора, в залежності від архітектури і типу інструкції. Частота тактових імпульсів визначає швидкість обчислень.

В залежності від складності пристрою, використовують різні типи генераторів.

Про деякі з них.

Класичний. У нескладних конструкціях, не критичних до стабільності тактового генератора, часто використовується послідовне включення декількох інверторів через RC-ланцюг. Частота коливань залежить від номіналів резистора і конденсатора. Основний мінус даної конструкції - низька стабільність. Плюс - гранична простота.

Тактовий генератор. Тактовий генератор - автогенератор, що формує робочі такти процесора («частоту»). У деяких процесорах виконується вбудованим. Крім тактового процесора в обов'язки тактового генератора входить організація циклів системної шини. Тому його робота часто тісно пов'язана з циклами оновлення пам'яті, контролером ПДП і дешифратором сигналів стану процесора.

12. Два роди кодування імпульсних сигналів.

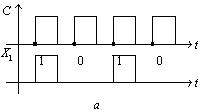

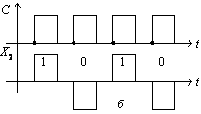

Для імпульсних сигналів розрізняють два роди кодування (рис. 1.5): перший – наявність імпульсу відображає лог. 1, відсутність – лог. 0; другий – наявність імпульсу однієї полярності відображає лог. 1, а іншої полярності – лог. 0.

Рис. 1.5. Імпульсне кодування: а – першого роду; б – другого роду

Як співвідносяться за розрядністю шини даних шифратора:

1) вихідна шина має більшу розрядність, ніж вхідна;

2) вхідна шина має більшу розрядність, ніж вихідна;

3) мають однакову розрядність

Шифратор перетворює коди:

1) з двійкового в унітарний;

2) з унітарного в двійковий;

3) з двійкового в десятковий.

Входи дешифратора, на які надходить вхідний код, називаються:

1) стробуючими;

2) шифруючими;

3) адресними;

4) управляючими;

5) синхронізуючими.

Мікросхеми шифраторів позначають на схемах буквами:

1) MS;

2) DC;

3) CD;

4) SH;

5) MP.

Мікросхеми дешифраторів позначають на схемах буквами:

1) MS;

2) DC;

3) CD;

4) SH;

5) MP.

Мікросхеми мультиплексорів позначають на схемах буквами:

1) MS;

2) DC;

3) CD;

4) SH;

5) MP.

Вкажіть допустиме число активних виходів дешифратора:

1) 1;

2) 2;

3) 3;

4) в залежності від типу мікросхеми і коду.

Вкажіть допустиме число активних виходів шифратора:

1) 1;

2) 2;

3) 3;

4) в залежності від типу мікросхеми і коду.

Вкажіть допустиме число активних виходів мультиплексора:

1) 1;

2) 2;

3) 3;

4) в залежності від типу мікросхеми і коду.

Повним дешифратором називається комбінаційна схема, яка має:

1) n входів, 2n виходів і реалізує на кожному виході функцію, що є макстермом n змінних;

2) n входів, 2n виходів і реалізує на кожному виході функцію, що є мінтермом n змінних;

3) 2n входів, n виходів і реалізує на кожному виході функцію, що є мінтермом n змінних;

4) 2n входів, n виходів і реалізує на кожному виході функцію, що є макстермом n змінних;

5) n входів, 2n виходів і реалізує на кожному виході функцію, що є мінтермом 2n змінних;

6) 2n входів, n виходів і реалізує на кожному виході функцію, що є мінтермом 2n змінних.

Неповним дешифратором називається комбінаційна схема, яка має:

1) m<2n входів, 2n виходів і реалізує на кожному виході функцію, що є макстермом n змінних;

2) m<2n входів, 2n виходів і реалізує на кожному виході функцію, що є мінтермом n змінних;

3) 2n входів, m<2n виходів і реалізує на кожному виході функцію, що є мінтермом n змінних;

4) 2n входів, m<2n виходів і реалізує на кожному виході функцію, що є макстермом m<2n змінних;

5) m>2n входів, 2n виходів і реалізує на кожному виході функцію, що є мінтермом 2n змінних;

6) 2n входів, m<2n виходів і реалізує на кожному виході функцію, що є мінтермом 2n змінних.

Шифратором називається комбінаційна схема, яка має:

1) 2n≥m входів, n виходів;

2) 2n≥m входів, 2n виходів;

3) 2n входів, n виходів;

4) m>2n входів, 2n виходів;

5) n входів, 2n виходів;

6) 2n входів, m<2n виходів.