- •Содержание

- •Лабораторная работа № 4 триггеры

- •1. Введение

- •6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Cинтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Создание дешифратора

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •Группа 2

- •Лабораторная работа № 8 Проектирование цифровых устройств в pcad 2001

- •Введение

- •Лабораторная работа № 8.1 Создание схемного элемента

- •1. Создание символа элемента

- •2. Редактирование символов

- •3. Контрольные вопросы

- •2. Внесение изменений в схему

- •3. Вывод схемы на печать

- •4. Контрольные вопросы

3. Регистры сдвига

Регистр сдвига представляет собой схему на триггерах, соединения между которыми обеспечивают передачу двоичной информации от одних триггеров регистра к другим.

Сдвиги могут выполняться на один или несколько разрядов. Применяются сдвиги на i разрядов как в сторону младших разрядов числа (правый сдвиг), так и в сторону старших разрядов числа (левый сдвиг).

Основная трудность, которая возникает при построении сдвиговых регистров, состоит в том, что при выполнении сдвига каждый запоминающий элемент (разряд) должен одновременно и выдавать информацию в следующий разряд и принимать новую информацию из предыдущего разряда. При построении регистров сдвига чаще всего используют синхронные D- или JK-триггеры с динамическим управлением записью либо с двухступенчатой организацией.

Полностью интегральные сдвиговые регистры построены на синхронных RS- или D-триггерах (двухступенчатых или с динамическим управлением записью). Внутренняя организация триггерных схем уже предусматривает разделение во времени этапов приема входной информации и смены выходного сигнала триггера. По одному фронту синхронизирующего импульса происходит прием информации, по другому - смена выходного сигнала. Это позволяет обойтись одной триггерной схемой на каждый разряд при построении регистров сдвига.

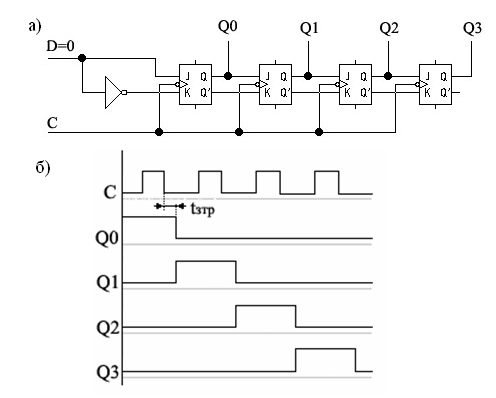

На рис. 10,а приведена схема регистра сдвига на один разряд вправо на JK-триггерах. Для реализации функции сдвига вправо необходимо соединить прямой выход триггера i-гo разряда с входом J триггера (i +1)-го разряда, а инверсный выход - с входом К. Объединенные синхронизирующие входы всех триггеров образуют шину сдвига С. Сдвиг на один разряд выполняется подачей одного импульса на шину сдвига. В момент поступления этого импульса значения сигналов на входах J и К каждого триггера определяют его переход в новое состояние. Это новое состояние каждый триггер принимает после окончания импульса сдвига. На рис. 10,б приведена временная диаграмма, поясняющая работу регистра сдвига.

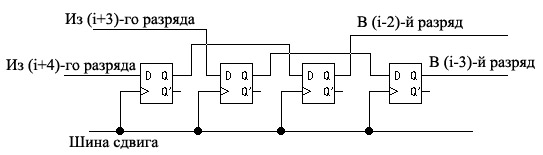

Регистр сдвига на два разряда вправо, построенный на D-триггерах, приведен на рис. 11. В отличие от аналогичной схемы на JK-триггерах здесь используется меньшее число линий связи между триггерами регистра.

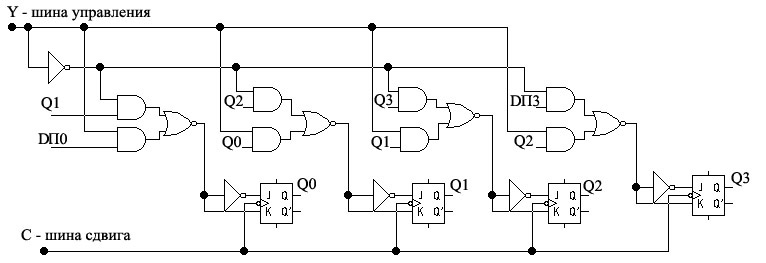

Регистры, выполняющие как левый, так и правый сдвиги, называют реверсивными регистрами сдвига. Схема такого регистра на JK-триггерах показана на рис. 12. Данный регистр помимо шины сдвига имеет шину управления Y. Ее назначение состоит в том, чтобы из двух микроопераций сдвига, выполняемых регистром, выбрать одну, требуемую в данный момент времени. Таким образом, сигнал, поступающий на шину управления, настраивает определенную цепь сдвига от одних триггеров к другим и запрещает работу остальных цепей. При Y = 1 информация сдвигается вправо, при Y = 0 - влево.

Рис. 10. Регистр сдвига на JK-триггерах и временная диаграмма его работы:

С - шина сдвига.

Р ис.

11. Регистр сдвига на два разряда вправо

на D-триггерах

ис.

11. Регистр сдвига на два разряда вправо

на D-триггерах

4. Цепи ввода и вывода информации в регистрах

В рассмотренных схемах предполагается последовательный ввод и вывод информации. Однако важна и возможность параллельного ввода и вывода информации. Пример схемы сдвигового регистра с последовательным и параллельным вводом и выводом информации приведен на рис. 13.

Регистр, находящийся в произвольном состоянии, устанавливается в любое требуемое состояние подачей кода на параллельные входы D0, D1, D2 и единичного сигнала на синхронизирующий вход Сзагр (параллельная загрузка).

Р ис.

12. Реверсивный регистр сдвига: DП0

- вход для последовательного приема

информации в регистр при сдвиге вправо;

DП3

- вход для последовательного приема

информации в регистр при сдвиге влево

ис.

12. Реверсивный регистр сдвига: DП0

- вход для последовательного приема

информации в регистр при сдвиге вправо;

DП3

- вход для последовательного приема

информации в регистр при сдвиге влево

Последовательный вывод информации происходит подачей серии тактовых импульсов на шину сдвига и снятия кода с выхода триггера последнего разряда регистра. Параллельный вывод информации может быть осуществлен непосредственно с выходов триггеров регистра или через вспомогательные элементы подачей единичного сигнала на управляющие входы Y1 и Y2 (см. рис. 13).

Регистры сдвига могут быть использованы полностью или частично в зависимости от применения регистра.

В приведенной схеме (см. рис. 13) параллельный ввод информации реализуется по асинхронным входам S и R триггеров регистра. Некоторые схемы интегральных регистров построены на триггерах, не имеющих асинхронных входов R и S.

Поэтому для обеспечения параллельного ввода информации в регистр сдвига необходима дополнительная логика. На рис. 14 приведена схема такого регистра сдвига. При Y = 1 регистр находится в режиме сдвига информации, т.е. с поступлением тактового импульса на вход С произойдет сдвиг кода на один разряд вправо. При Y = 0 регистр переводится в режим параллельной загрузки. С поступлением тактового импульса на вход С произойдет запись кода D0, D1, D2 в триггеры регистра.