- •Содержание

- •Лабораторная работа № 4 триггеры

- •1. Введение

- •6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Cинтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Создание дешифратора

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •Группа 2

- •Лабораторная работа № 8 Проектирование цифровых устройств в pcad 2001

- •Введение

- •Лабораторная работа № 8.1 Создание схемного элемента

- •1. Создание символа элемента

- •2. Редактирование символов

- •3. Контрольные вопросы

- •2. Внесение изменений в схему

- •3. Вывод схемы на печать

- •4. Контрольные вопросы

2. Регистры памяти

Наиболее простыми регистрами являются регистры памяти. Их назначение — хранение двоичной информации небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных RS‑ или D‑триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) информации производится параллельным кодом (либо запись во все, либо считывание со всех разрядов одновременно).

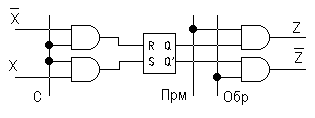

Ввод информации в регистры, на RS‑триггерах, возможен либо парафазный, либо однофазный. Парафазный ввод обеспечивается тактовым импульсом C (см. рис. 1), с приходом очередного тактового импульса записанная информация обновляется. При отсутствии С информация в регистре сохраняется без изменения.

На рис.1

показан ввод информации в прямом коде

(![]() на R, Х на S)

для ввода в обратном коде необходимо

на R, Х на S)

для ввода в обратном коде необходимо

![]() и Х поменять местами (

и Х поменять местами (![]() - на S, Х - на R).

- на S, Х - на R).

Р ис.

1. Схема одного разряда регистра хранения

с парафазным приемом и однофазной

выдачей информации

ис.

1. Схема одного разряда регистра хранения

с парафазным приемом и однофазной

выдачей информации

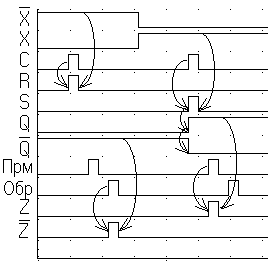

Временная диаграмма работы одного разряда регистра по схеме рис. 1 показана на рис. 2.

На временной диаграмме рис. 2 стрелками показаны сигналы, участвующие в формировании соответствующего сигнала.

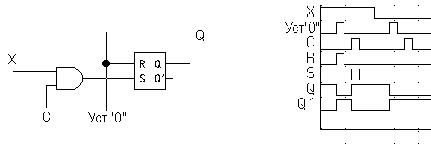

Прием информации в регистр на RS‑триггерах по однофазной схеме показан на рис. 3. В этом случае перед занесением новой информации регистр необходимо обнулить, подав импульс Уст“0” на общий вход всех разрядов. Временная диаграмма показана на рис. 3,б.

Для

ввода информации в обратном коде

необходимо вместо Х подать

![]() или сигналы на входах R

и S поменять местами:

Х на R а "Уст 0"

- заменить на "Уст 1", подаваемый на

вход S.

или сигналы на входах R

и S поменять местами:

Х на R а "Уст 0"

- заменить на "Уст 1", подаваемый на

вход S.

Р ис.

2. Временная диаграмма работы регистра

по схеме рис. 1

ис.

2. Временная диаграмма работы регистра

по схеме рис. 1

Наиболее просто однофазный ввод информации реализуется в регистрах на синхронных D‑триггерах (см. рис. 4). Информация в таком регистре меняется по сигналу C без его предварительного обнуления.

Р ис.

3. Один разряд регистра на RS‑триггере

с однофазным вводом информации и его

временная диаграмма

ис.

3. Один разряд регистра на RS‑триггере

с однофазным вводом информации и его

временная диаграмма

Р ис.

4. Один разряд регистра на D

‑триггере и его временная диаграмма

ис.

4. Один разряд регистра на D

‑триггере и его временная диаграмма

Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, входы C и R которых подсоединяют к общим шинам синхронизации и сброса.

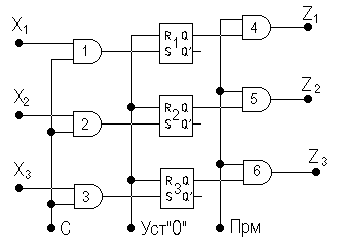

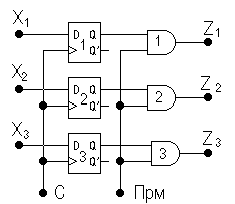

На рис. 5 изображена схема регистра хранения трехразрядного слова. Регистр построен на RS‑триггерах. Прием и выдача информации в этом регистре производятся по однофазной схеме.

Пусть до приема новой информации в регистре находилось число 3 (X3 = 0, X2 = 1, X1 = 1). Новое число, которое поступило на входы X3, X2, X1, равно 5 (101). Загрузка этого числа в регистр и выдача его на выходные шины Z3, Z2, Z1 производится следующим образом.

Р ис.

5. Регистр хранения на RS‑триггерах

с однофазным приемом

ис.

5. Регистр хранения на RS‑триггерах

с однофазным приемом

и однофазной выдачей информации

Сначала подается импульс установки регистра в 0 – Уст “0”. Все разряды регистра устанавливаются в 0. Затем на вход C подается импульс приема нового числа. Этот импульс проходит только через конъюнкторы И1 и И3, на другие входы которых поступили единичные значения X1 и X3 (через И2 импульс пройти не может, так как на другой вход этого элемента поступает нулевое значение сигнала X2). Под воздействием импульсов, появившихся на выходах элементов И1 и И3 и поступивших на входы S, триггеры T1 и T3 перейдут в состояние 1. Триггер T2 своего нулевого состояния не изменит, так как на его входах никаких импульсов нет.

Считывание нового числа из регистра в прямом коде производится импульсным сигналом Прм (конечно можно считывание произвести и потенциальным сигналом, но не надо забывать про гонки сигналов и борьбу с ними).

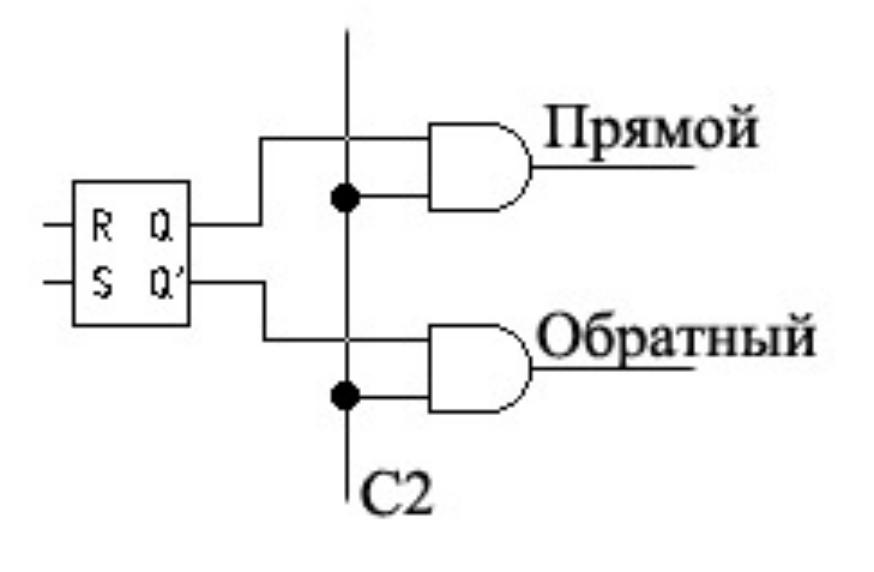

Двухфазный съем информации прямым и обратным кодом одновременно производится по схеме рис. 6.

Р ис.

6

ис.

6

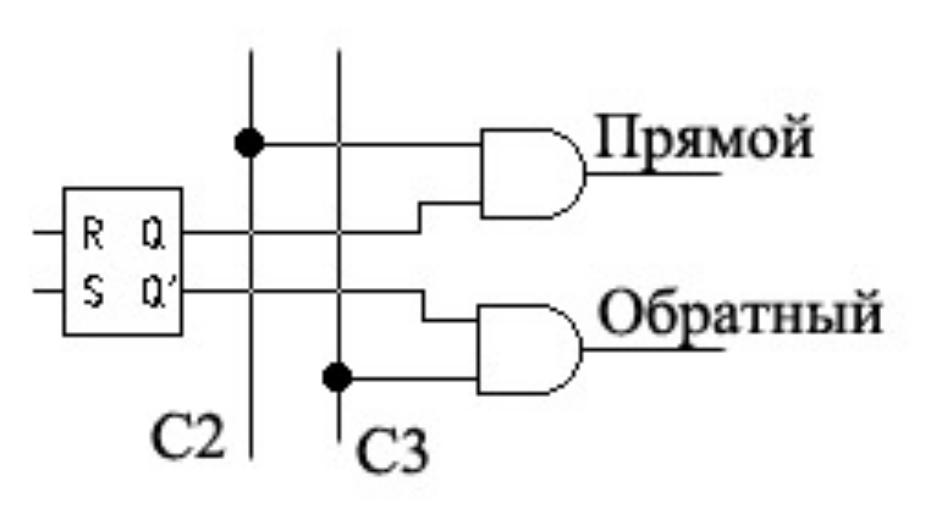

Выдача информации прямым и обратным кодом за два такта производится по схеме рис. 7.

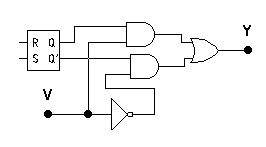

Выдача информации прямым или обратным кодом выполняется по схеме рис. 8.

При V = 1 на Y выдается прямой код, при V = 0 обратный код.

Р ис.

7

ис.

7

Р ис.

8

ис.

8

На рис. 9 показана схема трехразрядного регистра хранения на D‑триггерах, выполняющего те же функции, что и регистр, показанный на рис. 5.

Р ис.

9. Регистр хранения на D‑триггерах

ис.

9. Регистр хранения на D‑триггерах

В этом регистре отсутствует шина установки регистра в состояние 0, так как сбрасывать регистр в 0 здесь не требуется.

ЗАДАНИЕ 1. Нарисуйте схему и временную диаграмму работы регистра хранения на JK‑триггерах, не имеющих R и S входов. Съем информации с регистра должен быть парафазным.

ЗАДАНИЕ 2. Создайте в EWB четырехразрядный регистр хранения на D‑триггерах с парафазным съемом информации в прямом или обратном коде.

УКАЗАНИЕ. С каждого разряда снимается прямой и обратный парафазный код и через два мультиплексора MS2–1 сигналы поступают на внешние выходы так, что при единичном значении управляющего сигнала на выходы подается прямой парафазный код, при нулевом значении этого сигнала на выходы поступает обратный парафазный код.

ЗАДАНИЕ 3: Нарисуйте схему приема информации на асинхронные и синхронные JK-триггеры.