- •Содержание

- •1. Создание схем 123

- •2. Технология составления отчета 129

- •Лабораторная работа №1 логические функции и схемы

- •1. Комбинационные схемы

- •2. Аксиомы алгебры логики

- •3. Тождества алгебры логики

- •4. Логические функции

- •5. Таблица истинности

- •6. Аналитическое представление логических функций

- •7. Карты Карно

- •8. Частично определенные логические функции

- •9. Система логических функций

- •10. Подготовка к выполнению работы

- •11. Порядок выполнения работы

- •12. Отчет по работе

- •13. Контрольные вопросы и задания

- •Варианты заданий Логические функции трех переменных

- •Системы логических функций четырех аргументов

- •Лабораторная работа №2 дешифраторы

- •1. Принцип действия дешифраторов

- •2. Каскадирование дешифраторов

- •3. Дешифратор в качестве демультиплексора

- •4. Структуры дешифраторов

- •5. Реализация логических функций на дешифраторах

- •6. Дешифратор десятичного кода

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Контрольные вопросы и задания

- •Варианты заданий: Десятичные коды

- •Лабораторная работа №3 мультиплексоры

- •1. Мультиплексоры

- •2. Уравнение мультиплексора

- •3. Наращивание информационной емкости мультиплексоров

- •4. Реализация логических функций на мультиплексорах

- •5. Подготовка к выполнению работы

- •6. Порядок выполнения работы

- •7. Отчет по работе

- •8. Контрольные вопросы и задания

- •1.6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Синтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •6. Варианты заданий

- •Группа 2

- •Литература

- •Приложение

- •1. Создание схем

- •1.1. Технология построения схем

- •Путем настройки приборов можно осуществить следующее:

- •Графические возможности программы позволяют:

- •1.2. Исследование схем

- •1.3. Контрольные вопросы

- •2. Технология составления отчета

- •2.1. Требования к отчету

- •2.2. Вывод результатов на принтер

Лабораторная работа №2 дешифраторы

Цель работы: ознакомление с принципом работы дешифраторов, реализация и исследование функциональных узлов на основе дешифраторов.

1. Принцип действия дешифраторов

Дешифратор – комбинационная логическая схема – преобразователь двоичного (или какого либо другого кода) в унитарный код, которая имеет n информационных входов (их называют также адресными входами) и m выходов.

Если у дешифратора m = 2n, то он называется полным. Если число выходов дешифратора меньше 2n, то дешифратор называется неполным.

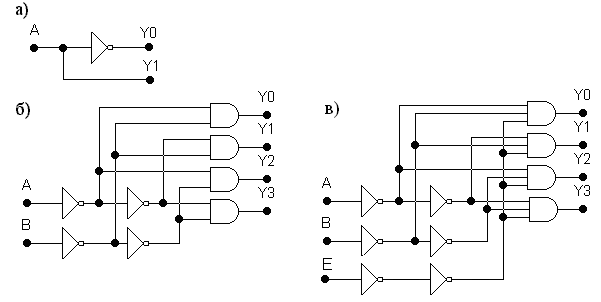

Простейший дешифратор имеет один вход (n = 1) и два выхода 21 = 2 – рис. 2.1,а, где А – вход, Y0 и Y1 – выходы.

У этого дешифратора

при А = 0 Y0 = 1 и Y1 = 0, а при А = 1 Y0 = 0 и Y1 = 1.

На рис. 2.1,б показана схема дешифратора с двумя входами A и B и четырьмя выходами Y0, Y1, Y2, Y3. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из четырех (22) выходов. Например, если на входы подана комбинация логических уровней 01, то на выходе с номером N = 1 установится единичный уровень сигнала (Y1 = 1), а все остальные выходы будут иметь уровень логического нуля. Этот принцип формирования выходного сигнала можно описать следующим образом:

![]()

Рис. 2.1. Схемы дешифраторов 1-2 и 2-4:

а), б) без входа управления; в) с входом управления E

Помимо информационных входов, дешифраторы обычно имеют один или несколько дополнительных входов управления (разрешения) (на рис. 2.1,в – это вход E).

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом — уровень логического нуля.

В схеме рис.2.1,в сигнал на входе E при значении 1 разрешает нормальное функционирование дешифратора, а при значении 0 переводит его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах схемы установится неактивный уровень логического нуля.

ЗАМЕЧАНИЕ. В схемах дешифраторов практически все входные сигналы (информационные и управляющие) подаются через инверторы с целью разгрузки источников сигналов (см. рис. 2.1,в).

В интегральном исполнении дешифраторов число адресных входов n обычно равно 2, 3 или 4.

На рис. 2.2 изображен дешифратор с n = 3 и одним инверсным входом управления, активным уровнем на выходе является уровень логического нуля. На входы С, В, А можно подать 8 комбинаций логических уровней 000, 001, 010,…, 111 (А – младший разряд). Соответственно схема имеет 8 выходов, на одном из которых формируется низкий потенциал, на остальных – высокий. Номер этого единственного выхода, на котором формируется активный (нулевой) уровень, соответствует десятичному числу N, определяемому состоянием входов С, В, А

N = 22С + 21В + 20А.

Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

![]()

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, в дешифраторе 3-8 микросхемы К555ИД7 (зарубежный аналог – микросхема 74138) с одним прямым входом управления G1 и двумя инверсными G2A’ и G2B’ (рис.2.3.) функция разрешения G имеет вид

![]() .

.

Входы управления используются для каскадирования (увеличения разрядности) дешифраторов, стробирования или при параллельной работе нескольких дешифраторов на общие выходные линии.

На основе словесного описания принципа действия дешифратора можно составить таблицы истинности для дешифраторов с активной единицей и активным нулем на выходах (см. табл. 2.1 и 2.2):

Из таблицы 2.1 для выходов дешифратора с активной единицей получаем такие выражения

![]()

Из таблицы 2.2 для дешифратора с активным нулем будем иметь

![]()

Таблица 2.1 Таблица 2.2

Активная единица |

|

|

Активный нуль |

||||||||||||

№ |

b |

a |

y0 |

y1 |

y2 |

y3 |

|

|

№ |

b |

a |

y0 |

y1 |

y2 |

y3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

2 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

2 |

1 |

0 |

1 |

1 |

0 |

1 |

3 |

1 |

1 |

0 |

0 |

0 |

1 |

|

|

3 |

1 |

1 |

1 |

1 |

1 |

0 |

Р ис.

2.2. Дешифратор с одним Рис. 2.3. Дешифратор

с тремя

ис.

2.2. Дешифратор с одним Рис. 2.3. Дешифратор

с тремя

входом управления G' входами управления G1, G2A', G2B'