- •Содержание

- •1. Создание схем 123

- •2. Технология составления отчета 129

- •Лабораторная работа №1 логические функции и схемы

- •1. Комбинационные схемы

- •2. Аксиомы алгебры логики

- •3. Тождества алгебры логики

- •4. Логические функции

- •5. Таблица истинности

- •6. Аналитическое представление логических функций

- •7. Карты Карно

- •8. Частично определенные логические функции

- •9. Система логических функций

- •10. Подготовка к выполнению работы

- •11. Порядок выполнения работы

- •12. Отчет по работе

- •13. Контрольные вопросы и задания

- •Варианты заданий Логические функции трех переменных

- •Системы логических функций четырех аргументов

- •Лабораторная работа №2 дешифраторы

- •1. Принцип действия дешифраторов

- •2. Каскадирование дешифраторов

- •3. Дешифратор в качестве демультиплексора

- •4. Структуры дешифраторов

- •5. Реализация логических функций на дешифраторах

- •6. Дешифратор десятичного кода

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Контрольные вопросы и задания

- •Варианты заданий: Десятичные коды

- •Лабораторная работа №3 мультиплексоры

- •1. Мультиплексоры

- •2. Уравнение мультиплексора

- •3. Наращивание информационной емкости мультиплексоров

- •4. Реализация логических функций на мультиплексорах

- •5. Подготовка к выполнению работы

- •6. Порядок выполнения работы

- •7. Отчет по работе

- •8. Контрольные вопросы и задания

- •1.6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Синтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •6. Варианты заданий

- •Группа 2

- •Литература

- •Приложение

- •1. Создание схем

- •1.1. Технология построения схем

- •Путем настройки приборов можно осуществить следующее:

- •Графические возможности программы позволяют:

- •1.2. Исследование схем

- •1.3. Контрольные вопросы

- •2. Технология составления отчета

- •2.1. Требования к отчету

- •2.2. Вывод результатов на принтер

4. Реализация логических функций на мультиплексорах

Полностью определенная логическая функция n переменных определена для 2n комбинаций значений переменных. Ее можно реализовать на мультиплексоре, имеющем n управляющих и 2n информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается соответствующее значение функции.

Пусть требуется реализовать функцию

F1 =

![]() ,

,

таблица истинности которой показана в табл. 3.2.

Таблица 3.2

№ |

С |

B |

А |

F1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

2 |

0 |

1 |

0 |

0 |

3 |

0 |

1 |

1 |

1 |

4 |

1 |

0 |

0 |

0 |

5 |

1 |

0 |

1 |

0 |

6 |

1 |

1 |

0 |

1 |

7 |

1 |

1 |

1 |

1 |

Эта функция зависит от трех переменных, поэтому она определена для 8 комбинаций значений переменных и ее можно записать так

![]()

Уравнение мультиплексора с тремя управляющими входами MS 8–1 имеет вид

![]()

Как видим, структура уравнений полностью совпадает, поэтому данную функцию можно реализовать на мультиплексоре MS 8-1 с тремя управляющими входами A, B, C, подав на информационные входы D0, …, D7 соответствующие значения функции.

В данном случае на входы с номерами 1, 2, 4, 5 следует подать уровень логического нуля, а на остальные – уровень логической единицы, т.е.

D0 = 1, D1 = 0, D2 = 0, D3 = 1, D4 = 0, D5 = 0, D6 = 1, D7 = 1.

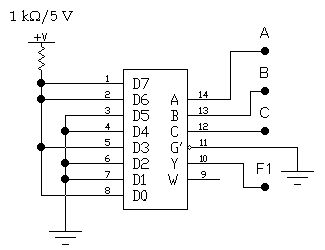

Таким образом, при изменении комбинаций логических уровней на управляющих входах мультиплексора к его выходу будут подключаться входы, значения сигналов на которых равны соответствующим значениям функции. Схемная реализация приведена на рис. 3.8.

В общем случае можно сформулировать следующее правило:

если количество логических переменных n, от которых зависит реализуемая логическая функция, совпадает с разрядностью адресной части мультиплексора, то эти переменные подаются на адресные входы мультиплексора (старшая переменная - на старший адресный вход), а на информационные входы мультиплексора MS 2n–1 – константы 0 и 1 в соответствии с таблицей истинности реализуемой функции.

Р ис.

3.8. Реализация функции F1

на мультиплексоре 8-1

ис.

3.8. Реализация функции F1

на мультиплексоре 8-1

При реализации логических функций на информационные входы можно подавать не только константы, но и изменяющиеся входные сигналы. Например, функцию F1, рассмотренную выше, можно реализовать по-другому следующим образом.

Минимизируем выражение функции. В результате получим

F1=

![]() .

.

Составим таблицу истинности функции в зависимости от значений переменных а и b (см. табл.3.3).

Таблица 3.3

N |

B |

A |

F1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

2 |

1 |

0 |

С |

3 |

1 |

1 |

1 |

Заданную

такой таблицей функцию реализуют на

мультиплексоре, как и в предыдущем

случае, подав на вход с номером N

сигнал, уровень которого соответствует

значению функции F1.

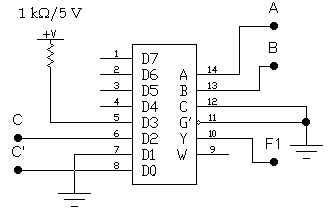

В данном случае сигналы С и

![]() ,

соответствующие переменной С,

подаются на информационные входы так,

как указано в таблице истинности. При

этом сокращается число управляющих

входов.

,

соответствующие переменной С,

подаются на информационные входы так,

как указано в таблице истинности. При

этом сокращается число управляющих

входов.

Схемная реализация такого способа задания функции представлена на рис. 3.9.

Так как используются только два адресных входа, то управляющий вход С можно заземлить. При этом состояние информационных входов D4,…,D7 безразлично.

Схема рис. 3.9 по существу представляет собой мультиплексор 4-1 с двумя управляющими и четырьмя информационными входами.

Если функцию можно представить в виде произведения одночлена на многочлен, то ее также можно реализовать при помощи мультиплексора с уменьшенным числом управляющих входов. Как следует из уравнения мультиплексора, сигнал, соответствующий одночлену, нужно подать на вход разрешения. Например, требуется реализовать на мультиплексоре 8-1 функцию F2 шести переменных, описываемую следующим выражением

F2=

![]()

При реализации данной функции на мультиплексоре сигнал, соответствующий переменной Х, следует подать на его разрешающий вход.

Рассмотрим, какие сигналы необходимо подать на управляющие входы мультиплексора. Выражение в скобках можно рассматривать как некоторую функцию F пяти переменных А, B, С, D, E, из которых наиболее часто используются переменные А, B и С. Поэтому сигналы, соответствующие этим переменным, целесообразно подать на три управляющих входа мультиплексора MS 8-1.

Р ис.

3.9. Второй вариант реализации функции

F1

ис.

3.9. Второй вариант реализации функции

F1

Определим, какие сигналы следует подать на информационные входы, чтобы реализовать функцию F2. Для этого составим таблицу истинности функции в зависимости от значений переменных А, B и С (табл. 3.4).

Таблица 3.4

N |

С |

B |

А |

F |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

D |

2 |

0 |

1 |

0 |

0 |

3 |

0 |

1 |

1 |

E |

4 |

1 |

0 |

0 |

D |

5 |

1 |

0 |

1 |

D |

6 |

1 |

1 |

0 |

0 |

7 |

1 |

1 |

1 |

1 |

Из таблицы видно, что на информационные входы с номерами N = 0, 2, 6 нужно подать уровень логического нуля. Сигнал, соответствующий переменной D, нужно подать на входы с номерами N = 1, 4, 5, а сигнал, соответствующий переменной Е, – на вход с номером 3. Схемная реализация функции шести переменных F2 представлена на рис. 3.10.