- •Содержание

- •1. Создание схем 123

- •2. Технология составления отчета 129

- •Лабораторная работа №1 логические функции и схемы

- •1. Комбинационные схемы

- •2. Аксиомы алгебры логики

- •3. Тождества алгебры логики

- •4. Логические функции

- •5. Таблица истинности

- •6. Аналитическое представление логических функций

- •7. Карты Карно

- •8. Частично определенные логические функции

- •9. Система логических функций

- •10. Подготовка к выполнению работы

- •11. Порядок выполнения работы

- •12. Отчет по работе

- •13. Контрольные вопросы и задания

- •Варианты заданий Логические функции трех переменных

- •Системы логических функций четырех аргументов

- •Лабораторная работа №2 дешифраторы

- •1. Принцип действия дешифраторов

- •2. Каскадирование дешифраторов

- •3. Дешифратор в качестве демультиплексора

- •4. Структуры дешифраторов

- •5. Реализация логических функций на дешифраторах

- •6. Дешифратор десятичного кода

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Контрольные вопросы и задания

- •Варианты заданий: Десятичные коды

- •Лабораторная работа №3 мультиплексоры

- •1. Мультиплексоры

- •2. Уравнение мультиплексора

- •3. Наращивание информационной емкости мультиплексоров

- •4. Реализация логических функций на мультиплексорах

- •5. Подготовка к выполнению работы

- •6. Порядок выполнения работы

- •7. Отчет по работе

- •8. Контрольные вопросы и задания

- •1.6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Синтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •6. Варианты заданий

- •Группа 2

- •Литература

- •Приложение

- •1. Создание схем

- •1.1. Технология построения схем

- •Путем настройки приборов можно осуществить следующее:

- •Графические возможности программы позволяют:

- •1.2. Исследование схем

- •1.3. Контрольные вопросы

- •2. Технология составления отчета

- •2.1. Требования к отчету

- •2.2. Вывод результатов на принтер

3. Наращивание информационной емкости мультиплексоров

Для получения мультиплексоров с большим числом информационных входов из мультиплексоров с малым числом информационных входов применяют схемы, показанные на рис. 3.5… 3.7.

Пусть требуется реализовать MS 8–1 (адресных входов здесь три).

Запишем его уравнение в виде двух строк:

![]()

В первой

строке адресная переменная a2

встречается только с инверсией,

а во второй – только без инверсии. Вынося

за скобки переменную

![]() в первой строке и a2

во второй, получим:

в первой строке и a2

во второй, получим:

![]() (1)

(1)

В выражении (1) в скобках записаны уравнения двух мультиплексоров MS 4–1 с общим адресом, представленным двумя младшими переменными a1, a0.

Будем рассматривать в первой строке и a2 во второй как разрешающие входы для этих мультиплексоров. Тогда уравнение MS 4–1 с активной единицей на входе разрешения Е будет иметь вид:

![]()

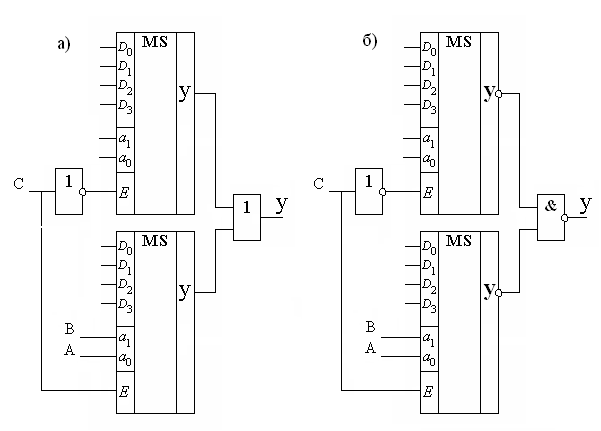

Структура такого мультиплексора приведена на рис. 3.3,б, а его функциональное обозначение – на рис. 3.5.

Если адресную переменную a2 подать через инвертор на вход Е первого мультиплексора MS 4–1, то мы реализуем первую часть выражения (1), а если ее подать непосредственно на вход Е второго мультиплексора MS 4–1, то мы реализуем вторую часть выражения (1).

Представим уравнение (1) в виде:

![]() ,

,

откуда видно, что для окончательной реализации MS 8–1 потребуется два MS 4–1 со входом разрешения, инвертор и либо двухвходовый элемент ИЛИ, если мультиплексор MS 4–1 реализован с активной единицей на выходе; либо двухвходовый элемент И-НЕ, если мультиплексор MS 4–1 реализован с активным нулем на выходе. Оба варианта схемы приведены на рис. 3.5

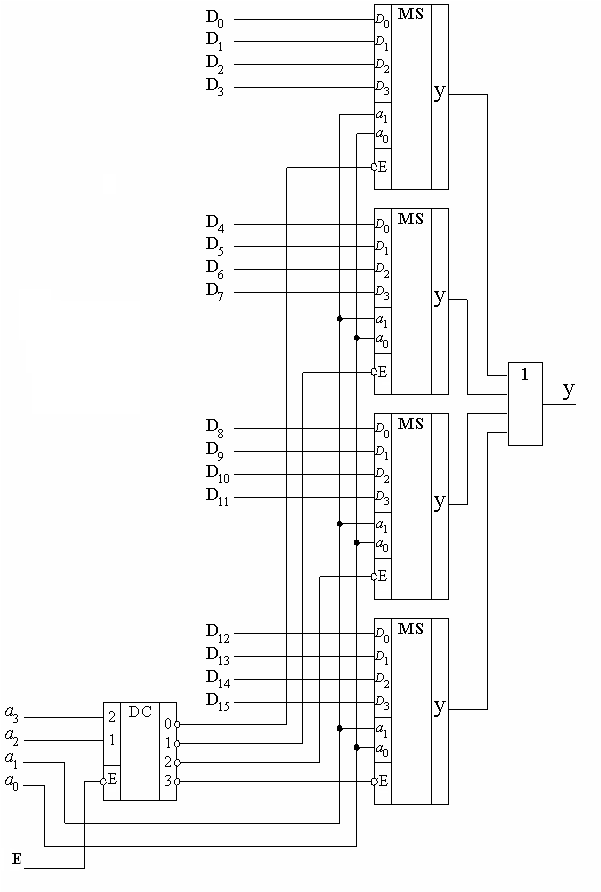

В схемах рис. 3.5 инвертор и шина С являются простейшим дешифратором. Заменив этот дешифратор дешифратором DC 2–4, можно построить мультиплексор MS 16–1 на четырех MS 4–1 и одном дешифраторе со входами разрешения (рис. 3.6), где вход Е дешифратора выполняет функцию входа разрешения всего MS 16–1.

Ясно, что такую структуру можно реализовать для любого числа входов.

Рассмотрим еще один способ построения мультиплексора MS 16–1 на базе мультиплексора MS 4–1.

Запишем уравнение для этого мультиплексора в виде матрицы из четырех строк и четырех столбцов (разрядность адреса для MS 16–1 равна четырем):

![]()

В этом выражении имеют единое представление в каждой строке две старшие адресные переменные, а в каждом столбце – две младшие.

Вынесем за скобки в каждой строке две старшие адресные переменные, тогда получим:

Рис. 3.5

![]() (2)

(2)

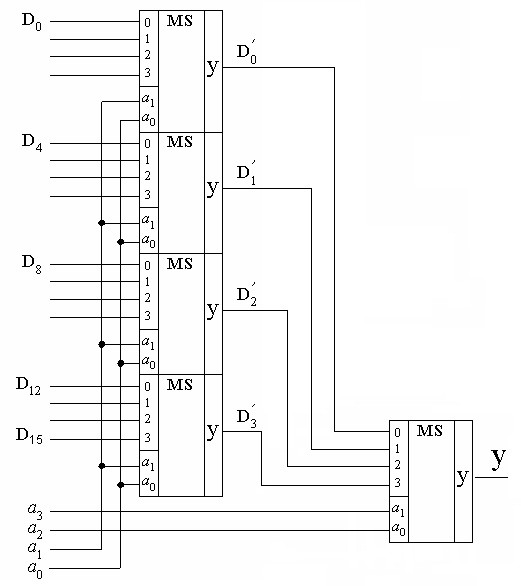

B этом выражении во всех строках в скобках записаны уравнения четырех MS 4–1 с общим адресом, представленным двумя младшими адресными переменными.

Рис. 3.6

Обозначим

выходы этих мультиплексоров соответственно

как

![]() ,

тогда уравнение (2) можно записать так

,

тогда уравнение (2) можно записать так

![]() .

.

то есть опять получили уравнение MS 4–1. Следовательно, всего потребуется пять MS 4–1.

Окончательная схема MS 16–1, построенная на пяти MS 4–1, приведена на рис. 3.7.

Рис. 3.7

Ясно, что такую структуру можно реализовать для любого числа входов, однако она имеет очевидный недостаток – существенное возрастание задержек распространения сигналов в последовательно включенных ярусах мультиплексоров.