- •Содержание

- •1. Создание схем 123

- •2. Технология составления отчета 129

- •Лабораторная работа №1 логические функции и схемы

- •1. Комбинационные схемы

- •2. Аксиомы алгебры логики

- •3. Тождества алгебры логики

- •4. Логические функции

- •5. Таблица истинности

- •6. Аналитическое представление логических функций

- •7. Карты Карно

- •8. Частично определенные логические функции

- •9. Система логических функций

- •10. Подготовка к выполнению работы

- •11. Порядок выполнения работы

- •12. Отчет по работе

- •13. Контрольные вопросы и задания

- •Варианты заданий Логические функции трех переменных

- •Системы логических функций четырех аргументов

- •Лабораторная работа №2 дешифраторы

- •1. Принцип действия дешифраторов

- •2. Каскадирование дешифраторов

- •3. Дешифратор в качестве демультиплексора

- •4. Структуры дешифраторов

- •5. Реализация логических функций на дешифраторах

- •6. Дешифратор десятичного кода

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Контрольные вопросы и задания

- •Варианты заданий: Десятичные коды

- •Лабораторная работа №3 мультиплексоры

- •1. Мультиплексоры

- •2. Уравнение мультиплексора

- •3. Наращивание информационной емкости мультиплексоров

- •4. Реализация логических функций на мультиплексорах

- •5. Подготовка к выполнению работы

- •6. Порядок выполнения работы

- •7. Отчет по работе

- •8. Контрольные вопросы и задания

- •1.6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Синтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •6. Варианты заданий

- •Группа 2

- •Литература

- •Приложение

- •1. Создание схем

- •1.1. Технология построения схем

- •Путем настройки приборов можно осуществить следующее:

- •Графические возможности программы позволяют:

- •1.2. Исследование схем

- •1.3. Контрольные вопросы

- •2. Технология составления отчета

- •2.1. Требования к отчету

- •2.2. Вывод результатов на принтер

7. Подготовка к выполнению работы

Изучить описание лабораторной работы.

Создать схему дешифратора 2-4 с одним входом управления. Активный уровень выходов дешифратора логический нуль.

Создать схему, реализующую на дешифраторе заданную логическую функцию трех переменных.

Создать схему, реализующую на дешифраторе заданную частично определенную логическую функцию четырех переменных.

Создать схему, реализующую на дешифраторе заданную систему логических функций четырех переменных.

УКАЗАНИЕ: Для реализации берутся логические функции, исследованные в лабораторной работе №1.

Создать дешифратор десятичного кода (код берется из Вариантов заданий к лабораторной работе № 2 по номеру исполнителя в журнале группы).

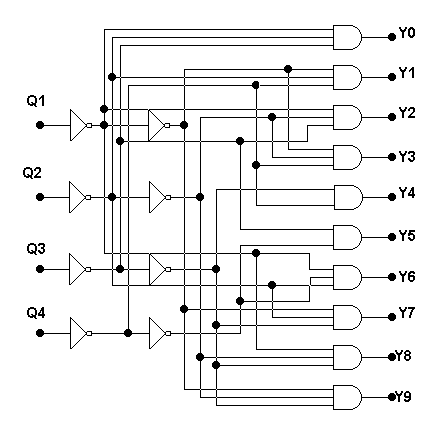

Рис. 2.9 – Дешифратор кода 2421

8. Порядок выполнения работы

Используя Electronics Workbench, синтезировать дешифратор 2-4 с одним входом управления. Активный уровень выходов дешифратора логический нуль. Провести моделирование и получить временные диаграммы. Оценить время задержки схемы, используя параметры элементов.

Из схемы п.1, создать субблок дешифратора 2-4 с одним входом управления. Используя полученный субблок, создать дешифраторы 3-8 и 4-16. Проверить их работоспособность моделированием.

Реализовать на дешифраторах логические функции, исследованные в лабораторной работе №1. Провести моделирование и получить временные диаграммы. Оценить время задержки схемы, используя параметры элементов.

Используя Electronics Workbench, создать дешифратор для заданного десятичного кода и проверить его работоспособность моделированием. (Десятичный код на входах дешифратора задать с помощью Генератора слов в шестнадцатеричном коде).

Показать преподавателю работу созданных схем с демонстрацией на экране логического анализатора временных диаграмм.

9. Отчет по работе

Отчет по работе должен содержать

исходные данные варианта задания.

Полученные таблицы.

Рисунки исследованных схем и их временные диаграммы.

оценку быстродействия полученных схем.

10. Контрольные вопросы и задания

В чем состоит принцип работы дешифратора?

Каким соотношением связаны число входов и число выходов полного дешифратора? А не полного?

Почему входные сигналы в схемах дешифраторов (рис. 2.1) подаются через инверторы?

Зачем нужен разрешающий вход E у дешифратора? Постройте схему дешифратора на заданное число выходов с прямым (инверсным) входом разрешения.

Постройте дешифратор на 8 выходов на элементах И (на элементах И‑НЕ).

Можно ли построить дешифратор на элементах ИЛИ (ИЛИ‑НЕ)? Если да, то как?

Постройте дешифратор 3‑8 из двух дешифраторов 2‑4.

Постройте дешифратор 4‑16 на базе готовых дешифраторов 2‑4 с разрешающим входом E. Сколько дешифраторов 2‑4 потребуется для решения этой задачи, если не использовать другие элементы?

Что представляет собой декодер‑демультиплексор? Постройте схему на заданное число выходов.

Постройте линейный дешифратор 4-16.

Постройте пирамидальный дешифратор 4–16.

Постройте матричный дешифратор 4–16.

Сравните сложность и быстродействие дешифраторов п.10 – 12.

Реализуйте на базе готового дешифратора произвольную логическую функцию, заданную СДНФ (СКНФ).

Каковы особенности дешифратора десятичного кода?