- •Содержание

- •1. Создание схем 123

- •2. Технология составления отчета 129

- •Лабораторная работа №1 логические функции и схемы

- •1. Комбинационные схемы

- •2. Аксиомы алгебры логики

- •3. Тождества алгебры логики

- •4. Логические функции

- •5. Таблица истинности

- •6. Аналитическое представление логических функций

- •7. Карты Карно

- •8. Частично определенные логические функции

- •9. Система логических функций

- •10. Подготовка к выполнению работы

- •11. Порядок выполнения работы

- •12. Отчет по работе

- •13. Контрольные вопросы и задания

- •Варианты заданий Логические функции трех переменных

- •Системы логических функций четырех аргументов

- •Лабораторная работа №2 дешифраторы

- •1. Принцип действия дешифраторов

- •2. Каскадирование дешифраторов

- •3. Дешифратор в качестве демультиплексора

- •4. Структуры дешифраторов

- •5. Реализация логических функций на дешифраторах

- •6. Дешифратор десятичного кода

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Контрольные вопросы и задания

- •Варианты заданий: Десятичные коды

- •Лабораторная работа №3 мультиплексоры

- •1. Мультиплексоры

- •2. Уравнение мультиплексора

- •3. Наращивание информационной емкости мультиплексоров

- •4. Реализация логических функций на мультиплексорах

- •5. Подготовка к выполнению работы

- •6. Порядок выполнения работы

- •7. Отчет по работе

- •8. Контрольные вопросы и задания

- •1.6. Контрольные вопросы

- •Лабораторная работа № 4.1 двухступенчатые триггеры

- •1. Постановка задачи

- •2. Пример проектирования двухступенчатого триггера

- •3. Экспериментальное исследование триггера

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •7. Варианты заданий

- •Группа 2

- •Лабораторная работа № 4.2 триггерные структуры на d- и jk-триггерах

- •1. Проектирование триггерных структур на d-триггерах

- •2. Проектирование триггерных структур на jk-триггерах

- •2. Синтез синхронных счетчиков

- •2.1. Счетчик на jk–триггерах

- •2.1. Счетчик на d–триггерах

- •3. Организация переноса

- •4. Примеры схем и временных диаграмм

- •5. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •9. Отчет по работе

- •10. Варианты заданий

- •Лабораторная работа № 6 Регистры

- •1. Введение

- •2. Регистры памяти

- •3. Регистры сдвига

- •4. Цепи ввода и вывода информации в регистрах

- •5. Регистры сдвига с обратными связями

- •5.1. Простое кольцо

- •5.2. Кольцо Мёбиуса – счетчик Джонсона

- •6. Контрольные вопросы

- •7. Подготовка к выполнению работы

- •8. Порядок выполнения работы

- •2. Проектирование конечных автоматов

- •2.1. Проектирование конечного автомата без учета времени

- •2.2. Проектирование конечного автомата с учетом времени

- •3. Контрольные вопросы

- •4. Подготовка к выполнению работы

- •5. Порядок выполнения работы

- •6. Отчет по работе

- •6. Варианты заданий

- •Группа 2

- •Литература

- •Приложение

- •1. Создание схем

- •1.1. Технология построения схем

- •Путем настройки приборов можно осуществить следующее:

- •Графические возможности программы позволяют:

- •1.2. Исследование схем

- •1.3. Контрольные вопросы

- •2. Технология составления отчета

- •2.1. Требования к отчету

- •2.2. Вывод результатов на принтер

2. Каскадирование дешифраторов

Очень часто в распоряжении разработчиков цифровой аппаратуры оказываются дешифраторы меньшей размерности, чем требуется. Вполне естественно возникает вопрос: Как построить дешифратор m-разрядного кода, если имеются дешифраторы n-разрядного кода, причем m > n?

Для ответа на этот вопрос рассмотрим уравнения полного дешифратора с активной единицей на выходах при n = 3:

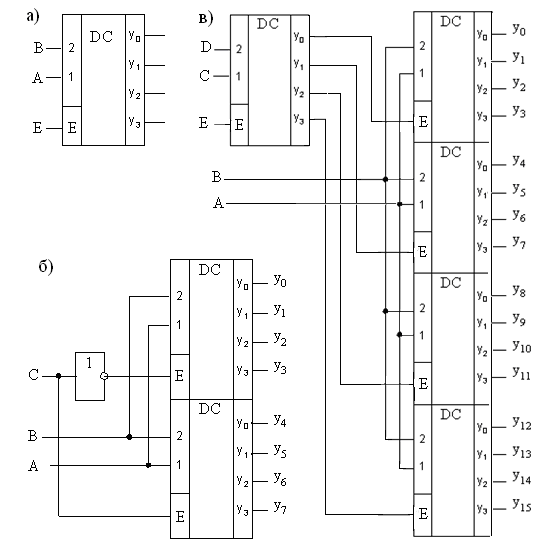

В уравнениях для y0...y3 переменная С встречается только с инверсией, а для y4...y7 – только без инверсии, в то время как переменные B и A образуют совпадающие комбинации в y0 и y4, y1 и y5 и т. д. Примем переменную C за вход разрешения Е для дешифратора 2 – 4 (см. рис. 2.1,в). функциональное обозначение этого дешифратора показано на рис. 2.4,а.

Из уравнений также видно, что для реализации дешифратора 3 – 8 необходимо взять два дешифратора 2 – 4 со входом управления и один внешний дополнительный инвертор. Получается схема, приведенная на рис. 2.4,б.

Заметим, инвертор и шина x2 – это простейший дешифратор 1 – 2 (рис. 2.1,а). Если вместо него взять дешифратор 2 – 4, то можно получить дешифратор 4 – 16 на пяти дешифраторах 2 – 4 (см. рис. 2.4,в). один из них будет дешифрировать наборы, представленные двумя старшими переменными, и управлять остальными четырьмя дешифраторами. Вход Е этого дешифратора будет являться входом управления для всего дешифратора 4 – 16.

Рис. 2.4. Схемы каскадирования дешифраторов:

а) условное обозначение дешифратора 2–4 со входом управления,

б) схема получения дешифратора 3–8 из двух дешифраторов 2–4,

в) схема получения дешифратора 4–16 из пяти дешифраторов 2–4

3. Дешифратор в качестве демультиплексора

Дешифратор может быть использован и как демультиплексор – логический коммутатор, подключающий входной сигнал к одному из выходов.

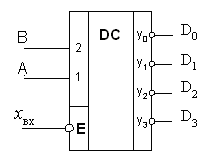

В этом случае функцию информационного входа выполняет вход разрешения E, а состояния адресных входов В и А задают номер выхода, на который передается сигнал со входа разрешения (см. рис. 2.5). Именно по этой причине дешифратор, имеющий разрешающий вход E, называют не просто декодер, а декодер-демультиплексор.

Пусть с помощью дешифратора рис. 2.5 необходимо передать данные со входа xвх на выход D1, т.е. по адресу 01 (на вход B подаем 0, на вход A подаем 1). Уравнение для выхода D1 будет таким

![]() .

.

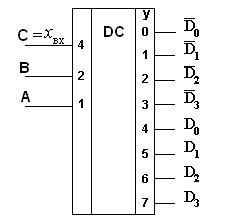

Если нет дешифратора со входом разрешения, то в качестве демультиплексора можно использовать дешифратор, имеющий n+1 адресный вход, в котором старший адресный вход используется в качестве информационного входа. В этом случае получим два демультиплексора с общими адресными и информационным входами: один из них будет передавать данные в обратном коде, а другой в прямом коде.

Рис. 2.5 Дешифратор со входом разрешения

в режиме демультиплексора

Продемонстрируем это на примере дешифратора 3–8 с активной единицей на выходах, в котором вход C используется как информационный (рис. 2.6).

Подадим адрес 01 на входы B, A и рассмотрим уравнения выходов с индексами 1 и 5.

В терминах дешифратора

![]() .

.

В терминах демультиплексора

![]() ,

,

![]() .

.

Рис. 2.6. Дешифратор без входа разрешения

в режиме демультиплексора