Лабораторная работа № 3

Процессор Intel 8086/88

Тема: функционирование процессоров х86 в реальном режиме.

Цель работы : изучение структуры, функционирования процессора Intel 8086/88, реального режима процессоров х86 и программной модели процессоров х86 в реальном режиме.

1. Ознакомление с теоретическими сведениями

Структура процессора

Впервые микропроцессор Intel 8086 был представлен 8 июня 1978 года. Основные параметры микропроцессора :

Тактовая частота (МГц): 5 (модель 8086), 8 (модель 8086-2), 10 (модель 8086-1)

Разрядность регистров: 16 бит

Разрядность шины данных: 16 бит

Разрядность шины адреса: 20 бит.

Объём адресуемой памяти: 1 Мбайт

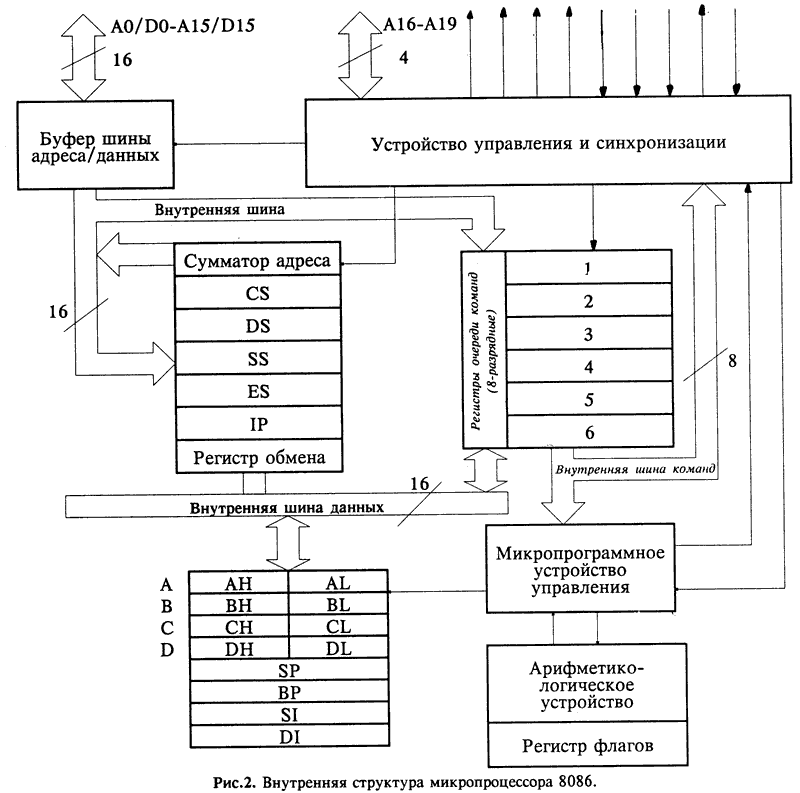

Структура микропроцессора состоит из двух сравнительно независимых устройств. Операционное устройство выполняет команды, а устройство шинного интерфейса формирует адрес, выбирает команды, считывает операнды и записывает результаты. Оба устройства могут работать параллельно и в большинстве случаев обеспечивают значительное совмещение выборки и выполнения команд. В результате этого время выборки не учитывается в цикле команды, так как операционное устройство выполняет команды, уже выбранные шинным интерфейсом. Таким образом впервые было введено понятие конвейера в структуре процессора. Операционное устройство содержит группу регистров общего назначения (РОН) , арифметико-логическое устройство (АЛУ), основу которого составляет комбинированный 16-разрядный сумматор с последовательно-параллельным переносом, регистр флажков и несколько регистров для временного хранения операндов и результата операции. Оно выполняет команды, обменивается данными и адресами с шинным интерфейсом, оперирует общими регистрами и флажками. В его составе имеется блок микропрограммного управления, который дешифрует команды и формирует необходимые управляющие сигналы. Операционное устройство изолированно от внешней шины, за исключением нескольких внешних сигналов.

Шинный интерфейс выполняет для операционного устройства все операции обмена. Данные передаются между процессором и памятью или портами ввода-вывода по запросам операционного устройства. Когда операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует опережающую выборку из памяти очередных команд. Команды хранятся во внутренней регистровой памяти, называемой очередью (буфером) команд. Очередь команд выполняет по существу функции регистра команды процессора. Длина очереди составляет 6 байт. Очередь команд работает по принципу FIFO ("первым пришел, первым вышел"), который сохраняет на выходе порядок поступления команд. Шинный интерфейс инициирует выборку из памяти следующего командного слова, когда в очереди оказываются два свободных (пустых) байта. В большинстве случаев очередь команд содержит минимум один байт потока команд, и операционное устройство не ожидает выборки команды. Конечно, очередь обеспечивает положительный эффект при естественном порядке выполнения команд. Когда операционное устройство выполняет команду передачи управления, шинный интерфейс сбрасывает очередь, выбирает команду по новому адресу, передает

ее в операционное устройство, а затем начинает заполнение очереди из следующих ячеек. Эти действия выполняются при условных и безусловных переходах, вызовах подпрограмм, возвратах из подпрограмм и при обработке прерываний. Шинный интерфейс приостанавливает выборку команд, когда операционное устройство запрашивает операцию считывания или записи в память или порт ввода-вывода. В состав шинного интерфейса входят несколько регистров и сумматор, которые формируют 20-разрядный физический адрес памяти из двух 16-разрядных логических адресов: сегмента (базы) и смещения.

При готовности операционного устройства выполнять команду оно считывает из очереди байт, а затем выполняет предписанную командой операцию. При многобайтных командах из очереди считываются и другие байты команды. Когда операционное устройство готово считать командный байт, а очередь команд пуста, оно ожидает выборки командного слова из памяти программ, которую производит шинный интерфейс. Если команда требует обращения к памяти или порту ввода-вывода, операционное устройство запрашивает шинный интерфейс на выполнение необходимого цикла шины. Когда шинный интерфейс не занят выборкой команды, он удовлетворяет запрос немедленно; в противном случае операционное устройство ожидает завершения текущего цикла шин

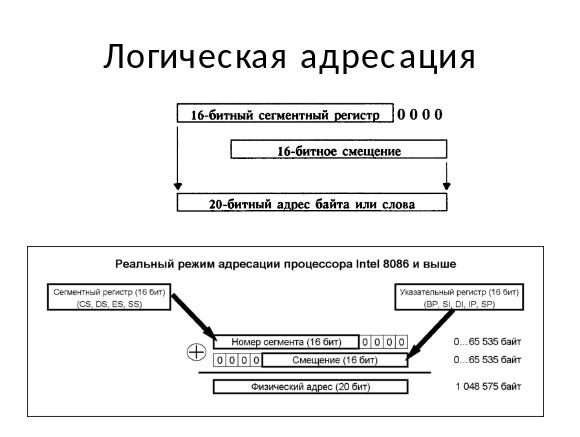

Использование шинного интерфейса привело к появлению логической адерсации , которая основана на использовании крупных областей памяти, называемых сегментами. Логический адрес операнда представляет собой шестнадцатиразрядный указатель на операнд внутри сегмента (смещение) и шестнадцатиразрядный адрес сегмента(база сегмента) (см рис.2)

Рисунок 2. Логический адрес операнда

На основании процессора 8986 была разработана программная модель процессора 8086. Программная модель процессора - это функциональная модель, используемая программистом при разработке программ в кодах ЭВМ или на языке ассемблера. В такой модели игнорируются многие аппаратные особенности в работе процессора.

К важнейшим ресурсам микропроцессора относятся регистры. Регистры разбиваются на четыре категории: регистры общего назначения, регистр флагов, указатель команд и сегментные регистры. Все регистры 16-разрядные.